### Renesas Electronics America Inc - R5F101PJDFB#V0 Datasheet

Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | RL78                                                                            |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 32MHz                                                                           |

| Connectivity               | CSI, I <sup>2</sup> C, LINbus, UART/USART                                       |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                                         |

| Number of I/O              | 82                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 20K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 1.6V ~ 5.5V                                                                     |

| Data Converters            | A/D 20x8/10b                                                                    |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-LQFP                                                                        |

| Supplier Device Package    | 100-LQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/renesas-electronics-america/r5f101pjdfb-v0 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

RL78/G13 1. OUTLINE

Table 1-1. List of Ordering Part Numbers

(6/12)

| Pin count | Package                 | Data flash | Fields of<br>Application | Ordering Part Number                            |

|-----------|-------------------------|------------|--------------------------|-------------------------------------------------|

| 48 pins   | 48-pin plastic          | Mounted    | А                        | R5F100GAANA#U0, R5F100GCANA#U0, R5F100GDANA#U0, |

|           | HWQFN (7 $\times$ 7 mm, |            |                          | R5F100GEANA#U0, R5F100GFANA#U0, R5F100GGANA#U0, |

|           | 0.5 mm pitch)           |            |                          | R5F100GHANA#U0, R5F100GJANA#U0, R5F100GKANA#U0, |

|           |                         |            |                          | R5F100GLANA#U0                                  |

|           |                         |            |                          | R5F100GAANA#W0, R5F100GCANA#W0,                 |

|           |                         |            |                          | R5F100GDANA#W0, R5F100GEANA#W0,                 |

|           |                         |            |                          | R5F100GFANA#W0, R5F100GGANA#W0,                 |

|           |                         |            |                          | R5F100GHANA#W0, R5F100GJANA#W0,                 |

|           |                         |            |                          | R5F100GKANA#W0, R5F100GLANA#W0                  |

|           |                         |            | D                        | R5F100GADNA#U0, R5F100GCDNA#U0, R5F100GDDNA#U0, |

|           |                         |            |                          | R5F100GEDNA#U0, R5F100GFDNA#U0, R5F100GGDNA#U0, |

|           |                         |            |                          | R5F100GHDNA#U0, R5F100GJDNA#U0, R5F100GKDNA#U0, |

|           |                         |            |                          | R5F100GLDNA#U0                                  |

|           |                         |            |                          | R5F100GADNA#W0, R5F100GCDNA#W0,                 |

|           |                         |            |                          | R5F100GDDNA#W0, R5F100GEDNA#W0,                 |

|           |                         |            |                          | R5F100GFDNA#W0, R5F100GGDNA#W0,                 |

|           |                         |            |                          | R5F100GHDNA#W0, R5F100GJDNA#W0,                 |

|           |                         |            |                          | R5F100GKDNA#W0, R5F100GLDNA#W0                  |

|           |                         |            | G                        | R5F100GAGNA#U0, R5F100GCGNA#U0, R5F100GDGNA#U0, |

|           |                         |            |                          | R5F100GEGNA#U0, R5F100GFGNA#U0, R5F100GGGNA#U0, |

|           |                         |            |                          | R5F100GHGNA#U0, R5F100GJGNA#U0                  |

|           |                         |            |                          | R5F100GAGNA#W0, R5F100GCGNA#W0,                 |

|           |                         |            |                          | R5F100GDGNA#W0, R5F100GEGNA#W0,                 |

|           |                         |            |                          | R5F100GFGNA#W0, R5F100GGGNA#W0,                 |

|           |                         |            |                          | R5F100GHGNA#W0, R5F100GJGNA#W0                  |

|           |                         | Not        | Α                        | R5F101GAANA#U0, R5F101GCANA#U0, R5F101GDANA#U0, |

|           |                         | mounted    |                          | R5F101GEANA#U0, R5F101GFANA#U0, R5F101GGANA#U0, |

|           |                         |            |                          | R5F101GHANA#U0, R5F101GJANA#U0, R5F101GKANA#U0, |

|           |                         |            |                          | R5F101GLANA#U0                                  |

|           |                         |            |                          | R5F101GAANA#W0, R5F101GCANA#W0,                 |

|           |                         |            |                          | R5F101GDANA#W0, R5F101GEANA#W0,                 |

|           |                         |            |                          | R5F101GFANA#W0, R5F101GGANA#W0,                 |

|           |                         |            |                          | R5F101GHANA#W0, R5F101GJANA#W0,                 |

|           |                         |            |                          | R5F101GKANA#W0, R5F101GLANA#W0                  |

|           |                         |            | D                        | R5F101GADNA#U0, R5F101GCDNA#U0, R5F101GDDNA#U0, |

|           |                         |            |                          | R5F101GEDNA#U0, R5F101GFDNA#U0, R5F101GGDNA#U0, |

|           |                         |            |                          | R5F101GHDNA#U0, R5F101GJDNA#U0, R5F101GKDNA#U0, |

|           |                         |            |                          | R5F101GLDNA#U0                                  |

|           |                         |            |                          | R5F101GADNA#W0, R5F101GCDNA#W0,                 |

|           |                         |            |                          | R5F101GDDNA#W0, R5F101GEDNA#W0,                 |

|           |                         |            |                          | R5F101GFDNA#W0, R5F101GGDNA#W0,                 |

|           |                         |            |                          | R5F101GHDNA#W0, R5F101GJDNA#W0,                 |

|           |                         |            |                          | R5F101GKDNA#W0, R5F101GLDNA#W0                  |

Note For the fields of application, refer to Figure 1-1 Part Number, Memory Size, and Package of RL78/G13.

Caution The ordering part numbers represent the numbers at the time of publication. For the latest ordering part numbers, refer to the target product page of the Renesas Electronics website.

RL78/G13 1. OUTLINE

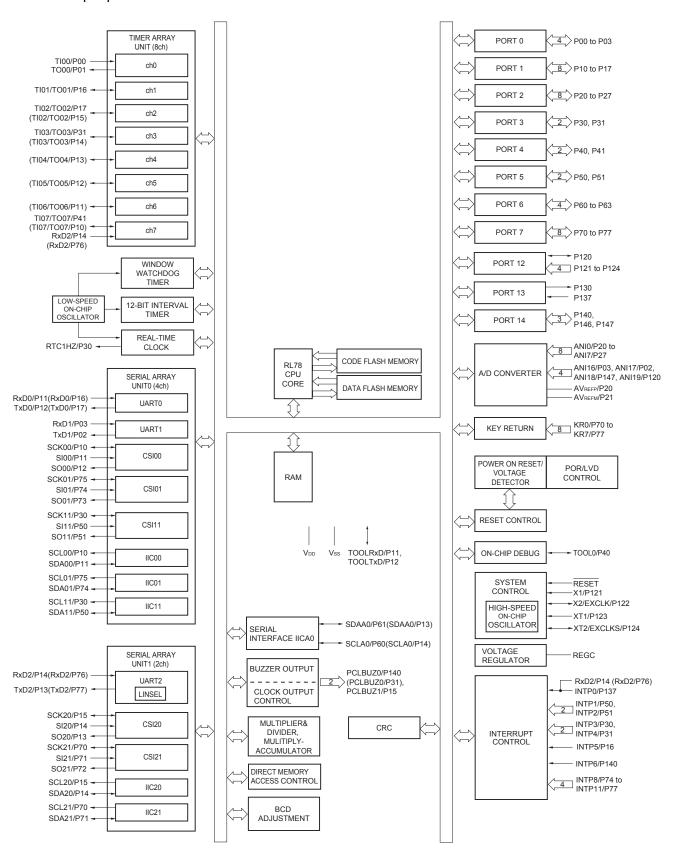

### 1.5.10 52-pin products

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR) in the RL78/G13 User's Manual.

RL78/G13 1. OUTLINE

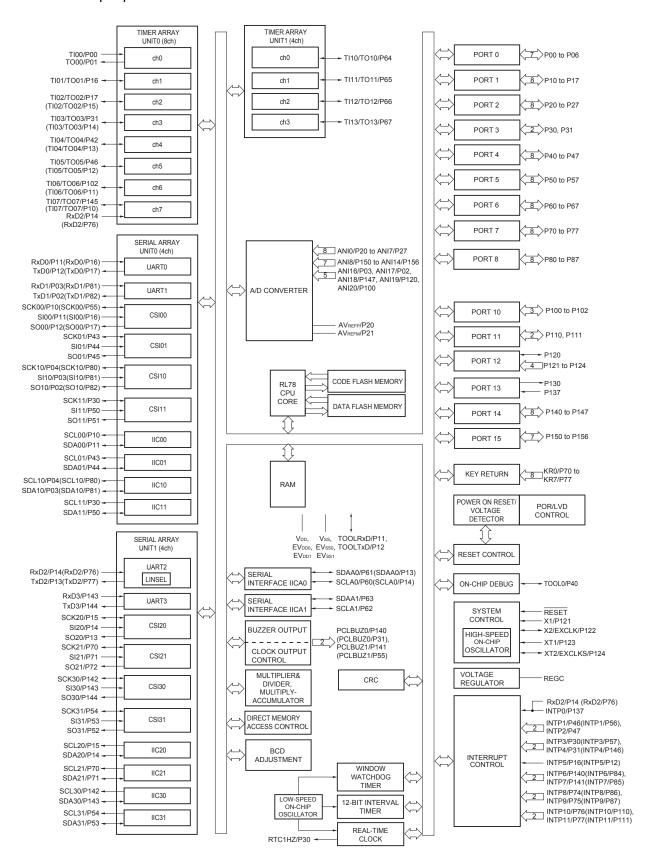

### 1.5.13 100-pin products

Remark Functions in parentheses in the above figure can be assigned via settings in the peripheral I/O redirection register (PIOR). Refer to Figure 4-8 Format of Peripheral I/O Redirection Register (PIOR) in the RL78/G13 User's Manual.

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.6 \text{ V} \le \text{EV}_{DD0} = \text{EV}_{DD1} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{Vss} = \text{EV}_{SS0} = \text{EV}_{SS1} = 0 \text{ V})$  (3/5)

| Items                  | Symbol           | Conditions                                                                                                                                                               |                                                                              | MIN.                 | TYP. | MAX.                 | Unit |

|------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------|------|----------------------|------|

| Input voltage,<br>high | V <sub>IH1</sub> | P00 to P07, P10 to P17, P30 to P37, P40 to P47, P50 to P57, P64 to P67, P70 to P77, P80 to P87, P90 to P97, P100 to P106, P110 to P117, P120, P125 to P127, P140 to P147 |                                                                              | 0.8EV <sub>DD0</sub> |      | EV <sub>DD0</sub>    | V    |

|                        | V <sub>IH2</sub> | P01, P03, P04, P10, P11,<br>P13 to P17, P43, P44, P53 to P55,                                                                                                            | TTL input buffer 4.0 V ≤ EV <sub>DD0</sub> ≤ 5.5 V                           | 2.2                  |      | EV <sub>DD0</sub>    | V    |

|                        |                  | P80, P81, P142, P143                                                                                                                                                     | TTL input buffer $3.3 \text{ V} \leq \text{EV}_{\text{DD0}} < 4.0 \text{ V}$ | 2.0                  |      | EV <sub>DD0</sub>    | V    |

|                        |                  |                                                                                                                                                                          | TTL input buffer 1.6 V ≤ EV <sub>DD0</sub> < 3.3 V                           | 1.5                  |      | EV <sub>DD0</sub>    | V    |

|                        | V <sub>IH3</sub> | P20 to P27, P150 to P156                                                                                                                                                 |                                                                              | 0.7V <sub>DD</sub>   |      | V <sub>DD</sub>      | ٧    |

|                        | V <sub>IH4</sub> | P60 to P63                                                                                                                                                               |                                                                              | 0.7EV <sub>DD0</sub> |      | 6.0                  | ٧    |

|                        | V <sub>IH5</sub> | P121 to P124, P137, EXCLK, EXCL                                                                                                                                          | KS, RESET                                                                    | 0.8V <sub>DD</sub>   |      | V <sub>DD</sub>      | ٧    |

| Input voltage,<br>low  | V <sub>IL1</sub> | P00 to P07, P10 to P17, P30 to P37, P40 to P47, P50 to P57, P64 to P67, P70 to P77, P80 to P87, P90 to P97, P100 to P106, P110 to P117, P120, P125 to P127, P140 to P147 | ,                                                                            | 0                    |      | 0.2EV <sub>DD0</sub> | V    |

|                        | V <sub>IL2</sub> | P01, P03, P04, P10, P11,<br>P13 to P17, P43, P44, P53 to P55,                                                                                                            | TTL input buffer 4.0 V ≤ EV <sub>DD0</sub> ≤ 5.5 V                           | 0                    |      | 0.8                  | V    |

|                        |                  | P80, P81, P142, P143                                                                                                                                                     | TTL input buffer 3.3 V ≤ EV <sub>DD0</sub> < 4.0 V                           | 0                    |      | 0.5                  | V    |

|                        |                  |                                                                                                                                                                          | TTL input buffer 1.6 V ≤ EV <sub>DD0</sub> < 3.3 V                           | 0                    |      | 0.32                 | V    |

|                        | VIL3             | P20 to P27, P150 to P156                                                                                                                                                 |                                                                              | 0                    |      | 0.3V <sub>DD</sub>   | ٧    |

|                        | V <sub>IL4</sub> | P60 to P63                                                                                                                                                               |                                                                              | 0                    |      | 0.3EV <sub>DD0</sub> | ٧    |

|                        | V <sub>IL5</sub> | P121 to P124, P137, EXCLK, EXCL                                                                                                                                          | KS, RESET                                                                    | 0                    |      | 0.2V <sub>DD</sub>   | ٧    |

Caution The maximum value of V<sub>IH</sub> of pins P00, P02 to P04, P10 to P15, P17, P43 to P45, P50, P52 to P55, P71, P74, P80 to P82, P96, and P142 to P144 is EV<sub>DD0</sub>, even in the N-ch open-drain mode.

**Remark** Unless specified otherwise, the characteristics of alternate-function pins are the same as those of the port pins.

### (5) During communication at same potential (simplified I<sup>2</sup>C mode) (2/2)

(Ta = -40 to +85°C, 1.6 V  $\leq$  EVDD0 = EVDD1  $\leq$  VDD  $\leq$  5.5 V, Vss = EVss0 = EVss1 = 0 V)

| Parameter                     | Symbol  | Conditions                                                                                                  | , ,                                             | h-speed<br>Mode | ,                                               | r-speed<br>Mode | `                                               | -voltage<br>Mode | Unit |

|-------------------------------|---------|-------------------------------------------------------------------------------------------------------------|-------------------------------------------------|-----------------|-------------------------------------------------|-----------------|-------------------------------------------------|------------------|------|

|                               |         |                                                                                                             | MIN.                                            | MAX.            | MIN.                                            | MAX.            | MIN.                                            | MAX.             |      |

| Data setup time (reception)   | tsu:dat | $2.7~V \leq EV_{DD0} \leq 5.5~V,$ $C_b = 50~pF,~R_b = 2.7~k\Omega$                                          | 1/f <sub>MCK</sub><br>+ 85<br><sub>Note2</sub>  |                 | 1/fmck<br>+ 145<br>Note2                        |                 | 1/f <sub>MCK</sub><br>+ 145<br><sub>Note2</sub> |                  | ns   |

|                               |         | $1.8~V \leq EV_{DD0} \leq 5.5~V,$ $C_b = 100~pF,~R_b = 3~k\Omega$                                           | 1/f <sub>MCK</sub><br>+ 145<br><sub>Note2</sub> |                 | 1/f <sub>MCK</sub><br>+ 145<br><sub>Note2</sub> |                 | 1/f <sub>MCK</sub><br>+ 145<br><sub>Note2</sub> |                  | ns   |

|                               |         | $1.8~V \leq EV_{DD0} < 2.7~V,$ $C_b = 100~pF,~R_b = 5~k\Omega$                                              | 1/fmck<br>+ 230<br>Note2                        |                 | 1/fmck<br>+ 230<br>Note2                        |                 | 1/fmck<br>+ 230<br>Note2                        |                  | ns   |

|                               |         | $1.7~V \leq EV_{DD0} < 1.8~V,$ $C_b = 100~pF,~R_b = 5~k\Omega$                                              | 1/fmck<br>+ 290<br>Note2                        |                 | 1/fmck<br>+ 290<br>Note2                        |                 | 1/fmck<br>+ 290<br>Note2                        |                  | ns   |

|                               |         | $1.6~V \leq EV_{DD0} < 1.8~V,$ $C_b = 100~pF,~R_b = 5~k\Omega$                                              | _                                               |                 | 1/fmck<br>+ 290<br>Note2                        |                 | 1/fmck<br>+ 290<br>Note2                        |                  | ns   |

| Data hold time (transmission) | thd:dat | $2.7~V \leq EV_{DD0} \leq 5.5~V,$ $C_b = 50~pF,~R_b = 2.7~k\Omega$                                          | 0                                               | 305             | 0                                               | 305             | 0                                               | 305              | ns   |

|                               |         | $1.8~V \leq EV_{DD0} \leq 5.5~V,$ $C_b = 100~pF,~R_b = 3~k\Omega$                                           | 0                                               | 355             | 0                                               | 355             | 0                                               | 355              | ns   |

|                               |         | $1.8~V \leq EV_{DD0} < 2.7~V,$ $C_b = 100~pF,~R_b = 5~k\Omega$                                              | 0                                               | 405             | 0                                               | 405             | 0                                               | 405              | ns   |

|                               |         | $1.7 \text{ V} \le \text{EV}_{\text{DD0}} < 1.8 \text{ V},$ $C_b = 100 \text{ pF}, R_b = 5 \text{ k}\Omega$ | 0                                               | 405             | 0                                               | 405             | 0                                               | 405              | ns   |

|                               |         | $1.6~V \leq EV_{DD0} < 1.8~V,$ $C_b = 100~pF,~R_b = 5~k\Omega$                                              | _                                               | _               | 0                                               | 405             | 0                                               | 405              | ns   |

Notes 1. The value must also be equal to or less than fmck/4.

2. Set the fmck value to keep the hold time of SCLr = "L" and SCLr = "H".

Caution Select the normal input buffer and the N-ch open drain output (Vpb tolerance (When 20- to 52-pin products)/EVpb tolerance (When 64- to 128-pin products)) mode for the SDAr pin and the normal output mode for the SCLr pin by using port input mode register g (PIMg) and port output mode register h (POMh).

(Remarks are listed on the next page.)

### (6) Communication at different potential (1.8 V, 2.5 V, 3 V) (UART mode) (2/2)

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{EV}_{DD0} = \text{EV}_{DD1} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{Vss} = \text{EV}_{SS0} = \text{EV}_{SS1} = 0 \text{ V})$

| Parameter     | Symbol | Conditions                                                                                                                 |                                                                  | HS (          | high-          | LS (          | low-           |               | low-<br>age<br>Mode | Unit |

|---------------|--------|----------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|---------------|----------------|---------------|----------------|---------------|---------------------|------|

|               |        |                                                                                                                            |                                                                  | MIN.          | MAX.           | MIN.          | MAX.           | MIN.          | MAX.                |      |

| Transfer rate |        | $4.0 \text{ V} \le \text{EV}_{\text{DD0}} \le 5.5 \text{ V},$<br>$2.7 \text{ V} \le \text{V}_{\text{b}} \le 4.0 \text{ V}$ |                                                                  |               | Note<br>1      |               | Note<br>1      |               | Note<br>1           | bps  |

|               |        | Theoretical value of the maximum transfer rate $C_b = 50 \text{ pF}, R_b = 1.4 \text{ k}\Omega, V_b = 2.7 \text{ V}$       |                                                                  | 2.8<br>Note 2 |                | 2.8<br>Note 2 |                | 2.8<br>Note 2 | Mbps                |      |

|               |        | $2.7 \text{ V} \le \text{EV}_{\text{DD0}} < 4.0 \text{ V},$ $2.3 \text{ V} \le \text{V}_{\text{b}} \le 2.7 \text{ V}$      |                                                                  |               | Note<br>3      |               | Note<br>3      |               | Note<br>3           | bps  |

|               |        | 2.3 V ≤ Vb ≤ 2.7 V                                                                                                         | Theoretical value of the maximum transfer rate  Cb = 50 pF, Rb = |               | 1.2<br>Note 4  |               | 1.2<br>Note 4  |               | 1.2<br>Note 4       | Mbps |

|               |        |                                                                                                                            | $2.7 \text{ k}\Omega, V_b = 2.3$                                 |               |                |               |                |               |                     |      |

|               |        | $1.8 \ V \le EV_{DD0} < 3.3 \ V,$ $1.6 \ V \le V_b \le 2.0 \ V$                                                            |                                                                  |               | Notes<br>5, 6  |               | Notes<br>5, 6  |               | Notes<br>5, 6       | bps  |

|               |        |                                                                                                                            | Theoretical value of the maximum transfer rate                   |               | 0.43<br>Note 7 |               | 0.43<br>Note 7 |               | 0.43<br>Note 7      | Mbps |

|               |        | $C_b = 50 \text{ pF}, R_b = 5.5 \text{ k}\Omega, V_b = 1.6 \text{ V}$                                                      |                                                                  |               |                |               |                |               |                     |      |

**Notes 1.** The smaller maximum transfer rate derived by using fmck/6 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 4.0 V  $\leq$  EV  $_{DD0} \leq$  5.5 V and 2.7 V  $\leq$  V  $_{b} \leq$  4.0 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{2.2}{V_b})\} \times 3}$$

[bps]

$$\text{Baud rate error (theoretical value)} = \frac{\frac{1}{\text{Transfer rate} \times 2} - \{-C_b \times R_b \times \ln{(1 - \frac{2.2}{V_b})}\}}{\frac{1}{(\text{Transfer rate})} \times \text{Number of transferred bits}} \times 100 \, [\%]$$

- \* This value is the theoretical value of the relative difference between the transmission and reception sides.

- 2. This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to Note 1 above to calculate the maximum transfer rate under conditions of the customer.

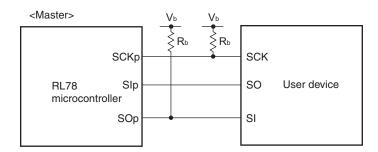

### CSI mode connection diagram (during communication at different potential)

- **Remarks 1.** R<sub>b</sub>[Ω]:Communication line (SCKp, SOp) pull-up resistance, C<sub>b</sub>[F]: Communication line (SCKp, SOp) load capacitance, V<sub>b</sub>[V]: Communication line voltage

- **2.** p: CSI number (p = 00, 01, 10, 20, 30, 31), m: Unit number , n: Channel number (mn = 00, 01, 02, 10, 12, 13), g: PIM and POM number (g = 0, 1, 4, 5, 8, 14)

- 3. fmck: Serial array unit operation clock frequency (Operation clock to be set by the CKSmn bit of serial mode register mn (SMRmn). m: Unit number, n: Channel number (mn = 00))

- **4.** CSI01 of 48-, 52-, 64-pin products, and CSI11 and CSI21 cannot communicate at different potential. Use other CSI for communication at different potential.

### 2.6 Analog Characteristics

### 2.6.1 A/D converter characteristics

Classification of A/D converter characteristics

|                            |                                | Reference Voltage           |                                          |

|----------------------------|--------------------------------|-----------------------------|------------------------------------------|

|                            | Reference voltage (+) = AVREFP | Reference voltage (+) = VDD | Reference voltage (+) = V <sub>BGR</sub> |

| Input channel              | Reference voltage (-) = AVREFM | Reference voltage (-) = Vss | Reference voltage (–) = AVREFM           |

| ANI0 to ANI14              | Refer to <b>2.6.1 (1)</b> .    | Refer to <b>2.6.1 (3)</b> . | Refer to <b>2.6.1 (4)</b> .              |

| ANI16 to ANI26             | Refer to <b>2.6.1 (2)</b> .    |                             |                                          |

| Internal reference voltage | Refer to <b>2.6.1 (1)</b> .    |                             | _                                        |

| Temperature sensor output  |                                |                             |                                          |

| voltage                    |                                |                             |                                          |

(1) When reference voltage (+)= AVREFP/ANI0 (ADREFP1 = 0, ADREFP0 = 1), reference voltage (-) = AVREFM/ANI1 (ADREFM = 1), target pin : ANI2 to ANI14, internal reference voltage, and temperature sensor output voltage

(TA = -40 to +85°C, 1.6 V  $\leq$  AVREFP  $\leq$  VDD  $\leq$  5.5 V, Vss = 0 V, Reference voltage (+) = AVREFP, Reference voltage (-) = AVREFM = 0 V)

| Parameter                                  | Symbol | Con                                                                                              | ditions                                                  | MIN.                       | TYP.                    | MAX.   | Unit |

|--------------------------------------------|--------|--------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------|-------------------------|--------|------|

| Resolution                                 | RES    |                                                                                                  |                                                          | 8                          |                         | 10     | bit  |

| Overall error <sup>Note 1</sup>            | AINL   | 10-bit resolution                                                                                | 1.8 V ≤ AV <sub>REFP</sub> ≤ 5.5 V                       |                            | 1.2                     | ±3.5   | LSB  |

|                                            |        | $AV_{REFP} = V_{DD}^{Note 3}$                                                                    | $1.6~V \leq AV_{REFP} \leq 5.5~V^{\text{Note 4}}$        |                            | 1.2                     | ±7.0   | LSB  |

| Conversion time                            | tconv  | 10-bit resolution                                                                                | $3.6~V \leq V_{DD} \leq 5.5~V$                           | 2.125                      |                         | 39     | μS   |

|                                            |        | Target pin: ANI2 to<br>ANI14                                                                     | $2.7~V \leq V_{DD} \leq 5.5~V$                           | 3.1875                     |                         | 39     | μS   |

|                                            |        |                                                                                                  | $1.8~V \leq V_{DD} \leq 5.5~V$                           | 17                         |                         | 39     | μS   |

|                                            |        |                                                                                                  | $1.6~V \leq V_{DD} \leq 5.5~V$                           | 57                         |                         | 95     | μS   |

|                                            |        | 10-bit resolution                                                                                | $3.6~V \leq V_{DD} \leq 5.5~V$                           | 2.375                      |                         | 39     | μS   |

|                                            |        | Target pin: Internal                                                                             | $2.7~V \leq V_{DD} \leq 5.5~V$                           | 3.5625                     |                         | 39     | μS   |

|                                            |        | reference voltage, and<br>temperature sensor<br>output voltage<br>(HS (high-speed main)<br>mode) | $2.4~V \leq V_{DD} \leq 5.5~V$                           | 17                         |                         | 39     | μs   |

| Zero-scale error <sup>Notes 1, 2</sup>     | Ezs    | 10-bit resolution                                                                                | 1.8 V ≤ AV <sub>REFP</sub> ≤ 5.5 V                       |                            |                         | ±0.25  | %FSR |

|                                            |        | $AV_{REFP} = V_{DD}^{Note 3}$                                                                    | $1.6~V \leq AV_{\text{REFP}} \leq 5.5~V^{\text{Note 4}}$ |                            |                         | ±0.50  | %FSR |

| Full-scale error Notes 1, 2                | Ers    | 10-bit resolution                                                                                | $1.8~V \leq AV_{REFP} \leq 5.5~V$                        |                            |                         | ±0.25  | %FSR |

|                                            |        | $AV_{REFP} = V_{DD}^{Note 3}$                                                                    | $1.6~V \leq AV_{REFP} \leq 5.5~V^{\text{Note 4}}$        |                            |                         | ±0.50  | %FSR |

| Integral linearity error <sup>Note 1</sup> | ILE    | 10-bit resolution                                                                                | $1.8~V \leq AV_{REFP} \leq 5.5~V$                        |                            |                         | ±2.5   | LSB  |

|                                            |        | $AV_{REFP} = V_{DD}^{Note 3}$                                                                    | $1.6~V \leq AV_{\text{REFP}} \leq 5.5~V^{\text{Note 4}}$ |                            |                         | ±5.0   | LSB  |

| Differential linearity error Note 1        | DLE    | 10-bit resolution                                                                                | $1.8~V \leq AV_{REFP} \leq 5.5~V$                        |                            |                         | ±1.5   | LSB  |

|                                            |        | $AV_{REFP} = V_{DD}^{Note 3}$                                                                    | $1.6~V \leq AV_{\text{REFP}} \leq 5.5~V^{\text{Note 4}}$ |                            |                         | ±2.0   | LSB  |

| Analog input voltage                       | VAIN   | ANI2 to ANI14                                                                                    |                                                          | 0                          |                         | AVREFP | V    |

|                                            |        | Internal reference voltage (2.4 V ≤ VDD ≤ 5.5 V, HS (high-speed main) mode)                      |                                                          |                            | V <sub>BGR</sub> Note 5 |        | V    |

|                                            |        | Temperature sensor outp (2.4 V $\leq$ VDD $\leq$ 5.5 V, HS                                       | •                                                        | V <sub>TMPS25</sub> Note 5 |                         |        | V    |

(Notes are listed on the next page.)

(2) When reference voltage (+) = AVREFP/ANIO (ADREFP1 = 0, ADREFP0 = 1), reference voltage (-) = AVREFM/ANI1 (ADREFM = 1), target pin : ANI16 to ANI26

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.6 \text{ V} \le \text{EV}_{\text{DD0}} = \text{EV}_{\text{DD1}} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, 1.6 \text{ V} \le \text{AV}_{\text{REFP}} \le \text{V}_{\text{DD}} \le 5.5 \text{ V}, \text{V}_{\text{SS}} = \text{EV}_{\text{SS0}} = \text{EV}_{\text{SS1}} = 0 \text{ V}, \text{Reference voltage (+)} = \text{AV}_{\text{REFM}} = 0 \text{ V})$

| Parameter                                | Symbol | Conditi                                              | ons                                              | MIN.   | TYP. | MAX.                | Unit |

|------------------------------------------|--------|------------------------------------------------------|--------------------------------------------------|--------|------|---------------------|------|

| Resolution                               | RES    |                                                      |                                                  | 8      |      | 10                  | bit  |

| Overall error <sup>Note 1</sup>          | AINL   | 10-bit resolution                                    | $1.8~V \leq AV_{REFP} \leq 5.5~V$                |        | 1.2  | ±5.0                | LSB  |

|                                          |        | EVDD0 = AVREFP = VDD Notes 3, 4                      | $1.6~V \leq AV_{REFP} \leq 5.5~V^{Note}$         |        | 1.2  | ±8.5                | LSB  |

| Conversion time                          | tconv  | 10-bit resolution                                    | $3.6~V \leq V_{DD} \leq 5.5~V$                   | 2.125  |      | 39                  | μS   |

|                                          |        | Target ANI pin : ANI16 to                            | $2.7~\text{V} \leq \text{Vdd} \leq 5.5~\text{V}$ | 3.1875 |      | 39                  | μS   |

|                                          |        | ANI26                                                | 1.8 V ≤ VDD ≤ 5.5 V                              | 17     |      | 39                  | μS   |

|                                          |        |                                                      | $1.6~V \leq V_{DD} \leq 5.5~V$                   | 57     |      | 95                  | μS   |

| Zero-scale error <sup>Notes 1, 2</sup>   | Ezs    | 10-bit resolution                                    | $1.8~V \leq AV_{REFP} \leq 5.5~V$                |        |      | ±0.35               | %FSR |

|                                          |        | EVDD0 = AVREFP = VDD Notes 3, 4                      | $1.6~V \leq AV_{REFP} \leq 5.5~V^{Note}$         |        |      | ±0.60               | %FSR |

| Full-scale error <sup>Notes 1, 2</sup>   | Ers    | 10-bit resolution<br>EVDD0 = AVREFP = VDD Notes 3, 4 | 1.8 V ≤ AV <sub>REFP</sub> ≤ 5.5 V               |        |      | ±0.35               | %FSR |

|                                          |        |                                                      | $1.6~V \le AV_{REFP} \le 5.5~V^{Note}$           |        |      | ±0.60               | %FSR |

| Integral linearity error <sup>Note</sup> | ILE    | 10-bit resolution                                    | 1.8 V ≤ AV <sub>REFP</sub> ≤ 5.5 V               |        |      | ±3.5                | LSB  |

| 1                                        |        | EVDD0 = AVREFP = VDD Notes 3, 4                      | $1.6~V \le AV_{REFP} \le 5.5~V^{Note}$           |        |      | ±6.0                | LSB  |

| Differential linearity                   | DLE    | 10-bit resolution                                    | 1.8 V ≤ AV <sub>REFP</sub> ≤ 5.5 V               |        |      | ±2.0                | LSB  |

| error <sup>Note 1</sup>                  |        | EVDD0 = AVREFP = VDD Notes 3, 4                      | $1.6~V \le AV_{REFP} \le 5.5~V^{Note}$           |        |      | ±2.5                | LSB  |

| Analog input voltage                     | VAIN   | ANI16 to ANI26                                       | ,                                                | 0      |      | AVREFP<br>and EVDD0 | V    |

- **Notes 1.** Excludes quantization error (±1/2 LSB).

- 2. This value is indicated as a ratio (%FSR) to the full-scale value.

- **3.** When  $AV_{REFP} < V_{DD}$ , the MAX. values are as follows.

Overall error: Add  $\pm 1.0$  LSB to the MAX. value when AV<sub>REFP</sub> = V<sub>DD</sub>.

Zero-scale error/Full-scale error: Add  $\pm 0.05\%$  FSR to the MAX. value when AV<sub>REFP</sub> = V<sub>DD</sub>.

Integral linearity error/ Differential linearity error: Add ±0.5 LSB to the MAX. value when AVREFP = VDD.

- **4.** When  $AV_{REFP} < EV_{DD0} \le V_{DD}$ , the MAX. values are as follows.

- Overall error: Add  $\pm 4.0$  LSB to the MAX. value when AV<sub>REFP</sub> = V<sub>DD</sub>.

Zero-scale error/Full-scale error: Add  $\pm 0.20\%$  FSR to the MAX. value when AV<sub>REFP</sub> = V<sub>DD</sub>.

Integral linearity error/ Differential linearity error: Add ±2.0 LSB to the MAX. value when AVREFP = VDD.

5. When the conversion time is set to 57  $\mu s$  (min.) and 95  $\mu s$  (max.).

### 2.8 Flash Memory Programming Characteristics

$(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le V_{DD} \le 5.5 \text{ V}, \text{ Vss} = 0 \text{ V})$

| Parameter                               | Symbol | Conditions                          | MIN.    | TYP.      | MAX. | Unit  |

|-----------------------------------------|--------|-------------------------------------|---------|-----------|------|-------|

| CPU/peripheral hardware clock frequency | fclk   | $1.8~V \leq V \text{dd} \leq 5.5~V$ | 1       |           | 32   | MHz   |

| Number of code flash rewrites           | Cerwr  | Retained for 20 years TA = 85°C     | 1,000   |           |      | Times |

| Number of data flash rewrites           |        | Retained for 1 years TA = 25°C      |         | 1,000,000 |      |       |

|                                         |        | Retained for 5 years TA = 85°C      | 100,000 |           |      |       |

|                                         |        | Retained for 20 years TA = 85°C     | 10,000  |           |      |       |

**Notes 1.** 1 erase + 1 write after the erase is regarded as 1 rewrite.

The retaining years are until next rewrite after the rewrite.

- 2. When using flash memory programmer and Renesas Electronics self programming library

- **3.** These are the characteristics of the flash memory and the results obtained from reliability testing by Renesas Electronics Corporation.

### 2.9 Dedicated Flash Memory Programmer Communication (UART)

### $(T_A = -40 \text{ to } +85^{\circ}\text{C}, 1.8 \text{ V} \le \text{EV}_{DD0} = \text{EV}_{DD1} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{Vss} = \text{EV}_{SS0} = \text{EV}_{SS1} = 0 \text{ V})$

| Parameter     | Symbol | Conditions                | MIN.    | TYP. | MAX.      | Unit |

|---------------|--------|---------------------------|---------|------|-----------|------|

| Transfer rate |        | During serial programming | 115,200 | _    | 1,000,000 | bps  |

# (2) Flash ROM: 96 to 256 KB of 30- to 100-pin products (Ta = -40 to $+105^{\circ}$ C, 2.4 V $\leq$ EV<sub>DD0</sub> = EV<sub>DD1</sub> $\leq$ V<sub>DD</sub> $\leq$ 5.5 V, Vss = EV<sub>SS0</sub> = EV<sub>SS1</sub> = 0 V) (1/2)

| Parameter         | Symbol           |                            |                                            | Conditions                                 |                      |                         | MIN. | TYP. | MAX. | Unit |

|-------------------|------------------|----------------------------|--------------------------------------------|--------------------------------------------|----------------------|-------------------------|------|------|------|------|

| Supply            | I <sub>DD1</sub> | Operating                  | HS (high-                                  | fin = 32 MHz <sup>Note 3</sup>             | Basic                | V <sub>DD</sub> = 5.0 V |      | 2.3  |      | mA   |

| Current<br>Note 1 |                  | mode                       | speed main)<br>mode Note 5                 |                                            | operatio<br>n        | V <sub>DD</sub> = 3.0 V |      | 2.3  |      | mA   |

|                   |                  |                            |                                            |                                            | Normal               | V <sub>DD</sub> = 5.0 V |      | 5.2  | 9.2  | mA   |

|                   |                  |                            |                                            |                                            | operatio<br>n        | V <sub>DD</sub> = 3.0 V |      | 5.2  | 9.2  | mA   |

|                   |                  |                            |                                            | fin = 24 MHz <sup>Note 3</sup>             | Normal               | V <sub>DD</sub> = 5.0 V |      | 4.1  | 7.0  | mA   |

|                   |                  |                            |                                            |                                            | operatio<br>n        | V <sub>DD</sub> = 3.0 V |      | 4.1  | 7.0  | mA   |

|                   |                  |                            |                                            | fih = 16 MHz <sup>Note 3</sup>             | Normal               | V <sub>DD</sub> = 5.0 V |      | 3.0  | 5.0  | mA   |

|                   |                  |                            |                                            |                                            | operatio<br>n        | V <sub>DD</sub> = 3.0 V |      | 3.0  | 5.0  | mA   |

|                   |                  |                            | HS (high-                                  | $f_{MX} = 20 \text{ MHz}^{\text{Note 2}},$ | Normal               | Square wave input       |      | 3.4  | 5.9  | mA   |

|                   |                  | speed main)<br>mode Note 5 | V <sub>DD</sub> = 5.0 V                    | operatio<br>n                              | Resonator connection |                         | 3.6  | 6.0  | mA   |      |

|                   |                  |                            |                                            | $f_{MX} = 20 \text{ MHz}^{\text{Note 2}},$ | Normal               | Square wave input       |      | 3.4  | 5.9  | mA   |

|                   |                  |                            | V <sub>DD</sub> = 3.0 V                    | operatio<br>n                              | Resonator connection |                         | 3.6  | 6.0  | mA   |      |

|                   |                  |                            | $f_{MX} = 10 \text{ MHz}^{\text{Note 2}},$ | Normal operation                           | Square wave input    |                         | 2.1  | 3.5  | mA   |      |

|                   |                  |                            | V <sub>DD</sub> = 5.0 V                    |                                            | Resonator connection |                         | 2.1  | 3.5  | mA   |      |

|                   |                  |                            |                                            | $f_{MX} = 10 \text{ MHz}^{\text{Note 2}},$ | Normal               | Square wave input       |      | 2.1  | 3.5  | mA   |

|                   |                  |                            |                                            | V <sub>DD</sub> = 3.0 V                    | operatio<br>n        | Resonator connection    |      | 2.1  | 3.5  | mA   |

|                   |                  |                            | Subsystem clock operation                  | fsuв = 32.768 kHz                          | Normal operation     | Square wave input       |      | 4.8  | 5.9  | μА   |

|                   |                  |                            |                                            | Note 4 $T_A = -40^{\circ}C$                |                      | Resonator connection    |      | 4.9  | 6.0  | μΑ   |

|                   |                  |                            |                                            | fsuв = 32.768 kHz                          | Normal               | Square wave input       |      | 4.9  | 5.9  | μΑ   |

|                   |                  |                            |                                            | Note 4 $T_A = +25^{\circ}C$                | operatio<br>n        | Resonator connection    |      | 5.0  | 6.0  | μΑ   |

|                   |                  |                            |                                            | fsuв = 32.768 kHz                          | Normal               | Square wave input       |      | 5.0  | 7.6  | μΑ   |

|                   |                  |                            |                                            | Note 4 $T_A = +50^{\circ}C$                | operatio<br>n        | Resonator connection    |      | 5.1  | 7.7  | μΑ   |

|                   |                  |                            |                                            | fsuв = 32.768 kHz                          | Normal               | Square wave input       |      | 5.2  | 9.3  | μA   |

|                   |                  |                            |                                            | Note 4 $T_A = +70^{\circ}C$                | operatio<br>n        | Resonator connection    |      | 5.3  | 9.4  | μΑ   |

|                   |                  |                            |                                            | fsuB = 32.768 kHz                          | Normal               | Square wave input       |      | 5.7  | 13.3 | μΑ   |

|                   |                  |                            | Note 4  TA = +85°C                         | operatio<br>n                              | Resonator connection |                         | 5.8  | 13.4 | μΑ   |      |

|                   |                  |                            |                                            | fsuв = 32.768 kHz                          | Normal               | Square wave input       |      | 10.0 | 46.0 | μΑ   |

|                   |                  |                            | Note 4  TA = +105°C                        | operatio<br>n                              | Resonator connection |                         | 10.0 | 46.0 | μA   |      |

(Notes and Remarks are listed on the next page.)

- Notes 1. Total current flowing into VDD, EVDDO, and EVDD1, including the input leakage current flowing when the level of the input pin is fixed to VDD, EVDDO, and EVDD1, or Vss, EVSSO, and EVSS1. The values below the MAX. column include the peripheral operation current. However, not including the current flowing into the A/D converter, LVD circuit, I/O port, and on-chip pull-up/pull-down resistors and the current flowing during data flash rewrite.

- 2. During HALT instruction execution by flash memory.

- 3. When high-speed on-chip oscillator and subsystem clock are stopped.

- 4. When high-speed system clock and subsystem clock are stopped.

- **5.** When high-speed on-chip oscillator and high-speed system clock are stopped. When RTCLPC = 1 and setting ultra-low current consumption (AMPHS1 = 1). The current flowing into the RTC is included. However, not including the current flowing into the 12-bit interval timer and watchdog timer.

- 6. Not including the current flowing into the RTC, 12-bit interval timer, and watchdog timer.

- 7. Relationship between operation voltage width, operation frequency of CPU and operation mode is as below.

HS (high-speed main) mode:  $2.7 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V} @ 1 \text{ MHz}$  to 32 MHz  $2.4 \text{ V} \le \text{V}_{DD} \le 5.5 \text{ V} @ 1 \text{ MHz}$  to 16 MHz

- 8. Regarding the value for current operate the subsystem clock in STOP mode, refer to that in HALT mode.

- Remarks 1. fmx: High-speed system clock frequency (X1 clock oscillation frequency or external main system clock frequency)

- 2. fin: High-speed on-chip oscillator clock frequency

- 3. fsub: Subsystem clock frequency (XT1 clock oscillation frequency)

- **4.** Except subsystem clock operation and STOP mode, temperature condition of the TYP. value is  $T_A = 25^{\circ}C$

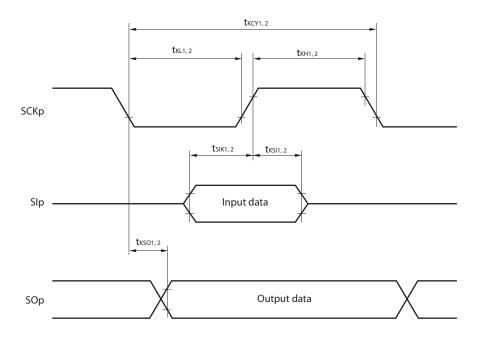

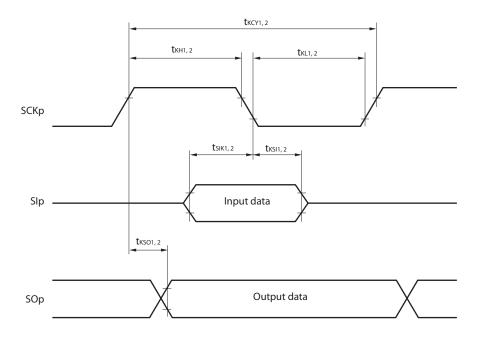

# CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.)

# CSI mode serial transfer timing (during communication at same potential) (When DAPmn = 0 and CKPmn = 1, or DAPmn = 1 and CKPmn = 0.)

**Remarks 1.** p: CSI number (p = 00, 01, 10, 11, 20, 21, 30, 31)

2. m: Unit number, n: Channel number (mn = 00 to 03, 10 to 13)

5. The smaller maximum transfer rate derived by using fmck/12 or the following expression is the valid maximum transfer rate.

Expression for calculating the transfer rate when 2.4 V  $\leq$  EV<sub>DD0</sub> < 3.3 V and 1.6 V  $\leq$  V<sub>b</sub>  $\leq$  2.0 V

Maximum transfer rate =

$$\frac{1}{\{-C_b \times R_b \times \ln (1 - \frac{1.5}{V_b})\} \times 3}$$

[bps]

Baud rate error (theoretical value) =

$$\frac{\frac{1}{\text{Transfer rate} \times 2} - \{-C_b \times R_b \times \ln{(1 - \frac{1.5}{V_b})}\}}{(\frac{1}{\text{Transfer rate}}) \times \text{Number of transferred bits}} \times 100 \, [\%]$$

- \* This value is the theoretical value of the relative difference between the transmission and reception sides.

- **6.** This value as an example is calculated when the conditions described in the "Conditions" column are met. Refer to Note 5 above to calculate the maximum transfer rate under conditions of the customer.

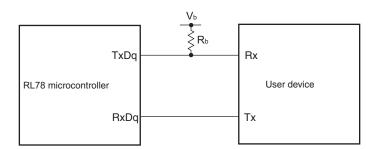

Caution Select the TTL input buffer for the RxDq pin and the N-ch open drain output (VDD tolerance (for the 20- to 52-pin products)/EVDD tolerance (for the 64- to 100-pin products)) mode for the TxDq pin by using port input mode register g (PIMg) and port output mode register g (POMg). For VIH and VIL, see the DC characteristics with TTL input buffer selected.

**UART** mode connection diagram (during communication at different potential)

## (6) Communication at different potential (1.8 V, 2.5 V, 3 V) (CSI mode) (master mode, SCKp... internal clock output) (2/3)

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{EV}_{DD0} = \text{EV}_{DD1} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{Vss} = \text{EV}_{SS0} = \text{EV}_{SS1} = 0 \text{ V})$

| Parameter                | Symbol | Conditions                                                                                                             | HS (high-spe | eed main) Mode | Unit |

|--------------------------|--------|------------------------------------------------------------------------------------------------------------------------|--------------|----------------|------|

|                          |        |                                                                                                                        | MIN.         | MAX.           |      |

| SIp setup time           | tsıĸı  | $4.0 \ V \leq EV_{DD0} \leq 5.5 \ V, \ 2.7 \ V \leq V_b \leq 4.0 \ V,$                                                 | 162          |                | ns   |

| (to SCKp↑) Note          |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}\Omega$                                                                       |              |                |      |

|                          |        | $2.7 \text{ V} \le \text{EV}_{\text{DD0}} < 4.0 \text{ V}, \ 2.3 \text{ V} \le \text{V}_{\text{b}} \le 2.7 \text{ V},$ | 354          |                | ns   |

|                          |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}\Omega$                                                                       |              |                |      |

|                          |        | $2.4 \ V \le EV_{DD0} < 3.3 \ V, \ 1.6 \ V \le V_b \le 2.0 \ V,$                                                       | 958          |                | ns   |

|                          |        | $C_b = 30 \text{ pF}, R_b = 5.5 \text{ k}\Omega$                                                                       |              |                |      |

| SIp hold time            | tksi1  | $4.0~V \leq EV_{\text{DD0}} \leq 5.5~V,~2.7~V \leq V_{\text{b}} \leq 4.0~V,$                                           | 38           |                | ns   |

| (from SCKp↑) Note        |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}\Omega$                                                                       |              |                |      |

|                          |        | $2.7 \; V \leq EV_{\text{DD0}} < 4.0 \; V, \; 2.3 \; V \leq V_{\text{b}} \leq 2.7 \; V,$                               | 38           |                | ns   |

|                          |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}\Omega$                                                                       |              |                |      |

|                          |        | $2.4~V \leq EV_{DD0} < 3.3~V,~1.6~V \leq V_b \leq 2.0~V,$                                                              | 38           |                | ns   |

|                          |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}\Omega$                                                                       |              |                |      |

| Delay time from SCKp↓ to | tkso1  | $4.0~V \leq EV_{\text{DD0}} \leq 5.5~V,~2.7~V \leq V_{\text{b}} \leq 4.0~V,$                                           |              | 200            | ns   |

| SOp output Note          |        | $C_b = 30 \text{ pF}, R_b = 1.4 \text{ k}\Omega$                                                                       |              |                |      |

|                          |        | $2.7 \; V \leq EV_{\text{DD0}} < 4.0 \; V, \; 2.3 \; V \leq V_{\text{b}} \leq 2.7 \; V,$                               |              | 390            | ns   |

|                          |        | $C_b = 30 \text{ pF}, R_b = 2.7 \text{ k}\Omega$                                                                       |              |                |      |

|                          |        | $2.4 \ V \le EV_{DD0} < 3.3 \ V, \ 1.6 \ V \le V_b \le 2.0 \ V,$                                                       | _            | 966            | ns   |

|                          |        | $C_b=30~pF,~R_b=5.5~k\Omega$                                                                                           |              |                |      |

**Note** When DAPmn = 0 and CKPmn = 0, or DAPmn = 1 and CKPmn = 1.

Caution Select the TTL input buffer for the SIp pin and the N-ch open drain output (V<sub>DD</sub> tolerance (for the 20- to 52-pin products)/EV<sub>DD</sub> tolerance (for the 64- to 100-pin products)) mode for the SOp pin and SCKp pin by using port input mode register g (PIMg) and port output mode register g (POMg). For V<sub>IH</sub> and V<sub>IL</sub>, see the DC characteristics with TTL input buffer selected.

(Remarks are listed on the page after the next page.)

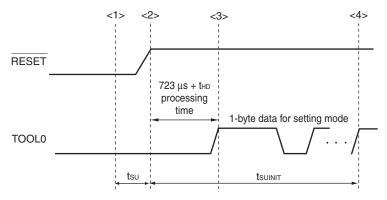

### 3.10 Timing of Entry to Flash Memory Programming Modes

$(T_A = -40 \text{ to } +105^{\circ}\text{C}, 2.4 \text{ V} \le \text{EV}_{DD0} = \text{EV}_{DD1} \le \text{V}_{DD} \le 5.5 \text{ V}, \text{Vss} = \text{EV}_{SS0} = \text{EV}_{SS1} = 0 \text{ V})$

| Parameter                                                                                                                                                    | Symbol  | Conditions                                                                | MIN. | TYP. | MAX. | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------------------------------------------------------------|------|------|------|------|

| Time to complete the communication for the initial setting after the external reset is released                                                              | tsuinit | POR and LVD reset must be released before the external reset is released. |      |      | 100  | ms   |

| Time to release the external reset after the TOOL0 pin is set to the low level                                                                               | tsu     | POR and LVD reset must be released before the external reset is released. | 10   |      |      | μS   |

| Time to hold the TOOL0 pin at the low level after the external reset is released (excluding the processing time of the firmware to control the flash memory) | tнo     | POR and LVD reset must be released before the external reset is released. | 1    |      |      | ms   |

- <1> The low level is input to the TOOL0 pin.

- <2> The external reset is released (POR and LVD reset must be released before the external reset is released.).

- <3> The TOOL0 pin is set to the high level.

- <4> Setting of the flash memory programming mode by UART reception and complete the baud rate setting.

**Remark** tsuinit: Communication for the initial setting must be completed within 100 ms after the external reset is released during this period.

tsu: Time to release the external reset after the TOOL0 pin is set to the low level

thd: Time to hold the TOOL0 pin at the low level after the external reset is released (excluding the processing time of the firmware to control the flash memory)

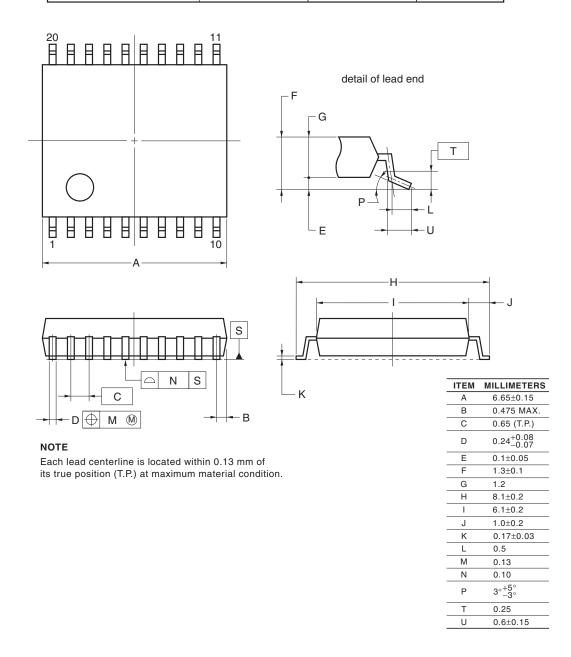

## 4. PACKAGE DRAWINGS

### 4.1 20-pin Products

R5F1006AASP, R5F1006CASP, R5F1006DASP, R5F1006EASP R5F1016AASP, R5F1016CASP, R5F1016DASP, R5F1016EASP R5F1006ADSP, R5F1006CDSP, R5F1006DDSP, R5F1006EDSP R5F1016ADSP, R5F1016CDSP, R5F1016DDSP, R5F1016EDSP R5F1006AGSP, R5F1006CGSP, R5F1006DGSP, R5F1006EGSP

| JEITA Package Code  | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|---------------------|--------------|----------------|-----------------|

| P-LSSOP20-0300-0.65 | PLSP0020JC-A | S20MC-65-5A4-3 | 0.12            |

© 2012 Renesas Electronics Corporation. All rights reserved.

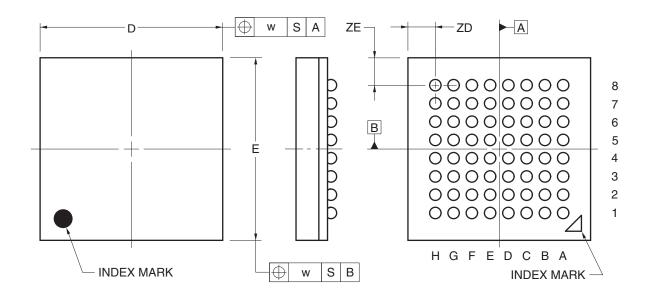

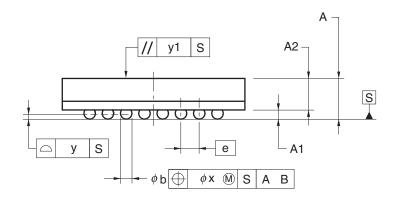

R5F100LCABG, R5F100LDABG, R5F100LEABG, R5F100LFABG, R5F100LGABG, R5F100LHABG, R5F100LJABG

R5F101LCABG, R5F101LDABG, R5F101LEABG, R5F101LFABG, R5F101LGABG, R5F101LHABG, R5F101LJABG

R5F100LCGBG, R5F100LDGBG, R5F100LEGBG, R5F100LFGBG, R5F100LGGBG, R5F100LHGBG, R5F100LJGBG

| JEITA Package Code | RENESAS Code | Previous Code  | MASS (TYP.) [g] |

|--------------------|--------------|----------------|-----------------|

| P-VFBGA64-4x4-0.40 | PVBG0064LA-A | P64F1-40-AA2-2 | 0.03            |

|      | (UNIT:mm)  |

|------|------------|

| ITEM | DIMENSIONS |

| D    | 4.00±0.10  |

| E    | 4.00±0.10  |

| w    | 0.15       |

| Α    | 0.89±0.10  |

| Α1   | 0.20±0.05  |

| A2   | 0.69       |

| е    | 0.40       |

| b    | 0.25±0.05  |

| х    | 0.05       |

| У    | 0.08       |

| y1   | 0.20       |

| ZD   | 0.60       |

| ZE   | 0.60       |

|      |            |

© 2012 Renesas Electronics Corporation. All rights reserved.

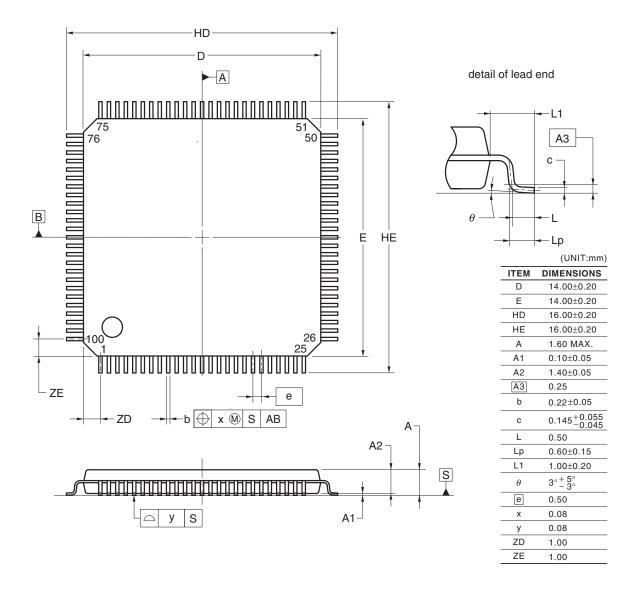

### 4.13 100-pin Products

R5F100PFAFB, R5F100PGAFB, R5F100PHAFB, R5F100PJAFB, R5F100PKAFB, R5F100PLAFB R5F101PFAFB, R5F101PGAFB, R5F101PHAFB, R5F101PJAFB, R5F101PKAFB, R5F101PLAFB R5F100PFDFB, R5F100PGDFB, R5F100PHDFB, R5F100PJDFB, R5F100PKDFB, R5F101PGDFB, R5F101PGDFB, R5F101PJDFB, R5F101PJDFB, R5F101PLDFB R5F100PFGFB, R5F100PGGFB, R5F100PHGFB, R5F100PJGFB

| JEITA Package Code    | RENESAS Code | Previous Code   | MASS (TYP.) [g] |

|-----------------------|--------------|-----------------|-----------------|

| P-LFQFP100-14x14-0.50 | PLQP0100KE-A | P100GC-50-GBR-1 | 0.69            |

©2012 Renesas Electronics Corporation. All rights reserved.

#### Notice

- Descriptions of circuits, software and other related information in this document are provided only to illustrate the operation of semiconductor products and application examples. You are fully responsible for the incorporation of these circuits, software, and information in the design of your equipment. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from the

- 2. Renesas Electronics has used reasonable care in preparing the information included in this document, but Renesas Electronics does not warrant that such information is error free. Renesas Electronics assumes no liability whatsoever for any damages incurred by you resulting from errors in or omissions from the information included herein.

- 3. Renesas Electronics does not assume any liability for infringement of patents, copyrights, or other intellectual property rights of third parties by or arising from the use of Renesas Electronics products or technical information described in this document. No license, express, implied or otherwise, is granted hereby under any patents, copyrights or other intellectual property rights of Renesas Electronics or

- 4. You should not alter, modify, copy, or otherwise misappropriate any Renesas Electronics product, whether in whole or in part. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties arising from such alteration, modification, copy or otherwise misappropriation of Renesas Electronics product.

- 5. Renesas Electronics products are classified according to the following two quality grades: "Standard" and "High Quality". The recommended applications for each Renesas Electronics product depends on the product's quality grade, as indicated below

"Standard": Computers: office equipment: communications equipment: test and measurement equipment: audio and visual equipment: home electronic appliances: machine tools: personal electronic equipment: and industrial robots etc.

"High Quality": Transportation equipment (automobiles, trains, ships, etc.); traffic control systems; anti-disaster systems; anti-crime systems; and safety equipment etc.

Renesas Electronics products are neither intended nor authorized for use in products or systems that may pose a direct threat to human life or bodily injury (artificial life support devices or systems, surgical implantations etc.), or may cause serious property damages (nuclear reactor control systems, military equipment etc.). You must check the quality grade of each Renesas Electronics product before using it in a particular application. You may not use any Renesas Electronics product for any application for which it is not intended. Renesas Electronics shall not be in any way liable for any damages or losses incurred by you or third parties arising from the use of any Renesas Electronics product for which the product is not intended by Renesas Electronics

- 6. You should use the Renesas Electronics products described in this document within the range specified by Renesas Electronics, especially with respect to the maximum rating, operating supply voltage range, movement power voltage range, heat radiation characteristics, installation and other product characteristics. Renesas Electronics shall have no liability for malfunctions or damages arising out of the use of Renesas Electronics products beyond such specified ranges.

- 7. Although Renesas Electronics endeavors to improve the quality and reliability of its products, semiconductor products have specific characteristics such as the occurrence of failure at a certain rate and malfunctions under certain use conditions. Further, Renesas Electronics products are not subject to radiation resistance design. Please be sure to implement safety measures to guard them against the possibility of physical injury, and injury or damage caused by fire in the event of the failure of a Renesas Electronics product, such as safety design for hardware and software including but not limited to redundancy, fire control and malfunction prevention, appropriate treatment for aging degradation or any other appropriate measures. Because the evaluation of microcomputer software alone is very difficult, please evaluate the safety of the final products or systems manufactured by you.

- 8. Please contact a Renesas Electronics sales office for details as to environmental matters such as the environmental compatibility of each Renesas Electronics product. Please use Renesas Electronics products in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. Renesas Electronics assumes no liability for damages or losses occurring as a result of your noncompliance with applicable laws and regulations.

- Renesas Electronics products and technology may not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable domestic or foreign laws or regulations. You should not use Renesas Electronics products or technology described in this document for any purpose relating to military applications or use by the military, including but not limited to the development of weapons of mass destruction. When exporting the Renesas Electronics products or technology described in this document, you should comply with the applicable export control laws and regulations and follow the procedures required by such laws and regulations.

- 10. It is the responsibility of the buyer or distributor of Renesas Electronics products, who distributes, disposes of, or otherwise places the product with a third party, to notify such third party in advance of the contents and conditions set forth in this document. Renesas Electronics assumes no responsibility for any losses incurred by you or third parties as a result of unauthorized use of Renesas Electronics

- nt may not be reproduced or duplicated in any form, in whole or in part, without prior written consent of Renesas Electronics

- 12. Please contact a Renesas Electronics sales office if you have any questions regarding the information contained in this document or Renesas Electronics products, or if you have any other inquiries

- (Note 2) "Renesas Electronics product(s)" means any product developed or manufactured by or for Renesas Electronics.

#### SALES OFFICES

### Renesas Electronics Corporation

http://www.renesas.com

Refer to "http://www.renesas.com/" for the latest and detailed information

California Eastern Laboratories, Inc.

4590 Patrick Henry Drive, Santa Clara, California 95054-1817, U.S.A Tel: +1-408-919-2500, Fax: +1-408-988-0279

Renesas Electronics Europe Limited

Dukes Meadow, Millboard Road, Bourne End, Buckinghamshire, SL8 5FH, U.K

Tel: +44-1628-585-100, Fax: +44-1628-585-900

Renesas Electronics Europe GmbH

Arcadiastrasse 10, 40472 Düsseldorf, German Tel: +49-211-6503-0, Fax: +49-211-6503-1327

Renesas Electronics (China) Co., Ltd.

Room 1709, Quantum Plaza, No.27 ZhiChunLu Haidian District, Beijing 100191, P.R.China Tel: +86-10-8235-1155, Fax: +86-10-8235-7679

Renesas Electronics (Shanghai) Co., Ltd.

Unit 301, Tower A, Central Towers, 555 Langao Road, Putuo District, Shanghai, P. R. China 200333 Tel: +86-21-2226-0888, Fax: +86-21-2226-0999

Renesas Electronics Hong Kong Limited ntury Place, 193 Prince Edward Road West, Mongkok, Kowloon, Hong Kong

t 1601-1611, 16/F., Tower 2, Grand Cen : +852-2265-6688, Fax: +852 2886-9022

Renesas Electronics Taiwan Co., Ltd. 13F, No. 363, Fu Shing North Road, Taipei 10543, Taiwan Tel: +886-2-8175-9600, Fax: +886 2-8175-9670

Renesas Electronics Singapore Pte. Ltd. 80 Bendemeer Road, Unit #06-02 Hyflux Innovation Centre, Singapore 339949 Tel: +65-6213-0200, Fax: +65-6213-0300

Renesas Electronics Malaysia Sdn.Bhd.

Unit 1207, Block B, Menara Amcorp, Amcorp Trade Centre, No. 18, Jln Persiaran Barat, 46050 Petaling Jaya, Selangor Darul Ehsan, Malaysia Tel: +60-3-7955-9390, Fax: +60-3-7955-9510

Renesas Electronics India Pvt. Ltd.

No.777C, 100 Feet Road, HAL II Stage, Indiranagar, Bangalore, India Tel: +91-80-67208700, Fax: +91-80-67208777

Renesas Electronics Korea Co., Ltd. 12F., 234 Teheran-ro, Gangnam-Gu, Seoul, 135-080, Korea Tel: +82-2-558-3737, Fax: +82-2-558-5141