# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113hh005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

- 2.7 V to 3.6 V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore! XP<sup>®</sup> F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Program Memory Address (Hex)                | Function                   |

|---------------------------------------------|----------------------------|

| 0002–0003                                   | Reset Vector               |

| 0004–0005                                   | WDT Interrupt Vector       |

| 0006–0007                                   | Illegal Instruction Trap   |

| 0008–0037                                   | Interrupt Vectors*         |

| 0038–003D                                   | Oscillator Fail Traps*     |

| 003E-03FF                                   | Program Memory             |

| ee Table 33 on page 54 for a list of the in | terrupt vectors and traps. |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

## **Data Memory**

Z8 Encore! XP<sup>®</sup> F0823 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

## **Flash Information Area**

Table 7 lists the Z8 Encore! XP F0823 Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address<br>(Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. Z8 Encore! XP F0823 Series Flash Memory Information Area Map

| Address (Hex)   | Register Description      | Mnemonic | Reset (Hex) | Page No |

|-----------------|---------------------------|----------|-------------|---------|

| F0C             | Timer 1 PWM High Byte     | T1PWMH   | 00          | 81      |

| F0D             | Timer 1 PWM Low Byte      | T1PWML   | 00          | 82      |

| F0E             | Timer 1 Control 0         | T1CTL0   | 00          | 82      |

| F0F             | Timer 1 Control 1         | T1CTL1   | 00          | 80      |

| F10–F3F         | Reserved                  | —        | XX          |         |

| UART            |                           |          |             |         |

| F40             | UART0 Transmit Data       | U0TXD    | XX          | 104     |

|                 | UART0 Receive Data        | U0RXD    | XX          | 105     |

| F41             | UART0 Status 0            | U0STAT0  | 0000011Xb   | 105     |

| F42             | UART0 Control 0           | U0CTL0   | 00          | 107     |

| F43             | UART0 Control 1           | U0CTL1   | 00          | 107     |

| F44             | UART0 Status 1            | U0STAT1  | 00          | 106     |

| F45             | UART0 Address Compare     | U0ADDR   | 00          | 109     |

| F46             | UART0 Baud Rate High Byte | U0BRH    | FF          | 110     |

| F47             | UART0 Baud Rate Low Byte  | U0BRL    | FF          | 110     |

| F48–F6F         | Reserved                  | _        | XX          |         |

| Analog-to-Digit | al Converter (ADC)        |          |             |         |

| F70             | ADC Control 0             | ADCCTL0  | 00          | 122     |

| F71             | ADC Control 1             | ADCCTL1  | 80          | 122     |

| F72             | ADC Data High Byte        | ADCD_H   | XX          | 124     |

| F73             | ADC Data Low Bits         | ADCD_L   | XX          | 124     |

| F74–F7F         | Reserved                  | _        | XX          |         |

| Low Power Cor   | ntrol                     |          |             |         |

| F80             | Power Control 0           | PWRCTL0  | 80          | 33      |

| F81             | Reserved                  |          | XX          |         |

| LED Controller  |                           |          |             |         |

| F82             | LED Drive Enable          | LEDEN    | 00          | 51      |

| F83             | LED Drive Level High Byte | LEDLVLH  | 00          | 51      |

| F84             | LED Drive Level Low Byte  | LEDLVLL  | 00          | 52      |

| F85             | Reserved                  | _        | XX          |         |

| Oscillator Cont | rol                       |          |             |         |

| F86             | Oscillator Control        | OSCCTL   | A0          | 167     |

| F87–F8F         | Reserved                  | _        | XX          |         |

| Comparator 0    |                           |          |             |         |

| F90             | Comparator 0 Control      | CMP0     | 14          | 128     |

|                 |                           |          |             |         |

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | LEDEN[7:0] |     |     |     |     |     |     |     |

| RESET | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F82H       |     |     |     |     |     |     |     |

#### Table 30. LED Drive Enable (LEDEN)

#### LEDEN[7:0]—LED Drive Enable

These bits determine which Port C pins are connected to an internal current sink.

0 = Tristate the Port C pin.

1= Connect controlled current sink to the Port C pin.

### LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 31). These two bits select between four programmable drive levels. Each pin is individually programmable.

#### Table 31. LED Drive Level High Register (LEDLVLH)

| BITS  | 7            | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | LEDLVLH[7:0] |     |     |     |     |     |     |     |

| RESET | 0            | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W          | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F83H         |     |     |     |     |     |     |     |

LEDLVLH[7:0]—LED Level High Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA

10= 13 mA 11= 20 mA

## LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 32). These two bits select between four programmable drive levels. Each pin is individually programmable.

- 0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

- 10 = Timer Interrupt only on defined Input Capture/Deassertion Events

- 11 = Timer Interrupt only on defined Reload/Compare Events

Reserved-Must be 0

#### PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

000 = No delay 001 = 2 cycles delay 010 = 4 cycles delay 011 = 8 cycles delay 100 = 16 cycles delay 101 = 32 cycles delay 110 = 64 cycles delay111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| BITS  | 7          | 6    | 5    | 4   | 3   | 2     | 1   | 0   |

|-------|------------|------|------|-----|-----|-------|-----|-----|

| FIELD | TEN        | TPOL | PRES |     |     | TMODE |     |     |

| RESET | 0          | 0    | 0    | 0   | 0   | 0     | 0   | 0   |

| R/W   | R/W        | R/W  | R/W  | R/W | R/W | R/W   | R/W | R/W |

| ADDR  | F07H, F0FH |      |      |     |     |       |     |     |

Table 56. Timer 0–1 Control Register 1 (TxCTL1)

TEN—Timer Enable

0 = Timer is disabled

1 = Timer enabled to count

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer

Watchdog Timer Reload Byte registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

| BITS  | 7       | 6 | 5 | 4  | 3  | 2 | 1 | 0 |  |  |  |

|-------|---------|---|---|----|----|---|---|---|--|--|--|

| FIELD | WDTUNLK |   |   |    |    |   |   |   |  |  |  |

| RESET | Х       | Х | Х | Х  | Х  | Х | Х | Х |  |  |  |

| R/W   | W       | W | W | W  | W  | W | W | W |  |  |  |

| ADDR  |         |   |   | FF | ОH |   |   |   |  |  |  |

WDTUNLK—Watchdog Timer Unlock

The software must write the correct unlocking sequence to this register before it is allowed to modify the contents of the Watchdog Timer reload registers.

## Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, High and Low Byte (WDTU, WDTH, WDTL) registers (Tables 59 through Table 61) form the 24-bit reload value that is loaded into the Watchdog Timer when a WDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers returns the current Watchdog Timer count value.

**Caution:** *The 24-bit WDT Reload Value must not be set to a value less than* 000004H.

No

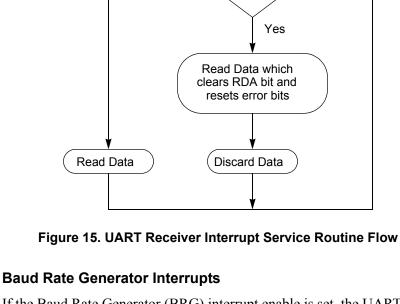

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

Receiver Ready

Receiver Interrupt

Read Status

Errors?

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------|---|---|---|---|---|---|---|--|--|--|

| FIELD | TXD  |   |   |   |   |   |   |   |  |  |  |

| RESET | Х    | Х | Х | Х | Х | Х | Х | Х |  |  |  |

| R/W   | W    | W | W | W | W | W | W | W |  |  |  |

| ADDR  | F40H |   |   |   |   |   |   |   |  |  |  |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

#### **Software Compensation Procedure**

The value read from the ADC high and low byte registers are uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following formula yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) * GAINCAL)/2^{16}$

where GAINCAL is the gain calibration byte, OFFCAL is the offset calibration byte and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. The OFFCAL value is in two's complement format, as are the compensated and uncompensated ADC values.

- Note: The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits. Also note that in the second term, the multiplication must be performed before the division by 2<sup>16</sup>. Otherwise, the second term evaluates to zero incorrectly.

- **Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

# **ADC Control Register Definitions**

The following sections define the ADC control registers.

## **ADC Control Register 0**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6       | 5      | 4    | 3          | 2   | 1   | 0   |  |  |  |

|-------|-----|---------|--------|------|------------|-----|-----|-----|--|--|--|

| FIELD | CEN | REFSELL | REFEXT | CONT | ANAIN[3:0] |     |     |     |  |  |  |

| RESET | 0   | 0       | 0      | 0    | 0          | 0   | 0   | 0   |  |  |  |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W        | R/W | R/W | R/W |  |  |  |

| ADDR  |     | F70H    |        |      |            |     |     |     |  |  |  |

Table 72. ADC Control Register 0 (ADCCTL0)

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

130

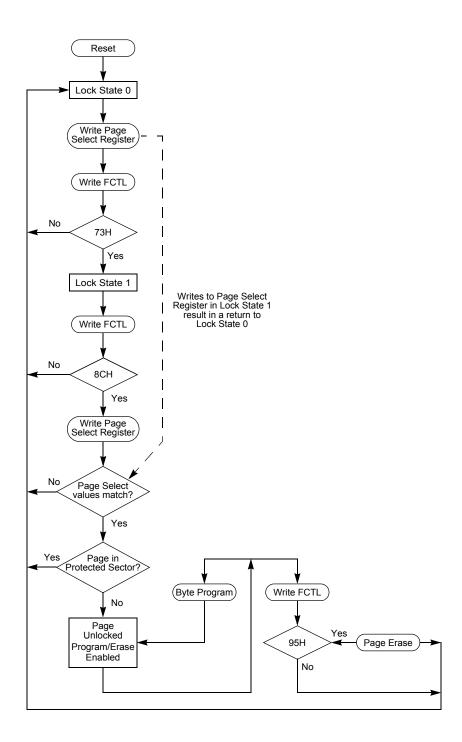

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

132

Figure 21. Flash Controller Operation Flowchart

# **Flash Control Register Definitions**

## **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FTCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| BITS  | 7    | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------|------|---|---|---|---|---|---|--|--|--|

| FIELD | FCMD |      |   |   |   |   |   |   |  |  |  |

| RESET | 0    | 0    | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| R/W   | W    | W    | W | W | W | W | W | W |  |  |  |

| ADDR  |      | FF8H |   |   |   |   |   |   |  |  |  |

Table 79. Flash Control Register (FCTL)

FCMD—Flash Command

73H = First unlock command

8CH = Second unlock command

95H = Page Erase command (must be third command in sequence to initiate Page Erase) 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase)

5EH = Enable Flash Sector Protect Register Access

## **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Table 80. Flash Status | Register (FSTAT) |

|------------------------|------------------|

|------------------------|------------------|

| BITS  | 7    | 6     | 5 | 4 | 3  | 2     | 1 | 0 |  |  |

|-------|------|-------|---|---|----|-------|---|---|--|--|

| FIELD | Rese | erved |   |   | FS | FSTAT |   |   |  |  |

| RESET | 0    | 0     | 0 | 0 | 0  | 0     | 0 | 0 |  |  |

| R/W   | R    | R     | R | R | R  | R     | R | R |  |  |

| ADDR  | FF8H |       |   |   |    |       |   |   |  |  |

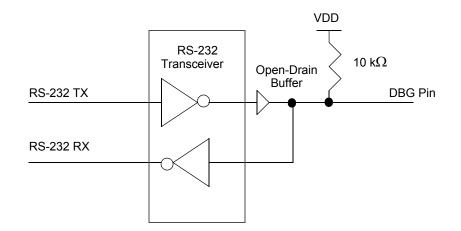

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP mode

- All enabled on-chip peripherals operate unless in STOP mode

- Automatically exits HALT mode

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG mode following the operations below:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG mode upon exiting System Reset

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 154).

• If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled high. At this

is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0AH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

174

Table 106 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

|        | -                         |

|--------|---------------------------|

| Symbol | Definition                |

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Table 106. Additional Symbols

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

# **Ordering Information**

| Part Number               | Flash      | RAM       | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|---------------------------|------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP with 8      |            |           | Analog    | j-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature      |            |           |           | 40         | 0                      | 4                   | 4              |                     |

| Z8F0823PB005SC            | 8 KB       | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005SC            | 8 KB       | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005SC            | 8 KB       | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005SC            | 8 KB       | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005SC            | 8 KB       | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005SC            | 8 KB       | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005SC            | 8 KB       | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005SC            | 8 KB       | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005SC            | 8 KB       | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur       | e: -40 °C  | to 105 °( | C         |            |                        |                     |                |                     |

| Z8F0823PB005EC            | 8 KB       | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005EC            | 8 KB       | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005EC            | 8 KB       | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005EC            | 8 KB       | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005EC            | 8 KB       | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005EC            | 8 KB       | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005EC            | 8 KB       | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005EC            | 8 KB       | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005EC            | 8 KB       | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Leas | d-Free Pac | kaging    |           |            |                        |                     |                |                     |

| nber                                |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |  |

|-------------------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|

| Part Number                         | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |  |

| Z8 Encore! XP with 2                | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |  |

| Standard Temperature: 0 °C to 70 °C |            |            |           |            |                        |                     |                |                     |  |

| Z8F0223PB005SC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |

| Z8F0223QB005SC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |

| Z8F0223SB005SC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |

| Z8F0223SH005SC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |

| Z8F0223HH005SC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |

| Z8F0223PH005SC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |

| Z8F0223SJ005SC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |

| Z8F0223HJ005SC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |

| Z8F0223PJ005SC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |

| Extended Temperatur                 | e: -40 °C  | to 105 °C  | ;         |            |                        |                     |                |                     |  |

| Z8F0223PB005EC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |

| Z8F0223QB005EC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |

| Z8F0223SB005EC                      | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |

| Z8F0223SH005EC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |

| Z8F0223HH005EC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |

| Z8F0223PH005EC                      | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |

| Z8F0223SJ005EC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |

| Z8F0223HJ005EC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |

| Z8F0223PJ005EC                      | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |

| Replace C with G for Leas           | d-Free Pac | kaging     |           |            |                        |                     |                |                     |  |

221

231

L LD 177 LDC 177 LDCI 176, 177 LDE 177 LDEI 176, 177 LDX 177 LEA 177 load 177 load constant 176 load constant to/from program memory 177 load constant with auto-increment addresses 177 load effective address 177 load external data 177 load external data to/from data memory and auto-increment addresses 176 load external to/from data memory and auto-increment addresses 177 load instructions 177 load using extended addressing 177 logical AND 177 logical AND/extended addressing 177 logical exclusive OR 178 logical exclusive OR/extended addressing 178 logical instructions 177 logical OR 177 logical OR/extended addressing 178 low power modes 31

## Μ

master interrupt enable 55 memory data 15 program 13 mode CAPTURE 84, 85 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 84 ONE-SHOT 84 PWM 84, 85 modes 84 MULT 175 multiply 175 MULTIPROCESSOR mode, UART 99

# Ν

NOP (no operation) 176 notation b 173 cc 173 DA 173 ER 173 IM 173 IR 173 Ir 173 **IRR 173** Irr 173 p 173 R 173 r 173 RA 173 RR 173 rr 173 vector 173 X 173 notational shorthand 173

#### O OCD

architecture 151 auto-baud detector/generator 154 baud rate limits 155 block diagram 151 breakpoints 156 commands 157 control register 161 data format 154 DBG pin to RS-232 Interface 152 DEBUG mode 153 debugger break 178 interface 152 serial errors 155

timing 205 OCD commands execute instruction (12H) 161 read data memory (0DH) 160 read OCD control register (05H) 158 read OCD revision (00H) 158 read OCD status register (02H) 158 read program counter (07H) 159 read program memory (0BH) 160 read program memory CRC (0EH) 161 read register (09H) 159 read runtime counter (03H) 158 step instruction (10H) 161 stuff instruction (11H) 161 write data memory (0CH) 160 write OCD control register (04H) 158 write program counter (06H) 159 write program memory (0AH) 159 write register (08H) 159 on-chip debugger (OCD) 151 on-chip debugger signals 10 ONE-SHOT mode 84 opcode map abbreviations 189 cell description 188 first 190 second after 1FH 191 Operational Description 21, 31, 35, 53, 67, 87, 93, 113, 117, 127, 129, 141, 151, 165, 169 OR 177 ordering information 217 **ORX 178**

status register 163

# Ρ

p 173 packaging 20-pin PDIP 211, 212 20-pin SSOP 212, 215 28-pin PDIP 213 28-pin SOIC 214 8-pin PDIP 209 8-pin SOIC 210

PDIP 214, 215 part selection guide 2 PC 174 PDIP 214, 215 peripheral AC and DC electrical characteristics 199 pin characteristics 10 Pin Descriptions 7 polarity 173 POP 177 pop using extended addressing 177 **POPX 177** port availability. device 35 port input timing (GPIO) 203 port output timing, GPIO 204 power supply signals 10 power-down, automatic (ADC) 118 Power-on and Voltage Brownout electrical characteristics and timing 199 Power-On Reset (POR) 23 program control instructions 178 program counter 174 program memory 13 **PUSH 177** push using extended addressing 177 PUSHX 177 PWM mode 84, 85 PxADDR register 44

## R

PxCTL register 45

R 173 r 173 RA register address 173 RCF 176 receive IrDA data 115 receiving UART data-interrupt-driven method 98 receiving UART data-polled method 97 register 173 ADC control (ADCCTL) 122, 124 232