Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113hj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

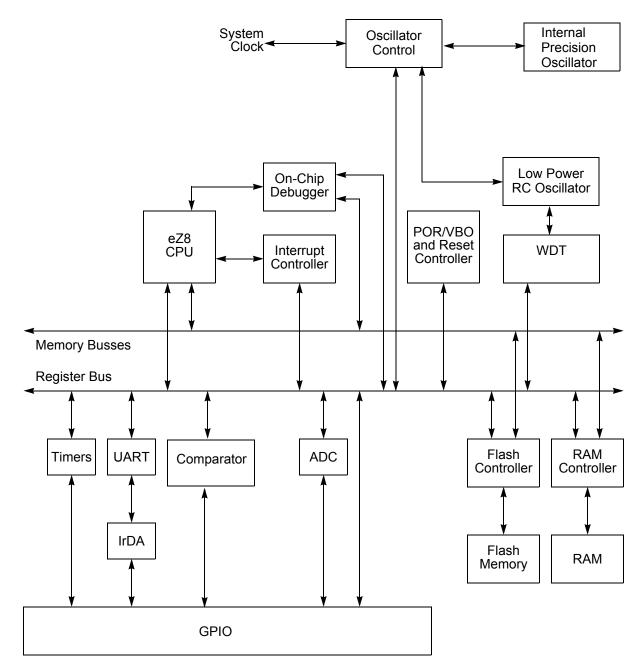

# Block Diagram

Figure 1 on page 3 displays the block diagram of the architecture of Z8 Encore! XP F0823 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0823 Series Block Diagram

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–C Control Registers on page 44), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overline{\text{RESET}}$  pin Low. The  $\overline{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) register is set.

# **Stop Mode Recovery**

The device enters into STOP mode when eZ8 CPU executes a STOP instruction. For more details on STOP mode, see Low-Power Modes on page 31. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

# **Low-Power Modes**

Z8 Encore! XP<sup>®</sup> F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT mode).

# **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled.

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

## Port A–C Pull-up Enable Sub-Registers

The Port A–C Pull-up Enable sub-register (Table 25) is accessed through the Port A–C Control register by writing 06H to the Port A–C Address register. Setting the bits in the Port A–C Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

Table 25. Port A–C Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|

| FIELD | PPUE7    | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                                           |       |       |       |       |       |       |

| ADDR  | lf 06H i | If 06H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

## Port A–C Alternate Function Set 1 Sub-Registers

The Port A–C Alternate Function Set1 sub-register (Table 26) is accessed through the Port A–C Control register by writing 07H to the Port A–C Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 36.

Note:

*Alternate function selection on port pins must also be enabled as described in* Port A–C Alternate Function Sub-Registers *on page 45*.

| BITS  | 7    | 6 | 5             | 4  | 3  | 2 | 1 | 0 |

|-------|------|---|---------------|----|----|---|---|---|

| FIELD | IRQE |   | Reserved      |    |    |   |   |   |

| RESET | 0    | 0 | 0             | 0  | 0  | 0 | 0 | 0 |

| R/W   | R/W  | R | R R R R R R R |    |    |   |   |   |

| ADDR  |      |   |               | FC | FH |   |   |   |

## Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:  $PWM \text{ Period (s)} = \frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge

86

010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value.

0000 = ONE-SHOT mode

0001 = CONTINUOUS mode

0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

- 1000 = PWM DUAL OUTPUT mode

- 1001 = CAPTURE RESTART mode

- 1010 = COMPARATOR COUNTER Mode

| BITS  | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|-----------------------------|---|---|---|---|---|---|

| FIELD |      | COMP_ADDR                   |   |   |   |   |   |   |

| RESET | 0    | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  | F45H |                             |   |   |   |   |   |   |

#### Table 68. UART Address Compare Register (U0ADDR)

COMP ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

# UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (Table 69 and Table 70) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

#### Table 69. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------------------|---|---|---|---|---|---|

| FIELD |     | BRH                         |   |   |   |   |   |   |

| RESET | 1   | 1 1 1 1 1 1 1 1             |   |   |   |   |   |   |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  |     | F46H                        |   |   |   |   |   |   |

#### Table 70. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|-----|-----------------------------|---|---|---|---|---|---|

| FIELD |     | BRL                         |   |   |   |   |   |   |

| RESET | 1   | 1                           | 1 | 1 | 1 | 1 | 1 | 1 |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  |     | F47H                        |   |   |   |   |   |   |

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 71 provides information about data rate errors for 5.5296 MHz System Clock.

| 5.5296 MHz System Clock  |                          |                      |           |  |  |  |

|--------------------------|--------------------------|----------------------|-----------|--|--|--|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |  |  |  |

| 1250.0                   | N/A                      | N/A                  | N/A       |  |  |  |

| 625.0                    | N/A                      | N/A                  | N/A       |  |  |  |

| 250.0                    | 1                        | 345.6                | 38.24     |  |  |  |

| 115.2                    | 3                        | 115.2                | 0.00      |  |  |  |

| 57.6                     | 6                        | 57.6                 | 0.00      |  |  |  |

| 38.4                     | 9                        | 38.4                 | 0.00      |  |  |  |

| 19.2                     | 18                       | 19.2                 | 0.00      |  |  |  |

| 9.60                     | 36                       | 9.60                 | 0.00      |  |  |  |

| 4.80                     | 72                       | 4.80                 | 0.00      |  |  |  |

| 2.40                     | 144                      | 2.40                 | 0.00      |  |  |  |

| 1.20                     | 288                      | 1.20                 | 0.00      |  |  |  |

| 0.60                     | 576                      | 0.60                 | 0.00      |  |  |  |

| 0.30                     | 1152                     | 0.30                 | 0.00      |  |  |  |

#### Table 71. UART Baud Rates

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 93.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO port alternate function for the corresponding pin.

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32 kHz (32768 Hz) through 20 MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32 kHz (32768 Hz) or above 20 MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of Z8 Encore! XP<sup>®</sup> F0823 Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access with the On-Chip Debugger. Programming the FRP Flash Option Bit prevents reading of the user code with the On-Chip Debugger. For more information, see Flash Option Bits on page 141 and On-Chip Debugger on page 151.

## Flash Code Protection Against Accidental Program and Erasure

Z8 Encore! XP F0823 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 78. For more information, see Flash Option Bits on page 141.

# **Oscillator Control**

Z8 Encore! XP<sup>®</sup> F0823 Series devices uses three possible clocking schemes, each user-selectable:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, Z8 Encore! XP F0823 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

## **System Clock Selection**

The oscillator control block selects from the available clocks. Table 101 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                 | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>           | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                   |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 101. Oscillator Configuration and Selection

| Table 1 | 08. Bit | Manipu | lation Ir | nstructions   |

|---------|---------|--------|-----------|---------------|

|         | 00. Dit | manipu |           | 1311 40110113 |

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 109. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                         |

|----------|----------|---------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment Addresses |

### Table 110. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | HALT Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

179

| Table 114. Rotate and Shift Instructions | (Continued) |

|------------------------------------------|-------------|

|------------------------------------------|-------------|

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

# eZ8 CPU Instruction Summary

Table 115 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly        |                                                              | Addre      | ss Mode     | - Opcode(s) | Fla | ags          |   |   |   | - Fetch | Instr. |        |

|-----------------|--------------------------------------------------------------|------------|-------------|-------------|-----|--------------|---|---|---|---------|--------|--------|

| Mnemonic        | Symbolic Operation                                           | dst        | src         | (Hex)       | С   | Ζ            | S | v | D | Н       |        | Cycles |

| ADC dst, src    | $dst \gets dst + src + C$                                    | r          | r           | 12          | *   | *            | * | * | 0 | *       | 2      | 3      |

|                 |                                                              | r          | lr          | 13          | _   |              |   |   |   |         | 2      | 4      |

|                 |                                                              | R          | R           | 14          | _   |              |   |   |   |         | 3      | 3      |

|                 |                                                              | R          | IR          | 15          | _   |              |   |   |   |         | 3      | 4      |

|                 |                                                              | R          | IM          | 16          | _   |              |   |   |   |         | 3      | 3      |

|                 |                                                              | IR         | IM          | 17          | _   |              |   |   |   |         | 3      | 4      |

| ADCX dst, src   | $dst \gets dst + src + C$                                    | ER         | ER          | 18          | *   | *            | * | * | 0 | *       | 4      | 3      |

|                 |                                                              | ER         | IM          | 19          | _   |              |   |   |   |         | 4      | 3      |

| ADD dst, src    | $dst \gets dst + src$                                        | r          | r           | 02          | *   | *            | * | * | 0 | *       | 2      | 3      |

|                 |                                                              | r          | lr          | 03          | _   |              |   |   |   |         | 2      | 4      |

|                 |                                                              | R          | R           | 04          | _   |              |   |   |   |         | 3      | 3      |

|                 |                                                              | R          | IR          | 05          | _   |              |   |   |   |         | 3      | 4      |

|                 |                                                              | R          | IM          | 06          | _   |              |   |   |   |         | 3      | 3      |

|                 |                                                              | IR         | IM          | 07          | _   |              |   |   |   |         | 3      | 4      |

| ADDX dst, src   | $dst \gets dst + src$                                        | ER         | ER          | 08          | *   | *            | * | * | 0 | *       | 4      | 3      |

|                 |                                                              | ER         | IM          | 09          | _   |              |   |   |   |         | 4      | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resu | It of the o | peration.   |     | = Re<br>= Se |   |   | 0 |         |        |        |

#### Table 115. eZ8 CPU Instruction Summary

| 184 |  |

|-----|--|

|-----|--|

| Assembly        |                                                                                                                            | Addre | Address Mode<br>Opcode(s) |       |   | Flags |              |   |   |   |   | Instr. |

|-----------------|----------------------------------------------------------------------------------------------------------------------------|-------|---------------------------|-------|---|-------|--------------|---|---|---|---|--------|

| Mnemonic        | Symbolic Operation                                                                                                         | dst   | src                       | (Hex) | С | Ζ     | S            | v | D | н |   | Cycles |

| OR dst, src     | $dst \gets dst \: OR \: src$                                                                                               | r     | r                         | 42    | _ | *     | *            | 0 | _ | _ | 2 | 3      |

|                 |                                                                                                                            | r     | lr                        | 43    | - |       |              |   |   |   | 2 | 4      |

|                 |                                                                                                                            | R     | R                         | 44    | - |       |              |   |   |   | 3 | 3      |

|                 |                                                                                                                            | R     | IR                        | 45    | _ |       |              |   |   |   | 3 | 4      |

|                 |                                                                                                                            | R     | IM                        | 46    | - |       |              |   |   |   | 3 | 3      |

|                 |                                                                                                                            | IR    | IM                        | 47    | - |       |              |   |   |   | 3 | 4      |

| ORX dst, src    | $dst \gets dst \: OR \: src$                                                                                               | ER    | ER                        | 48    | - | *     | *            | 0 | _ | - | 4 | 3      |

|                 |                                                                                                                            | ER    | IM                        | 49    | _ |       |              |   |   |   | 4 | 3      |

| POP dst         | dst ← @SP                                                                                                                  | R     |                           | 50    | _ | _     | _            | _ | _ | _ | 2 | 2      |

|                 | $SP \leftarrow SP + 1$                                                                                                     | IR    |                           | 51    | - |       |              |   |   |   | 2 | 3      |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                                                                                   | ER    |                           | D8    | - | _     | _            | _ | _ | - | 3 | 2      |

| PUSH src        | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                                                                             | R     |                           | 70    | _ | _     | _            | _ | - | _ | 2 | 2      |

|                 |                                                                                                                            | IR    |                           | 71    | - | _     |              |   |   |   | 2 | 3      |

|                 |                                                                                                                            | IM    |                           | IF70  | - |       |              |   |   |   | 3 | 2      |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP ← src                                                                                        | ER    |                           | C8    | _ | _     | _            | _ | _ | _ | 3 | 2      |

| RCF             | C ← 0                                                                                                                      |       |                           | CF    | 0 | _     | -            | _ | _ | _ | 1 | 2      |

| RET             | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                                                                              |       |                           | AF    | _ | -     | -            | _ | _ | _ | 1 | 4      |

| RL dst          |                                                                                                                            | R     |                           | 90    | * | *     | *            | * | - | _ | 2 | 2      |

|                 | C < D7D6D5D4D3D2D1D0 < dst                                                                                                 | IR    |                           | 91    | - |       |              |   |   |   | 2 | 3      |

| RLC dst         |                                                                                                                            | R     |                           | 10    | * | *     | *            | * | _ | _ | 2 | 2      |

|                 | C D7D6D5D4D3D2D1D0                                                                                                         | IR    |                           | 11    | _ |       |              |   |   |   | 2 | 3      |

| Flags Notation: | <ul> <li>* = Value is a function of the result of the operation.</li> <li>– = Unaffected</li> <li>X = Undefined</li> </ul> |       |                           |       |   |       | ese<br>et to |   | 0 |   |   |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

#### Table 117. Absolute Maximum Ratings (Continued)

| Parameter                                                      | Minimum Maximum | Units | Notes |

|----------------------------------------------------------------|-----------------|-------|-------|

| Maximum current into $V_{\text{DD}}$ or out of $V_{\text{SS}}$ | 125             | mA    |       |

|                                                                |                 |       |       |

Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 118 lists the DC characteristics of the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F0823 Series products. All voltages are referenced to V<sub>SS</sub>, the primary system ground.

#### Table 118. DC Characteristics

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | _                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | _                      | -                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                               |

|                     |                                                    |                         | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C      |                           |                                                                                              |  |  |

|---------------------|----------------------------------------------------|-------------------------|-------------------------------------|------------|---------------------------|----------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                                          | Minimum Typical Maximum |                                     | Units      | Conditions                |                                                                                              |  |  |

|                     | Resolution                                         | 10                      |                                     | _          | bits                      |                                                                                              |  |  |

|                     | Differential Nonlinearity<br>(DNL)                 | -1.0                    | _                                   | 1.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |  |

|                     | Integral Nonlinearity (INL)                        | -3.0                    | _                                   | 3.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |  |

|                     | Offset Error with Calibration                      |                         | <u>+</u> 1                          |            | LSB <sup>3</sup>          |                                                                                              |  |  |

|                     | Absolute Accuracy with Calibration                 |                         | <u>+</u> 3                          |            | LSB <sup>3</sup>          |                                                                                              |  |  |

| V <sub>REF</sub>    | Internal Reference Voltage                         | 1.0<br>2.0              | 1.1<br>2.2                          | 1.2<br>2.4 | V                         | REFSEL=01<br>REFSEL=10                                                                       |  |  |

| V <sub>REF</sub>    | Internal Reference<br>Variation with Temperature   |                         | <u>+</u> 1.0                        |            | %                         | Temperature variation<br>with V <sub>DD</sub> = 3.0                                          |  |  |

| V <sub>REF</sub>    | Internal Reference Voltage Variation with $V_{DD}$ |                         | <u>+</u> 0.5                        |            | %                         | Supply voltage variation<br>with T <sub>A</sub> = 30 °C                                      |  |  |

| R <sub>REFOUT</sub> | Reference Buffer Output<br>Impedance               |                         | 850                                 |            | Ω                         | When the internal<br>reference is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |  |

|                     | Single-Shot Conversion<br>Time                     | _                       | 5129                                | -          | System<br>clock<br>cycles | All measurements but temperature sensor                                                      |  |  |

|                     |                                                    |                         | 10258                               |            |                           | Temperature sensor<br>measurement                                                            |  |  |

|                     | Continuous Conversion<br>Time                      | -                       | 256                                 | -          |                           | All measurements but temperature sensor                                                      |  |  |

|                     |                                                    |                         | 512                                 |            |                           | Temperature sensor<br>measurement                                                            |  |  |

|                     | Signal Input Bandwidth                             | -                       | 10                                  |            | kHz                       | As defined by -3 dB point                                                                    |  |  |

| R <sub>S</sub>      | Analog Source Impedance <sup>4</sup>               | _                       | _                                   | 10         | kΩ                        | In unbuffered mode                                                                           |  |  |

## Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing

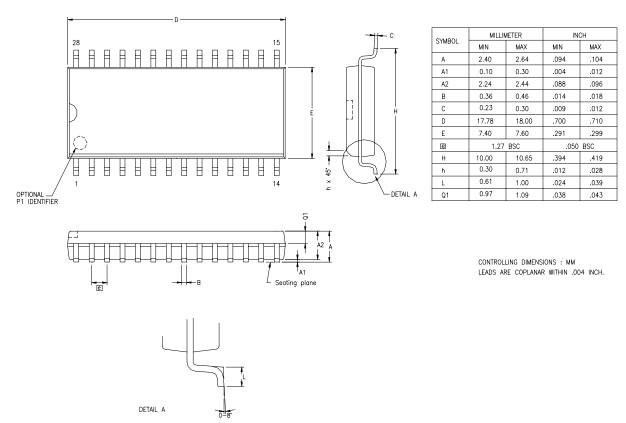

# Figure 41 displays the 28-pin Small Outline Integrated Circuit package (SOIC) available in Z8 Encore! XP F0823 Series devices.

Figure 41. 28-Pin Small Outline Integrated Circuit Package (SOIC)

Index

**COMPARE 84** compare - extended addressing 175 COMPARE mode 84 compare with carry 175 compare with carry - extended addressing 175 complement 177 complement carry flag 176 condition code 173 continuous conversion (ADC) 120 CONTINUOUS mode 84 control register definition, UART 104 Control Registers 13, 17 **COUNTER modes 84** CP 175 CPC 175 **CPCX 175** CPU and peripheral overview 4 CPU control instructions 176 **CPX 175** Customer Support 237

# D

DA 173, 175 data memory 15 DC characteristics 194 debugger, on-chip 151 **DEC 175** decimal adjust 175 decrement 175 decrement and jump non-zero 178 decrement word 175 **DECW 175** destination operand 174 device, port availability 35 DI 176 direct address 173 disable interrupts 176 **DJNZ 178** dst 174

# Ε

EI 176

electrical characteristics 193 ADC 201 flash memory and timing 200 GPIO input data sample timing 202 Watchdog Timer 200, 202 enable interrupt 176 ER 173 extended addressing register 173 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 174 eZ8 CPU instruction notation 172 eZ8 CPU instruction set 171 eZ8 CPU instruction set 171

# F

FCTL register 137, 143, 144 features, Z8 Encore! 1 first opcode map 190 FLAGS 174 flags register 174 flash controller 4 option bit address space 144 option bit configuration - reset 141 program memory address 0000H 144 program memory address 0001H 145 flash memory 129 arrangement 130 byte programming 135 code protection 133 configurations 129 control register definitions 137, 143 controller bypass 136 electrical characteristics and timing 200 flash control register 137, 143, 144 flash option bits 134 flash status register 137 flow chart 132 frequency high and low byte registers 139 mass erase 135 operation 131 operation timing 133

228

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

235

reset in STOP mode 89 time-out response 88 Watchdog Timer Control Register (WDTCTL) 90 WDTCTL register 90, 128, 167 WDTH register 91 WDTL register 91 WDTU register 91 working register 173 working register pair 173

# Χ

X 173 XOR 178 XORX 178

# Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2