Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessoreZ8Core Size8-BitSpeedSMHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)-Data Converters- |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Core Size8-BitSpeed5MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                              |

| Speed5MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                            |

| ConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                     |

| PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                 |

| Number of I/O6Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                      |

| Program Memory Size1KB (1K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                                    |

| Program Memory TypeFLASHEEPROM Size-RAM Size256 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                                                                                                                                                                                                   |

| EEPROM Size     -       RAM Size     256 x 8       Voltage - Supply (Vcc/Vdd)     2.7V ~ 3.6V                                                                                                                                                                                              |

| RAM Size         256 x 8           Voltage - Supply (Vcc/Vdd)         2.7V ~ 3.6V                                                                                                                                                                                                          |

| Voltage - Supply (Vcc/Vdd) 2.7V ~ 3.6V                                                                                                                                                                                                                                                     |

|                                                                                                                                                                                                                                                                                            |

| Data Converters -                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                            |

| Oscillator Type Internal                                                                                                                                                                                                                                                                   |

| Operating Temperature -40°C ~ 105°C (TA)                                                                                                                                                                                                                                                   |

| Mounting Type Through Hole                                                                                                                                                                                                                                                                 |

| Package / Case         8-DIP (0.300", 7.62mm)                                                                                                                                                                                                                                              |

| Supplier Device Package -                                                                                                                                                                                                                                                                  |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f0113pb005ec                                                                                                                                                                                                                     |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|--|--|--|

| Reset<br>Type         | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |  |  |  |

| System<br>Reset       | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL and OSC_CTL<br>registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |  |  |  |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

## **Reset Sources**

Table 10 lists the possible sources of a System Reset.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

#### Table 17. GPIO Port Registers and Sub-Registers

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 33. Trap and Interrupt Vectors in Order of Priority (Continued)

## Architecture

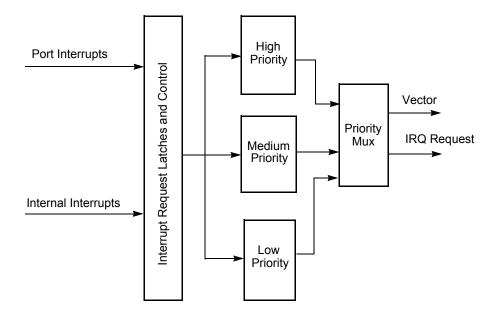

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

#### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an Enable Interrupt (EI) instruction

- Execution of an Return from Interrupt (IRET) instruction

## **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 35. Interrupt Request 1 Register (IRQ1)

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-------|-------|------|------|------|------|------|------|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |       |       |      | FC   | 3H   |      |      |      |

PA7VI—Port A7 Interrupt Request

0 = No interrupt request is pending for GPIO Port A

1 = An interrupt request from GPIO Port A

PA6CI—Port A6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator

1 = An interrupt request from GPIO Port A or Comparator

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin x

1 = An interrupt request from GPIO Port A pin x is awaiting service

where x indicates the specific GPIO Port pin number (0-5)

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 36) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

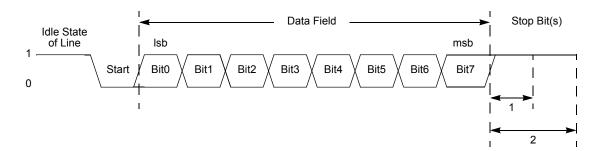

Figure 11. UART Asynchronous Data Format without Parity

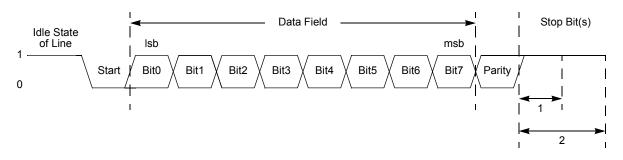

Figure 12. UART Asynchronous Data Format with Parity

#### Transmitting Data using the Polled Method

Follow the steps below to transmit data using the polled method of operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the required baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Write to the UART Control 1 register, if MULTIPROCESSOR mode is appropriate, to enable MULTIPROCESSOR (9-bit) mode functions.

- 4. Set the Multiprocessor Mode Select (MPEN) bit to enable MULTIPROCESSOR mode.

- 5. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission

- Set the parity enable bit (PEN), if parity is appropriate and MULTIPROCESSOR mode is not enabled, and select either even or odd parity (PSEL).

- Set or clear the CTSE bit to enable or disable control from the remote receiver using the CTS pin.

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

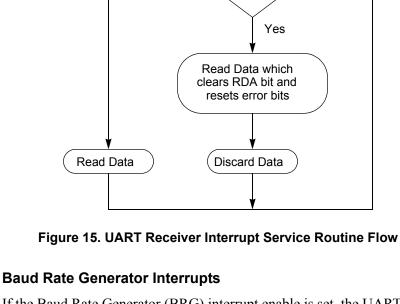

No

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

Receiver Ready

Receiver Interrupt

Read Status

Errors?

## **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

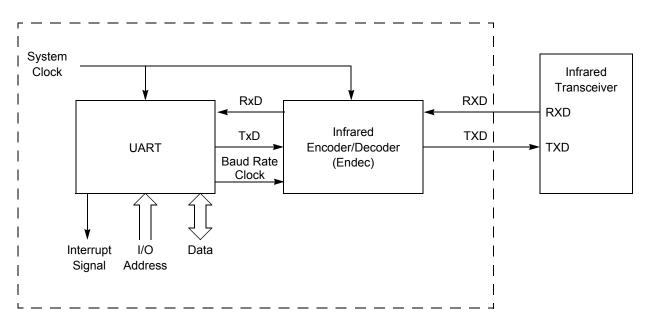

# **Infrared Encoder/Decoder**

Z8 Encore! XP<sup>®</sup> F0823 Series products contain a fully-functional, high-performance UART with Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

# Architecture

Figure 16 displays the architecture of the Infrared Endec.

Figure 16. Infrared Data Communication System Block Diagram

# Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared

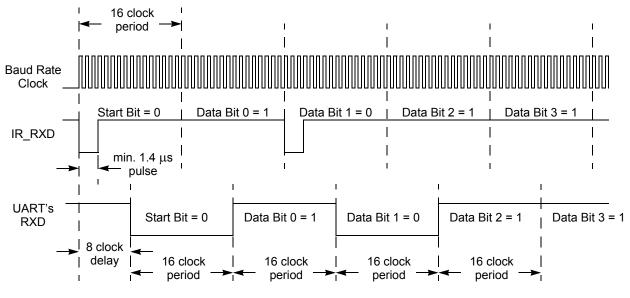

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the 1.4 μs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

# **Flash Memory**

The products in Z8 Encore! XP<sup>®</sup> F0823 Series features either 8 KB (8192), 4 KB (4096), 2 KB (2048) or 1 KB (1024) of non-volatile Flash memory with read/write/erase capability. Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash Memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program/data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F0823 Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes in size (all other memory sizes); each sector maps to a page. Page and sector sizes are not generally equal.

The first two bytes of the Flash Program memory are used as Flash Option Bits. For more information on their operation, see Flash Option Bits on page 141.

Table 77 describes the Flash memory configuration for each device in the Z8 Encore! XP F0823 Series. Figure 20 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08x3     | 8 (8192)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F04x3     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02x3     | 2 (2048)                 | 4              | 0000H–07FFH                 | 512                          |

| Z8F01x3     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

#### Table 77. Z8 Encore! XP F0823 Series Flash Memory Configurations

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

#### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore! (AN0117) available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select register

- Bits in the Flash Sector Protect register can be written to one or zero

- The second write of the Page Select register to unlock the Flash Controller is not necessary

- The Page Select register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control register

- **Caution:** For security reasons, Flash controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash controller must go through the unlock sequence again to select another page.

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

Table 86. Trim Bit Data Register (TRMDR)

| BITS  | 7                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-------|-----------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD | TRMDR - Trim Bit Data |     |     |     |     |     |     |     |  |  |  |  |

| RESET | 0                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| R/W   | R/W                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR  |                       |     |     | FF  | 7H  |     |     |     |  |  |  |  |

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

## Flash Program Memory Address 0000H

Table 87. Flash Option Bits at Program Memory Address 0000H

| BITS      | 7                    | 7 6 5 4 3 2 1 0 |              |          |        |     |          |     |  |  |  |  |

|-----------|----------------------|-----------------|--------------|----------|--------|-----|----------|-----|--|--|--|--|

| FIELD     | WDT_RES              | WDT_AO          | Reserved     |          | VBO_AO | FRP | Reserved | FWP |  |  |  |  |

| RESET     | U                    | U               | U            | U        | U U U  |     | U        | U   |  |  |  |  |

| R/W       | R/W                  | R/W             | R/W          | R/W      | R/W    | R/W | R/W      | R/W |  |  |  |  |

| ADDR      | Program Memory 0000H |                 |              |          |        |     |          |     |  |  |  |  |

| Note: U = | Unchanged by         | y Reset. R/W    | = Read/Write | <b>.</b> |        |     |          |     |  |  |  |  |

WDT RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always ON

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the

| Debug Command       | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit |

|---------------------|-----------------|---------------------------------------|----------------------------------------------|

| Stuff Instruction   | 11H             | -                                     | Disabled.                                    |

| Execute Instruction | 12H             | -                                     | Disabled.                                    |

| Reserved            | 13H–FFH         | _                                     | _                                            |

In the following list of OCD Commands, data and commands sent from the host to the OCD are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the OCD back to the host is identified by 'DBG  $\rightarrow$  Data'.

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the OCD. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

Read OCD Status Register (02H)—The Read OCD Status register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

Read Runtime Counter (03H)—The Runtime Counter counts system clock cycles in between breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

182

| Assembly        |                                                                                                                       | Addre       | ss Mode    | - Opcode(s) | Fla | ıgs |               |   |   |   | - Fetch | Instr  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-----|-----|---------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                                                                    | dst         | src        | (Hex)       | С   | z   | S             | v | D | Н |         | Cycles |

| HALT            | HALT Mode                                                                                                             |             |            | 7F          | -   | _   | -             | _ | - | - | 1       | 2      |

| INC dst         | $dst \leftarrow dst + 1$                                                                                              | R           |            | 20          | -   | *   | *             | _ | - | - | 2       | 2      |

|                 |                                                                                                                       | IR          |            | 21          | -   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | r           |            | 0E-FE       | _   |     |               |   |   |   | 1       | 2      |

| INCW dst        | $dst \leftarrow dst + 1$                                                                                              | RR          |            | A0          | -   | *   | *             | * | - | - | 2       | 5      |

|                 |                                                                                                                       | IRR         |            | A1          | -   |     |               |   |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP \\ SP \leftarrow SP + 1 \\ PC \leftarrow @SP \\ SP \leftarrow SP + 2 \\ IRQCTL[7] \leftarrow 1$ |             |            | BF          | *   | *   | *             | * | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                        | DA          |            | 8D          | _   | _   | _             | _ | _ | _ | 3       | 2      |

|                 |                                                                                                                       | IRR         |            | C4          | -   |     |               |   |   |   | 2       | 3      |

| JP cc, dst      | if cc is true<br>PC $\leftarrow$ dst                                                                                  | DA          |            | 0D-FD       | -   | _   | -             | _ | _ | - | 3       | 2      |

| JR dst          | $PC \leftarrow PC + X$                                                                                                | DA          |            | 8B          | -   | _   | _             | _ | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                               | DA          |            | 0B-FB       | -   | _   | _             | _ | _ | - | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                       | r           | IM         | 0C-FC       | -   | _   | -             | _ | - | - | 2       | 2      |

|                 |                                                                                                                       | r           | X(r)       | C7          | -   |     |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | X(r)        | r          | D7          | _   |     |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | r           | lr         | E3          | _   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | R           | R          | E4          | _   |     |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | R           | IR         | E5          | _   |     |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | R           | IM         | E6          | -   |     |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | IR          | IM         | E7          | -   |     |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | lr          | r          | F3          | -   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | IR          | R          | F5          | -   |     |               |   |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                          | f the resul | t of the o | peration.   |     |     | eset<br>et to |   | 0 |   |         |        |

### Table 115. eZ8 CPU Instruction Summary (Continued)

183

| Assembly        |                                                              | Addre       | ss Mode    | -<br>Opcode(s) | Fla | ıgs |              |   |   |   | - Fetch | Instr. |

|-----------------|--------------------------------------------------------------|-------------|------------|----------------|-----|-----|--------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                           | dst         | src        | (Hex)          | С   | z   | S            | v | D | Н |         | Cycles |

| LDC dst, src    | $dst \gets src$                                              | r           | Irr        | C2             | -   | _   |              | _ | _ | - | 2       | 5      |

|                 |                                                              | lr          | Irr        | C5             | _   |     |              |   |   |   | 2       | 9      |

|                 |                                                              | Irr         | r          | D2             | _   |     |              |   |   |   | 2       | 5      |

| LDCI dst, src   | $dst \leftarrow src$                                         | lr          | Irr        | C3             | -   | _   | _            | _ | _ | _ | 2       | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr         | lr         | D3             | _   |     |              |   |   |   | 2       | 9      |

| LDE dst, src    | $dst \leftarrow src$                                         | r           | Irr        | 82             | -   | _   | -            | _ | _ | - | 2       | 5      |

|                 |                                                              | Irr         | r          | 92             | _   |     |              |   |   |   | 2       | 5      |

| LDEI dst, src   | $dst \gets src$                                              | lr          | Irr        | 83             | -   | _   |              | _ | _ | - | 2       | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr         | lr         | 93             | _   |     |              |   |   |   | 2       | 9      |

| LDWX dst, src   | $dst \leftarrow src$                                         | ER          | ER         | 1FE8           | _   | _   | . <u> </u>   | _ | _ | _ | 5       | 4      |

| LDX dst, src    | $dst \gets src$                                              | r           | ER         | 84             | -   | _   |              | _ | _ | _ | 3       | 2      |

|                 |                                                              | lr          | ER         | 85             | _   |     |              |   |   |   | 3       | 3      |

|                 |                                                              | R           | IRR        | 86             | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                              | IR          | IRR        | 87             | _   |     |              |   |   |   | 3       | 5      |

|                 |                                                              | r           | X(rr)      | 88             | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                              | X(rr)       | r          | 89             | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                              | ER          | r          | 94             | _   |     |              |   |   |   | 3       | 2      |

|                 |                                                              | ER          | lr         | 95             | _   |     |              |   |   |   | 3       | 3      |

|                 |                                                              | IRR         | R          | 96             |     |     |              |   |   |   | 3       | 4      |

|                 |                                                              | IRR         | IR         | 97             | _   |     |              |   |   |   | 3       | 5      |

|                 |                                                              | ER          | ER         | E8             | _   |     |              |   |   |   | 4       | 2      |

|                 |                                                              | ER          | IM         | E9             | _   |     |              |   |   |   | 4       | 2      |

| LEA dst, X(src) | $dst \gets src + X$                                          | r           | X(r)       | 98             | -   | _   |              | _ | _ | - | 3       | 3      |

|                 |                                                              | rr          | X(rr)      | 99             |     |     |              |   |   |   | 3       | 5      |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR          |            | F4             | -   | _   |              | _ | _ | - | 2       | 8      |

| NOP             | No operation                                                 |             |            | 0F             | -   | _   | -            | _ | _ | - | 1       | 2      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resul | t of the c | operation.     |     |     | ese<br>et to |   | 0 |   |         |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                              | Addre      | Address Mode |                    | Fla | ags        |   |             | – Fetch | Instr. |   |        |

|-----------------|--------------------------------------------------------------|------------|--------------|--------------------|-----|------------|---|-------------|---------|--------|---|--------|

| Mnemonic        | Symbolic Operation                                           | dst        | src          | Opcode(s)<br>(Hex) | С   | z          | S | V           | D       | Н      |   | Cycles |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                  | r          | r            | B2                 | _   | *          | * | 0           | -       | _      | 2 | 3      |

|                 |                                                              | r          | lr           | B3                 | _   |            |   |             |         |        | 2 | 4      |

|                 |                                                              | R          | R            | B4                 | _   |            |   |             |         |        | 3 | 3      |

|                 |                                                              | R          | IR           | B5                 | -   |            |   |             |         |        | 3 | 4      |

|                 |                                                              | R          | IM           | B6                 | -   |            |   |             |         |        | 3 | 3      |

|                 |                                                              | IR         | IM           | B7                 | _   |            |   |             |         |        | 3 | 4      |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                  | ER         | ER           | B8                 | _   | *          | * | 0           | _       | _      | 4 | 3      |

|                 |                                                              | ER         | IM           | B9                 | _   |            |   |             |         |        | 4 | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resu | It of the o  | peration.          | -   | = R<br>= S |   | t to<br>5 1 | 0       |        |   |        |

### Table 115. eZ8 CPU Instruction Summary (Continued)

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

192

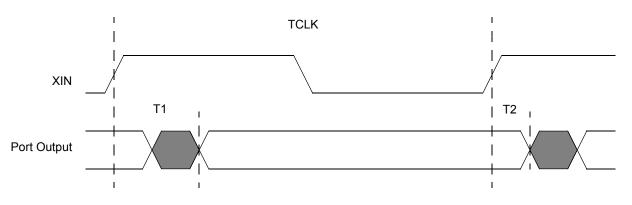

# General Purpose I/O Port Output Timing

Figure 30 and Table 128 provide timing information for GPIO Port pins.

## Figure 30. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |  |  |  |  |  |  |

|----------------|-------------------------------------|------------|---------|--|--|--|--|--|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |  |  |  |  |  |

| GPIO Port pins |                                     |            |         |  |  |  |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | - 15       |         |  |  |  |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |  |  |  |  |  |

## Table 128. GPIO Port Output Timing

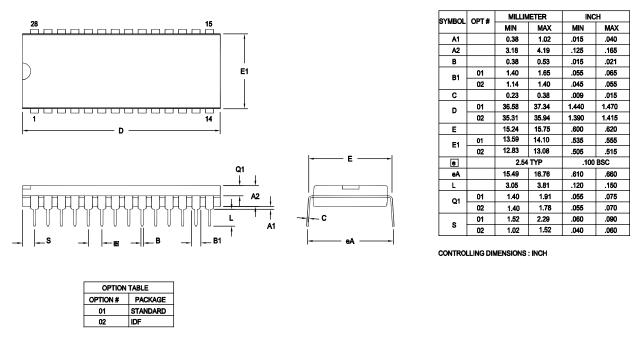

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

| Part Number                                                       | F     |       | /O Lines | nterrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |  |

|-------------------------------------------------------------------|-------|-------|----------|-----------|------------------------|---------------------|----------------|---------------------|--|--|--|

| Part                                                              | Flash | RAM   | 10 L     | Inter     | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |  |  |  |

| Z8 Encore! XP with 1 KB Flash, 10-Bit Analog-to-Digital Converter |       |       |          |           |                        |                     |                |                     |  |  |  |

| Standard Temperature: 0 °C to 70 °C                               |       |       |          |           |                        |                     |                |                     |  |  |  |

| Z8F0123PB005SC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0123QB005SC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0123SB005SC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0123SH005SC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0123HH005SC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0123PH005SC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0123SJ005SC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0123HJ005SC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0123PJ005SC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Extended Temperature: -40 °C to 105 °C                            |       |       |          |           |                        |                     |                |                     |  |  |  |

| Z8F0123PB005EC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |  |

| Z8F0123QB005EC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |  |

| Z8F0123SB005EC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |  |

| Z8F0123SH005EC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |  |

| Z8F0123HH005EC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |  |

| Z8F0123PH005EC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |  |

| Z8F0123SJ005EC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |  |

| Z8F0123HJ005EC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |  |

| Z8F0123PJ005EC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |  |

| Replace C with G for Lead-Free Packaging                          |       |       |          |           |                        |                     |                |                     |  |  |  |

223