Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113ph005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date             | Revision<br>Level | Description                                                                                                                                                                                                       | Page No                              |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| March<br>2008    | 14                | Changed title to Z8 Encore! XP F0823 Series and the contents to match the title.                                                                                                                                  | •                                    |

| December<br>2007 | 13                | Updated title from Z8 Encore! 8K and 4K Series to Z8<br>Encore! XP Z8F0823 Series. Updated Figure 3, Table<br>15, Table 35, Table 59 through Table 61, Table 119,<br>and Part Number Suffix Designations section. | 8, 39,<br>59, 91,<br>196, and<br>226 |

| August<br>2007   | 12                | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                                            | 2, 42,<br>and 13                     |

| June 2007        | 11                | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                                        | All                                  |

| December<br>2006 | 10                | Updated Ordering Information chapter.                                                                                                                                                                             | 217                                  |

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Operation                                               | 152 |

|---------------------------------------------------------|-----|

| OCD Interface                                           |     |

|                                                         |     |

| OCD Data FormatOCD Data Format                          |     |

| OCD Serial Errors                                       |     |

| OCD Unlock Sequence (8-Pin Devices Only)                |     |

| Breakpoints                                             |     |

| Runtime Counter                                         | 156 |

| On-Chip Debugger Commands                               | 157 |

| On-Chip Debugger Control Register Definitions           | 161 |

| OCD Control Register                                    |     |

| OCD Status Register                                     | 163 |

| Oscillator Control                                      |     |

| Operation                                               |     |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Oscillator Control Register Definitions                 |     |

| Internal Precision Oscillator                           |     |

| Operation                                               |     |

| eZ8 CPU Instruction Set                                 |     |

| Assembly Language Programming Introduction              |     |

| Assembly Language Syntax                                |     |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             |     |

| Opcode Maps                                             |     |

| Electrical Characteristics                              | 193 |

| Absolute Maximum Ratings                                | 193 |

| DC Characteristics                                      |     |

| AC Characteristics                                      | 197 |

| On-Chip Peripheral AC and DC Electrical Characteristics |     |

| General Purpose I/O Port Input Data Sample Timing       |     |

| General Purpose I/O Port Output Timing                  |     |

|                                                         |     |

| Packaging                                               |     |

|                                                         |     |

Table of Contents

# Architecture

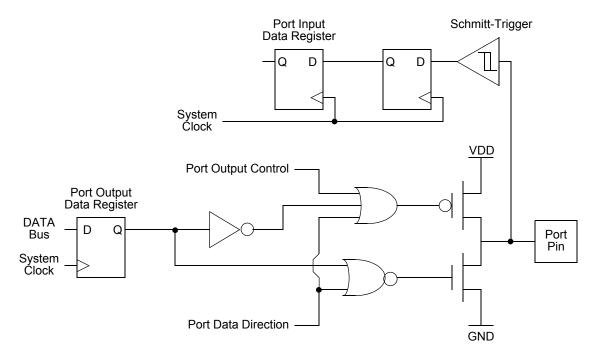

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 7. GPIO Port Pin Block Diagram

# **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function sub-registers configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 15 on page 39 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

| BITS  | 7        | 6                                                                                     | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PAFS17   | PAFS16                                                                                | PAFS15 | PAFS14 | PAFS13 | PAFS12 | PAFS11 | PAFS10 |  |  |  |

| RESET |          | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device)                    |        |        |        |        |        |        |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                                           |        |        |        |        |        |        |  |  |  |

| ADDR  | lf 07H i | If 07H in Port A–C Address Register, accessible through the Port A–C Control Register |        |        |        |        |        |        |  |  |  |

Table 26. Port A–C Alternate Function Set 1 Sub-Registers (PxAFS1)

PAFS1[7:0]—Port Alternate Function Set to 1

0 = Port Alternate Function selected as defined in Table 14 (see GPIO Alternate Functions on page 36).

1 = Port Alternate Function selected as defined in Table 14 (see GPIO Alternate Functions on page 36).

#### Port A–C Alternate Function Set 2 Sub-Registers

The Port A–C Alternate Function Set 2 sub-register (Table 27) is accessed through the Port A–C Control register by writing 08H to the Port A–C Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 14 in the section GPIO Alternate Functions on page 36.

Table 27. Port A–C Alternate Function Set 2 Sub-Registers (PxAFS2)

| BITS  | 7        | 6                                                                  | 5           | 4             | 3            | 2             | 1            | 0        |  |  |  |

|-------|----------|--------------------------------------------------------------------|-------------|---------------|--------------|---------------|--------------|----------|--|--|--|

| FIELD | PAFS27   | PAFS27 PAFS26 PAFS25 PAFS24 PAFS23 PAFS22 PAFS21 PAFS20            |             |               |              |               |              |          |  |  |  |

| RESET |          | 00H (all ports of 20/28 pin devices); 04H (Port A of 8-pin device) |             |               |              |               |              |          |  |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                        |             |               |              |               |              |          |  |  |  |

| ADDR  | lf 08H i | n Port A–C /                                                       | Address Reg | gister, acces | sible throug | n the Port A- | -C Control F | Register |  |  |  |

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 14 (see GPIO Alternate Functions on page 36).

1 = Port Alternate Function selected as defined in Table 14.

# Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 28) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

0 PIN0 X R

| 10.010 201 |      |      |      | (1, , , , , , , , , , , , , , , , , , , |      |      |      |

|------------|------|------|------|-----------------------------------------|------|------|------|

| BITS       | 7    | 6    | 5    | 4                                       | 3    | 2    | 1    |

| FIELD      | PIN7 | PIN6 | PIN5 | PIN4                                    | PIN3 | PIN2 | PIN1 |

| RESET      | Х    | Х    | Х    | Х                                       | Х    | Х    | Х    |

| R/W        | R    | R    | R    | R                                       | R    | R    | R    |

# Table 28. Port A–C Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low)

1 = Input data is logical 1 (High)

# Port A–C Output Data Register

The Port A–C Output Data register (Table 29) controls the output data to the pins.

FD2H, FD6H, FDAH

#### Table 29. Port A–C Output Data Register (PxOUT)

| BITS  | 7     | 6                           | 5     | 4     | 3     | 2     | 1     | 0     |  |  |

|-------|-------|-----------------------------|-------|-------|-------|-------|-------|-------|--|--|

| FIELD | POUT7 | POUT6                       | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |

| RESET | 0     | 0                           | 0     | 0     | 0     | 0     | 0     | 0     |  |  |

| R/W   | R/W   | R/W R/W R/W R/W R/W R/W R/W |       |       |       |       |       |       |  |  |

| ADDR  |       | FD3H, FD7H, FDBH            |       |       |       |       |       |       |  |  |

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

# LED Drive Enable Register

The LED Drive Enable register (Table 30) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

ADDR

#### Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[ | x] Priority | Description |

|------------|----------|-------------|-------------|

| 1          | 1        | Level 3     | High        |

where x indicates the register bits from 0–7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|-----|------|-------|-----|-------|-------|-------|-------|

| FIELD |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |     |      |       | FC  | 7H    |       |       |       |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|-----|------|-------|-----|-------|-------|-------|-------|

| FIELD |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   |       |

| ADDR  |     |      |       | FC  | 8H    |       |       |       |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

#### Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value.

0000 = ONE-SHOT mode

0001 = CONTINUOUS mode

0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

- 1000 = PWM DUAL OUTPUT mode

- 1001 = CAPTURE RESTART mode

- 1010 = COMPARATOR COUNTER Mode

### **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN to Enable MULTIPROCESSOR mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPROCESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

# **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data register (Table 63). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

#### Table 63. UART Receive Data Register (U0RXD)

| BITS  | 7 | 6               | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-----------------|---|----|----|---|---|---|--|--|

| FIELD |   | RXD             |   |    |    |   |   |   |  |  |

| RESET | Х | X X X X X X X X |   |    |    |   |   |   |  |  |

| R/W   | R | R R R R R R R   |   |    |    |   |   |   |  |  |

| ADDR  |   |                 |   | F4 | 0H |   |   |   |  |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 64 and Table 65) identify the current UART operating configuration and status.

Table 64. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6    | 5  | 4  | 3    | 2    | 1   | 0   |  |  |

|-------|-----|------|----|----|------|------|-----|-----|--|--|

| FIELD | RDA | PE   | OE | FE | BRKD | TDRE | TXE | CTS |  |  |

| RESET | 0   | 0    | 0  | 0  | 0    | 1    | 1   | Х   |  |  |

| R/W   | R   | R    | R  | R  | R    | R    | R   | R   |  |  |

| ADDR  |     | F41H |    |    |      |      |     |     |  |  |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty

1 = There is a byte in the UART Receive Data register

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred

1 = A parity error has occurred

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is

Reserved—0 when read

FSTAT—Flash Controller Status 000000 = Flash Controller locked 000001 = First unlock command received (73H written) 000010 = Second unlock command received (8CH written) 000011 = Flash Controller unlocked 000100 = Sector protect register selected 001xxx = Program operation in progress 010xxx = Page erase operation in progress 100xxx = Mass erase operation in progress

#### Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|-------|---------|-----|-----|-----|------|-----|-----|-----|

| FIELD | INFO_EN |     |     |     | PAGE |     |     |     |

| RESET | 0       | 0   | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W   | R/W     | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| ADDR  |         |     |     | FF  | 9H   |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH

#### PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0.

### **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|--|--|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |  |  |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |  |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |  |

| ADDR  |        | FF9H   |        |        |        |        |        |        |  |  |  |  |

Table 82. Flash Sector Protect Register (FPROT)

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 bytes Flash sector. For the Z8F08x3 devices, the upper 3 bits must be zero. For the Z8F04x3 devices all bits are used. For the Z8F02x3 devices, the upper 4 bits are unused. For the Z8F01x3 devices, the upper 6 bits are unused.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

```

FFREQ[15:0] = FFREQH[7:0],FFREQL[7:0]<sup>*</sup> = System Clock Frequency

1000

```

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG mode. For more details, see OCD Unlock Sequence (8-Pin Devices Only) on page 156.

#### **Exiting DEBUG Mode**

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a system reset

#### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

| START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

|-------|----|----|----|----|----|----|----|----|------|

#### Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open-drain output.

#### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

| Assembly        |                                                                  | Address Mode<br>Opcode(s) |             |           | Fla | ıgs |                           | - Fetch | Instr. |   |        |        |

|-----------------|------------------------------------------------------------------|---------------------------|-------------|-----------|-----|-----|---------------------------|---------|--------|---|--------|--------|

| Mnemonic        | Symbolic Operation                                               | dst                       | src         | (Hex)     | С   | Ζ   | S                         | v       | D      | Н | Cycles | Cycles |

| RR dst          |                                                                  | R                         |             | E0        | *   | *   | *                         | *       | _      | _ | 2      | 2      |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                             | IR                        |             | E1        | _   |     |                           |         |        |   | 2      | 3      |

| RRC dst         |                                                                  | R                         |             | C0        | *   | *   | *                         | *       | _      | _ | 2      | 2      |

|                 | ► D7D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                              | IR                        |             | C1        | -   |     |                           |         |        |   | 2      | 3      |

| SBC dst, src    | dst mdst – src - C                                               | r                         | r           | 32        | *   | *   | *                         | *       | 1      | * | 2      | 3      |

|                 |                                                                  | r                         | lr          | 33        | -   |     |                           |         |        |   | 2      | 4      |

|                 |                                                                  | R                         | R           | 34        | -   |     |                           |         |        |   | 3      | 3      |

|                 |                                                                  | R                         | IR          | 35        | _   |     |                           |         |        |   | 3      | 4      |

|                 |                                                                  | R                         | IM          | 36        | -   |     |                           |         |        |   | 3      | 3      |

|                 |                                                                  | IR                        | IM          | 37        | -   |     |                           |         |        |   | 3      | 4      |

| SBCX dst, src   | dst mdst – src - C                                               | ER                        | ER          | 38        | *   | *   | *                         | *       | 1      | * | 4      | 3      |

|                 |                                                                  | ER                        | IM          | 39        | -   |     |                           |         |        |   | 4      | 3      |

| SCF             | C m1                                                             |                           |             | DF        | 1   | -   | -                         | _       | _      | _ | 1      | 2      |

| SRA dst         | T V V                                                            | R                         |             | D0        | *   | *   | *                         | 0       | _      | _ | 2      | 2      |

|                 | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR                        |             | D1        |     |     |                           |         |        |   | 2      | 3      |

| SRL dst         | 0 <b>→</b> D7D6D5D4D3D2D1D0 <b>→</b> C                           | R                         |             | 1F C0     | *   | *   | 0                         | *       | _      | _ | 3      | 2      |

|                 | dst                                                              | IR                        |             | 1F C1     |     |     |                           |         |        |   | 3      | 3      |

| SRP src         | RP msrc                                                          |                           | IM          | 01        | -   | -   | -                         | _       | _      | _ | 2      | 2      |

| STOP            | STOP Mode                                                        |                           |             | 6F        | _   | _   | _                         | _       | _      | _ | 1      | 2      |

| SUB dst, src    | dst mdst – src                                                   | r                         | r           | 22        | *   | *   | *                         | *       | 1      | * | 2      | 3      |

|                 |                                                                  | r                         | lr          | 23        | -   |     |                           |         |        |   | 2      | 4      |

|                 |                                                                  | R                         | R           | 24        | -   |     |                           |         |        |   | 3      | 3      |

|                 |                                                                  | R                         | IR          | 25        | -   |     |                           |         |        |   | 3      | 4      |

|                 |                                                                  | R                         | IM          | 26        | _   |     |                           |         |        |   | 3      | 3      |

|                 |                                                                  | IR                        | IM          | 27        | _   |     |                           |         |        |   | 3      | 4      |

| Flags Notation: | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu                   | lt of the o | peration. |     |     | ese <sup>:</sup><br>et to |         | 0      |   |        |        |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

|                     |                                                              | $T_A =$               | = 3.0 V to<br>0 °C to +<br>otherwise | 70 °C      |                           |                                                                                              |  |  |

|---------------------|--------------------------------------------------------------|-----------------------|--------------------------------------|------------|---------------------------|----------------------------------------------------------------------------------------------|--|--|

| Symbol              | Parameter                                                    | Minimum Typical Maxin |                                      | Maximum    | Units                     | Conditions                                                                                   |  |  |

|                     | Resolution                                                   | 10                    |                                      | _          | bits                      |                                                                                              |  |  |

|                     | Differential Nonlinearity<br>(DNL)                           | -1.0                  | -                                    | 1.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> m 3.0 k :                               |  |  |

|                     | Integral Nonlinearity (INL)                                  | -3.0                  | -                                    | 3.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> m3.0 k :                                |  |  |

|                     | Offset Error with Calibration                                |                       | <u>+</u> 1                           |            | LSB <sup>3</sup>          |                                                                                              |  |  |

|                     | Absolute Accuracy with Calibration                           |                       | <u>+</u> 3                           |            | LSB <sup>3</sup>          |                                                                                              |  |  |

| V <sub>REF</sub>    | Internal Reference Voltage                                   | 1.0<br>2.0            | 1.1<br>2.2                           | 1.2<br>2.4 | V                         | REFSEL=01<br>REFSEL=10                                                                       |  |  |

| V <sub>REF</sub>    | Internal Reference<br>Variation with Temperature             |                       | <u>+</u> 1.0                         |            | %                         | Temperature variation<br>with V <sub>DD</sub> = 3.0                                          |  |  |

| V <sub>REF</sub>    | Internal Reference Voltage<br>Variation with V <sub>DD</sub> |                       | <u>+</u> 0.5                         |            | %                         | Supply voltage variation<br>with T <sub>A</sub> = 30 °C                                      |  |  |

| R <sub>REFOUT</sub> | Reference Buffer Output<br>Impedance                         |                       | 850                                  |            | :                         | When the internal<br>reference is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |  |

|                     | Single-Shot Conversion<br>Time                               | -                     | 5129                                 | -          | System<br>clock<br>cycles | All measurements but temperature sensor                                                      |  |  |

|                     |                                                              |                       | 10258                                |            |                           | Temperature sensor<br>measurement                                                            |  |  |

|                     | Continuous Conversion<br>Time                                | -                     | 256                                  | _          | System<br>clock<br>cycles | All measurements but temperature sensor                                                      |  |  |

|                     |                                                              |                       | 512                                  |            |                           | Temperature sensor<br>measurement                                                            |  |  |

|                     | Signal Input Bandwidth                                       | -                     | 10                                   |            | kHz                       | As defined by -3 dB point                                                                    |  |  |

| R <sub>S</sub>      | Analog Source Impedance <sup>4</sup>                         | _                     | _                                    | 10         | k :                       | In unbuffered mode                                                                           |  |  |

### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing

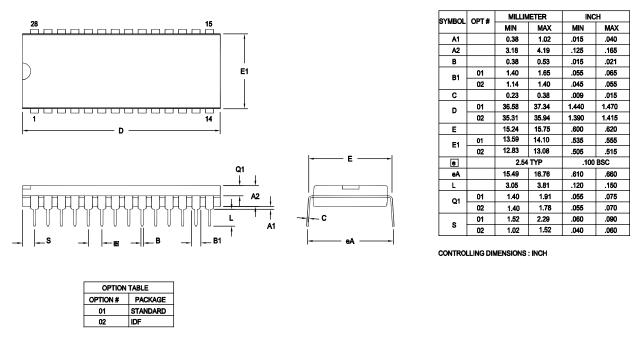

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

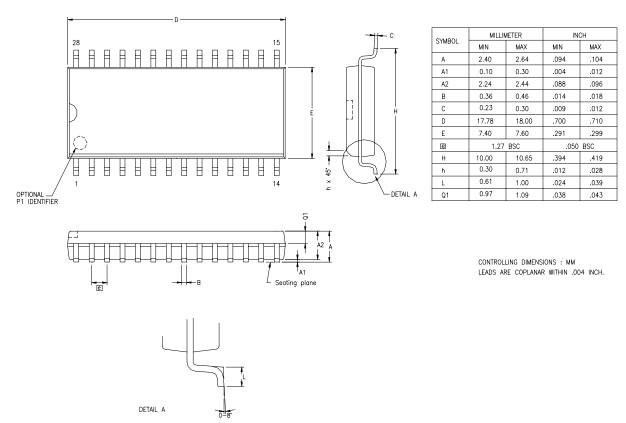

# Figure 41 displays the 28-pin Small Outline Integrated Circuit package (SOIC) available in Z8 Encore! XP F0823 Series devices.

Figure 41. 28-Pin Small Outline Integrated Circuit Package (SOIC)

| mber                     |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |

|--------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number              | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |

| Z8 Encore! XP with 2     | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature     | e: 0 °C to | 70 °C      |           |            |                        |                     |                |                     |

| Z8F0223PB005SC           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SC           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SC           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SC           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SC           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SC           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SC           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SC           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SC           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur      | 'e: -40 °C | to 105 °C  | )         |            |                        |                     |                |                     |

| Z8F0223PB005EC           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EC           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EC           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EC           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EC           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EC           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EC           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EC           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EC           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lea | d-Free Pac | kaging     |           |            |                        |                     |                |                     |

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Index

# Symbols

# 174 % 174 @ 174

# **Numerics**

10-bit ADC 4 40-lead plastic dual-inline package 214, 215

# Α

absolute maximum ratings 193 AC characteristics 197 ADC 175 architecture 117 automatic power-down 118 block diagram 118 continuous conversion 120 control register 122, 124 control register definitions 122 data high byte register 124 data low bits register 125 electrical characteristics and timing 201 operation 118 single-shot conversion 119 ADCCTL register 122, 124 ADCDH register 124 ADCDL register 125 ADCX 175 ADD 175 add - extended addressing 175 add with carry 175 add with carry - extended addressing 175 additional symbols 174 address space 13 ADDX 175 analog signals 10 analog-to-digital converter (ADC) 117 AND 177

ANDX 177 arithmetic instructions 175 assembly language programming 171 assembly language syntax 172

# В

B 174 b 173 baud rate generator, UART 103 **BCLR 176** binary number suffix 174 **BIT 176** bit 173 clear 176 manipulation instructions 176 set 176 set or clear 176 swap 176 test and jump 178 test and jump if non-zero 178 test and jump if zero 178 bit jump and test if non-zero 178 bit swap 178 block diagram 3 block transfer instructions 176 **BRK 178 BSET 176** BSWAP 176, 178 **BTJ 178 BTJNZ 178 BTJZ 178**

# С

CALL procedure 178 CAPTURE mode 84, 85 CAPTURE/COMPARE mode 85 cc 173 CCF 176 characteristics, electrical 193 clear 177 CLR 177 COM 177 227