Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | ·                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113qb005sc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Warning:** DO NOT USE IN LIFE SUPPORT

### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| On-Chip Debugger Initiated Reset                    | 26 |

|-----------------------------------------------------|----|

| Stop Mode Recovery                                  |    |

| Stop Mode Recovery Using Watchdog Timer Time-Out    |    |

| Stop Mode Recovery Using a GPIO Port Pin Transition |    |

| Stop Mode Recovery Using the External RESET Pin     |    |

| Reset Register Definitions                          |    |

| Low-Power Modes                                     |    |

| STOP Mode                                           |    |

| HALT Mode                                           |    |

| Peripheral-Level Power Control                      | 32 |

| Power Control Register Definitions                  | 32 |

| General-Purpose Input/Output                        | 35 |

| GPIO Port Availability By Device                    | 35 |

| Architecture                                        | 36 |

| GPIO Alternate Functions                            | 36 |

| Direct LED Drive                                    | 37 |

| Shared Reset Pin                                    | 37 |

| Shared Debug Pin                                    | 37 |

| Crystal Oscillator Override                         | 38 |

| 5 V Tolerance                                       |    |

| External Clock Setup                                |    |

| GPIO Interrupts                                     |    |

| GPIO Control Register Definitions                   |    |

| Port A–C Address Registers                          |    |

| Port A–C Control Registers                          |    |

| Port A–C Data Direction Sub-Registers               | 45 |

| Port A–C Alternate Function Sub-Registers           |    |

| Port A–C Input Data Registers                       |    |

| Port A–C Output Data Register                       |    |

|                                                     |    |

| LED Drive Level High Register                       |    |

|                                                     |    |

| Interrupt Controller                                |    |

| Interrupt Vector Listing                            |    |

| Architecture                                        |    |

| Operation                                           |    |

| IVIASIEI IIIIEIIUPI LIIAVIE                         | 00 |

# **Pin Description**

Z8 Encore! XP<sup>®</sup> F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information on physical package specifications, see Packaging on page 209.

## **Available Packages**

Table 2 lists the package styles that are available for each device in the Z8 Encore! XP F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | X             | X             | X              | X              | X              | X              | X              | X              | X                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. Z8 Encore! XP F0823 Series Package Options

## **Pin Configurations**

Figure 2 through Figure 4 displays the pin configurations for all packages available in the Z8 Encore! XP F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANA*x*) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

# **Register Map**

Table 8 lists the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0823 Series devices. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, or all GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page No   |

|----------------|-----------------------------------|---------------|-------------|-----------|

| General-Purpos | <u> </u>                          |               |             | 1 490 110 |

| Z8F0823/Z8F08  |                                   |               |             |           |

|                |                                   |               | ~~~         |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | _             | XX          |           |

| Z8F0423/Z8F04  |                                   |               |             |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | —             | XX          |           |

| Z8F0223/Z8F02  | 13 Devices                        |               |             |           |

| 000–1FF        | General-Purpose Register File RAM | —             | XX          |           |

| 200–EFF        | Reserved                          | —             | XX          |           |

| Z8F0123/Z8F01  | 13 Devices                        |               |             |           |

| 000–0FF        | General-Purpose Register File RAM | _             | XX          |           |

| 100–EFF        | Reserved                          | _             | XX          |           |

| Timer 0        |                                   |               |             |           |

| F00            | Timer 0 High Byte                 | ТОН           | 00          | 80        |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | 80        |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | 81        |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | 81        |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | 81        |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | 82        |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | 82        |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | 83        |

| Timer 1        |                                   |               |             |           |

| F08            | Timer 1 High Byte                 | T1H           | 00          | 80        |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | 80        |

| F0A            | Timer 1 Reload High Byte          | T1RH          | FF          | 81        |

| F0B            | Timer 1 Reload Low Byte           | T1RL          | FF          | 81        |

## Table 19. Port A–C Control Registers (PxCTL)

| BITS  | 7   | 6                           | 5 | 4        | 3        | 2 | 1 | 0 |  |  |

|-------|-----|-----------------------------|---|----------|----------|---|---|---|--|--|

| FIELD |     | PCTL                        |   |          |          |   |   |   |  |  |

| RESET |     |                             |   | 00       | )H       |   |   |   |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |          |          |   |   |   |  |  |

| ADDR  |     |                             |   | FD1H, FD | 5H, FD9H |   |   |   |  |  |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

## Port A-C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address register (Table 20).

| BITS  | 7        | 6          | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|----------|------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | DD7      | DD6        | DD5         | DD4           | DD3          | DD2           | DD1          | DD0      |

| RESET | 1        | 1          | 1           | 1             | 1            | 1             | 1            | 1        |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W          | R/W           | R/W          | R/W      |

| ADDR  | lf 01H i | n Port A–C | Address Reg | gister, acces | sible throug | n the Port A- | -C Control F | Register |

## Table 20. Port A–C Data Direction Sub-Registers (PxDD)

DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–C Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tristated.

# Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 21) is accessed through the Port A–C Control register by writing 02H to the Port A–C Address register. The Port A–C Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–C Alternate Function Set 1 Sub-Registers on page 48 and Port A–C Alternate Function Set 2 Sub-Registers on

# **Infrared Encoder/Decoder**

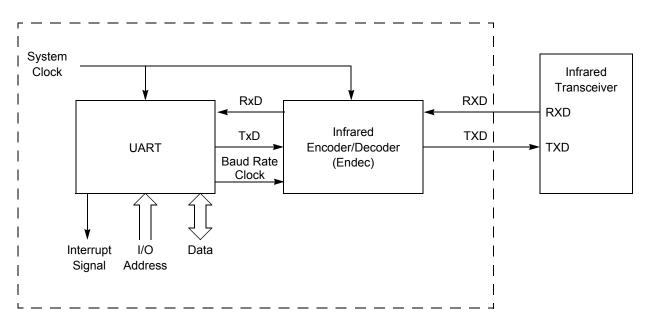

Z8 Encore! XP<sup>®</sup> F0823 Series products contain a fully-functional, high-performance UART with Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

# Architecture

Figure 16 displays the architecture of the Infrared Endec.

Figure 16. Infrared Data Communication System Block Diagram

# Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared

## **Receiving IrDA Data**

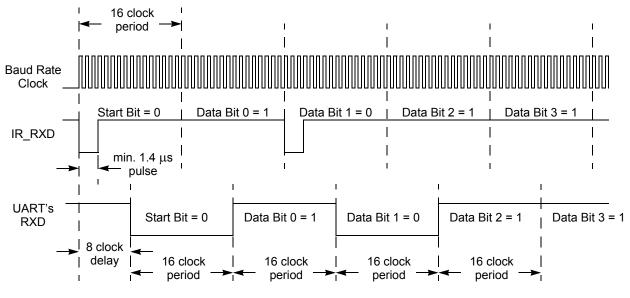

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the 1.4 μs minimum width pulses allowed by the IrDA standard.

### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

### 118

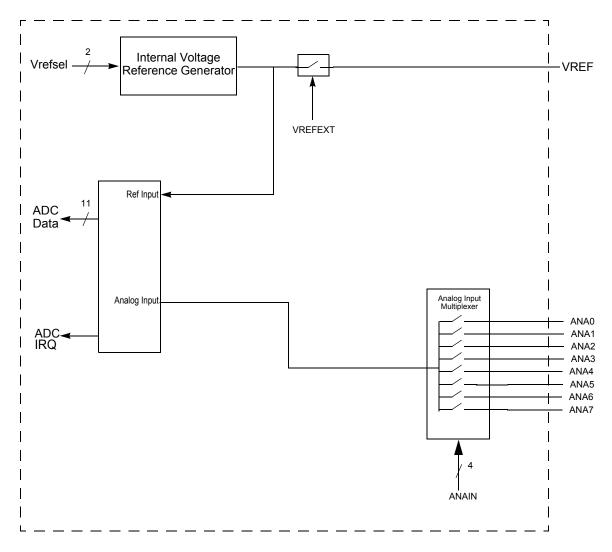

Figure 19. Analog-to-Digital Converter Block Diagram

## Operation

## **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

## **ADC Control/Status Register 1**

The second ADC Control register contains the voltage reference level selection bit.

### Table 73. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7       | 6   | 5                       | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---------|-----|-------------------------|----|----|---|---|---|--|--|

| FIELD | REFSELH |     | Reserved                |    |    |   |   |   |  |  |

| RESET | 1       | 0   | 0                       | 0  | 0  | 0 | 0 | 0 |  |  |

| R/W   | R/W     | R/W | R/W R/W R/W R/W R/W R/W |    |    |   |   |   |  |  |

| ADDR  |         |     |                         | F7 | 1H |   |   |   |  |  |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

## ADC Data High Byte Register

The ADC Data High Byte register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data High Byte Register (ADCD\_H)

| BITS  | 7 | 6     | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-------|---|----|----|---|---|---|--|--|

| FIELD |   | ADCDH |   |    |    |   |   |   |  |  |

| RESET | Х | Х     | Х | Х  | Х  | Х | Х | Х |  |  |

| R/W   | R | R     | R | R  | R  | R | R | R |  |  |

| ADDR  |   |       |   | F7 | 2H |   |   |   |  |  |

### ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

# **Flash Memory**

The products in Z8 Encore! XP<sup>®</sup> F0823 Series features either 8 KB (8192), 4 KB (4096), 2 KB (2048) or 1 KB (1024) of non-volatile Flash memory with read/write/erase capability. Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash Memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program/data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F0823 Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes in size (all other memory sizes); each sector maps to a page. Page and sector sizes are not generally equal.

The first two bytes of the Flash Program memory are used as Flash Option Bits. For more information on their operation, see Flash Option Bits on page 141.

Table 77 describes the Flash memory configuration for each device in the Z8 Encore! XP F0823 Series. Figure 20 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08x3     | 8 (8192)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F04x3     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02x3     | 2 (2048)                 | 4              | 0000H–07FFH                 | 512                          |

| Z8F01x3     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

#### Table 77. Z8 Encore! XP F0823 Series Flash Memory Configurations

## Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32 kHz (32768 Hz) through 20 MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32 kHz (32768 Hz) or above 20 MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of Z8 Encore! XP<sup>®</sup> F0823 Series devices.

### Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access with the On-Chip Debugger. Programming the FRP Flash Option Bit prevents reading of the user code with the On-Chip Debugger. For more information, see Flash Option Bits on page 141 and On-Chip Debugger on page 151.

## Flash Code Protection Against Accidental Program and Erasure

Z8 Encore! XP F0823 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 78. For more information, see Flash Option Bits on page 141.

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- $0 = Crystal \ oscillator \ is \ enabled \ during \ reset, \ resulting \ in \ longer \ reset \ timing$

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

## Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS        | 7                             | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------------|-------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|--|--|

| FIELD       | Reserved                      |              |              |     |     |     |     |     |  |  |  |

| RESET       | U                             | U            | U            | U   | U   | U   | U   | U   |  |  |  |

| R/W         | R/W                           | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR        | Information Page Memory 0020H |              |              |     |     |     |     |     |  |  |  |

| Note: U = U | Jnchanged b                   | y Reset. R/W | = Read/Write | 9.  |     |     |     |     |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

## Trim Bit Address 0001H—Reserved

### Table 90. Trim Option Bits at 0001H

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| FIELD     | Reserved                                        |     |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Information Page Memory 0021H                   |     |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |

# **On-Chip Debugger**

Z8 Encore! XP<sup>®</sup> F0823 Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features that include:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize the pins available

# Architecture

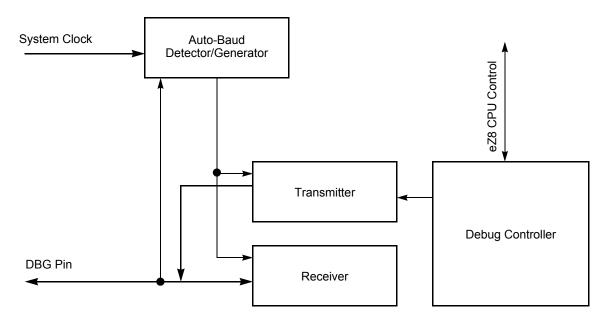

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 22 displays the architecture of the OCD.

Figure 22. On-Chip Debugger Block Diagram

datastreams, the maximum recommended baud rate is the system clock frequency divided by eight. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by four, but this theoretical maximum is possible only for low noise designs with clean signals. Table 98 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended<br>Maximum Baud<br>Rate (kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (kbps) |  |  |

|---------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|--|--|

| 5.5296                          | 1382.4                                     | 691,200                                       | 1.08                        |  |  |

| 0.032768 (32 kHz)               | 4.096                                      | 2400                                          | 0.064                       |  |  |

#### Table 98. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the auto-baud detector/generator resets. Reconfigure the auto-baud detector/generator by sending 80H.

### **OCD Serial Errors**

The OCD detects any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the auto-baud detector/generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F0823 Series devices or when recovering from an error. A Serial Break from the host resets the auto-baud generator/detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host sends a Serial Break to the OCD even if the OCD is transmitting a character.

### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

## **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control register.

### **Oscillator Control Register**

The Oscillator Control register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6        | 5     | 4     | 3     | 2           | 1 | 0 |  |  |  |

|-------|-------|----------|-------|-------|-------|-------------|---|---|--|--|--|

| FIELD | INTEN | Reserved | WDTEN | POFEN | WDFEN | SCKSEL      |   |   |  |  |  |

| RESET | 1     | 0        | 1     | 0     | 0     | 0           | 0 | 0 |  |  |  |

| R/W   | R/W   | R/W      | R/W   | R/W   | R/W   | R/W R/W R/W |   |   |  |  |  |

| ADDR  |       | F86H     |       |       |       |             |   |   |  |  |  |

Table 102. Oscillator Control Register (OSCCTL)

### Table 110. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |  |  |  |  |  |  |

|----------|----------|------------------------|--|--|--|--|--|--|

| SCF      | —        | Set Carry Flag         |  |  |  |  |  |  |

| SRP      | SrC      | Set Register Pointer   |  |  |  |  |  |  |

| STOP     | _        | STOP Mode              |  |  |  |  |  |  |

| WDT      | _        | Watchdog Timer Refresh |  |  |  |  |  |  |

### Table 111. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                    |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | SrC         | Push                                                                   |

| PUSHX    | SrC         | Push using Extended Addressing                                         |

## Table 112. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| СОМ      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

| 184 |  |

|-----|--|

|-----|--|

| Assembly        |                                                                 | Addre   | ss Mode     | -<br>Opcode(s) | Flags |   |              |   |   |   | - Fetch | Instr  |

|-----------------|-----------------------------------------------------------------|---------|-------------|----------------|-------|---|--------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                              | dst     | src         | (Hex)          | С     | Ζ | S            | v | D | н |         | Cycles |

| OR dst, src     | $dst \gets dst \: OR \: src$                                    | r       | r           | 42             | _     | * | *            | 0 | _ | _ | 2       | 3      |

|                 |                                                                 | r       | lr          | 43             | -     |   |              |   |   |   | 2       | 4      |

|                 |                                                                 | R       | R           | 44             | -     |   |              |   |   |   | 3       | 3      |

|                 |                                                                 | R       | IR          | 45             | _     |   |              |   |   |   | 3       | 4      |

|                 |                                                                 | R       | IM          | 46             | -     |   |              |   |   |   | 3       | 3      |

|                 |                                                                 | IR      | IM          | 47             | -     |   |              |   |   |   | 3       | 4      |

| ORX dst, src    | $dst \gets dst \: OR \: src$                                    | ER      | ER          | 48             | -     | * | *            | 0 | _ | - | 4       | 3      |

|                 |                                                                 | ER      | IM          | 49             | _     |   |              |   |   |   | 4       | 3      |

| POP dst         | dst ← @SP                                                       | R       |             | 50             | _     | _ | _            | _ | _ | _ | 2       | 2      |

|                 | $SP \leftarrow SP + 1$                                          | IR      |             | 51             | -     |   |              |   |   |   | 2       | 3      |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                        | ER      |             | D8             | -     | _ | _            | _ | _ | - | 3       | 2      |

| PUSH src        | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                  | R       |             | 70             | _     | _ |              | _ | - | _ | 2       | 2      |

|                 |                                                                 | IR      |             | 71             | -     | - |              |   |   |   | 2       | 3      |

|                 |                                                                 | IM      |             | IF70           | _     |   |              |   |   |   | 3       | 2      |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER      |             | C8             | _     | _ | _            | _ | _ | _ | 3       | 2      |

| RCF             | C ← 0                                                           |         |             | CF             | 0     | _ | -            | _ | _ | _ | 1       | 2      |

| RET             | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |         |             | AF             | _     | - | -            | _ | _ | _ | 1       | 4      |

| RL dst          |                                                                 | R       |             | 90             | *     | * | *            | * | - | _ | 2       | 2      |

|                 | C D7 D6 D5 D4 D3 D2 D1 D0<br>dst                                | IR      |             | 91             | -     |   |              |   |   |   | 2       | 3      |

| RLC dst         |                                                                 | R       |             | 10             | *     | * | *            | * | _ | _ | 2       | 2      |

|                 | C D7D6D5D4D3D2D1D0                                              | IR      | IR 11       |                |       |   |              |   |   |   | 2       | 3      |

| Flags Notation: | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he resu | It of the c | operation.     |       |   | ese<br>et to |   | 0 |   |         |        |

### Table 115. eZ8 CPU Instruction Summary (Continued)

# **On-Chip Peripheral AC and DC Electrical Characteristics**

## Table 122. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C       |          |                                                                                                       |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|--------------|----------|-------------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum      | Units    | Conditions                                                                                            |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70         | V        | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65         | V        | $V_{DD} = V_{VBO}$                                                                                    |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75           | mV       |                                                                                                       |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | _                  | V <sub>SS</sub>      | -            | V        |                                                                                                       |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -            | μs       | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                                                             |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles                                                            |

| Τ <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | _            | μs       | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100          | ms       |                                                                                                       |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |              | ns       | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |

|                   | he typical column is from char are not tested in production.                                                   | acterization       | at 3.3 V and         | 30 °C. These | values a | re provided for design guidance                                                                       |

199

| Part Number              | F           |           | ines      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part                     | Flash       | RAM       | I/O Lines | Inter      | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |

| Z8 Encore! XP with 8     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0813PB005SC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005SC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005SC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005SC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005SC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005SC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005SC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005SC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005SC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu       | re: -40 °C  | to 105 °( | 0         |            |                        |                     |                |                     |

| Z8F0813PB005EC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005EC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005EC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005EC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005EC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005EC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005EC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005EC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005EC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lea | ad-Free Pac | kaging    |           |            |                        |                     |                |                     |

## Т

**TCM 176 TCMX 176** test complement under mask 176 test complement under mask - extended addressing 176 test under mask 176 test under mask - extended addressing 176 timer signals 9 timers 67 architecture 67 block diagram 67 CAPTURE mode 74, 75, 84, 85 CAPTURE/COMPARE mode 78, 85 COMPARE mode 76, 84 CONTINUOUS mode 69, 84 COUNTER mode 70, 71 COUNTER modes 84 GATED mode 77, 84 ONE-SHOT mode 68, 84 operating mode 68 PWM mode 72, 73, 84, 85 reading the timer count values 79 reload high and low byte registers 80 timer control register definitions 80 timer output signal operation 79 timers 0-3 control registers 82, 83 high and low byte registers 80, 81 TM 176 TMX 176 tools, hardware and software 226 transmit IrDA data 114 transmitting UART data-polled method 95 transmitting UART dat-interrupt-driven method 96 **TRAP 178**

## U

UART 4 architecture 93 baud rate generator 103

control register definitions 104 controller signals 9 data format 94 interrupts 101 MULTIPROCESSOR mode 99 receiving data using interrupt-driven method 98 receiving data using the polled method 97 transmitting data using the interrupt-driven method 96 transmitting data using the polled method 95 x baud rate high and low registers 110 x control 0 and control 1 registers 107 x status 0 and status 1 registers 105, 106 **UxBRH** register 110 UxBRL register 110 UxCTL0 register 107, 110 UxCTL1 register 108 UxRXD register 105 UxSTAT0 register 105 UxSTAT1 register 106 UxTXD register 104

# V

vector 173 Voltage Brownout reset (VBR) 24

## W

Watchdog Timer approximate time-out delay 87 CNTL 24 control register 89, 127, 167 electrical characteristics and timing 200, 202 interrupt in normal operation 88 interrupt in STOP mode 88 refresh 88, 177 reload unlock sequence 89 reload upper, high and low registers 90 reset 25 reset in normal operation 89