Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113sb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- 2.7 V to 3.6 V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore! XP<sup>®</sup> F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

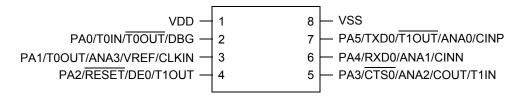

#### Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

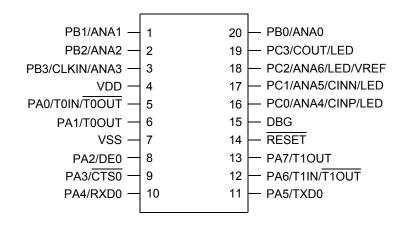

### Figure 3. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package\*

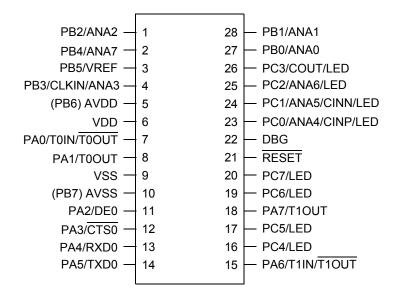

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

10

| Signal Mnemonic                                      | I/O | Description                                                                                                                                                                                                           |

|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog                                               |     |                                                                                                                                                                                                                       |

| ANA[7:0]                                             | Ι   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                                                 | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                                          |     |                                                                                                                                                                                                                       |

| CLKIN                                                | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                                          |     |                                                                                                                                                                                                                       |

| LED                                                  | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger                                     |     |                                                                                                                                                                                                                       |

| DBG                                                  | I/O | Debug. This signal is the control and data input and output to and from the OCD.                                                                                                                                      |

|                                                      |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull                                                                                                                                               |

|                                                      |     | up resistor to ensure proper operation.                                                                                                                                                                               |

| Reset                                                |     |                                                                                                                                                                                                                       |

| RESET                                                | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                                         |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>                                      | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub>                                     | Ι   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>                                      | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>                                     | I   | Analog Ground.                                                                                                                                                                                                        |

| Note: The AV <sub>DD</sub> and A<br>PB7 on 28-pin pa |     | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and without ADC.                                                                                                                        |

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA5 | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         |                                         |

### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

50

0 PIN0 X R

| 10.010 201 |      |      |      | (1, , , , , , , , , , , , , , , , , , , |      |      |      |

|------------|------|------|------|-----------------------------------------|------|------|------|

| BITS       | 7    | 6    | 5    | 4                                       | 3    | 2    | 1    |

| FIELD      | PIN7 | PIN6 | PIN5 | PIN4                                    | PIN3 | PIN2 | PIN1 |

| RESET      | Х    | Х    | Х    | Х                                       | Х    | Х    | Х    |

| R/W        | R    | R    | R    | R                                       | R    | R    | R    |

# Table 28. Port A–C Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low)

1 = Input data is logical 1 (High)

# Port A–C Output Data Register

The Port A–C Output Data register (Table 29) controls the output data to the pins.

FD2H, FD6H, FDAH

### Table 29. Port A–C Output Data Register (PxOUT)

| BITS  | 7                | 6     | 5     | 4     | 3     | 2     | 1     | 0     |

|-------|------------------|-------|-------|-------|-------|-------|-------|-------|

| FIELD | POUT7            | POUT6 | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET | 0                | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| ADDR  | FD3H, FD7H, FDBH |       |       |       |       |       |       |       |

### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

# LED Drive Enable Register

The LED Drive Enable register (Table 30) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

ADDR

| BITS  | 7    | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|-------|------|------|-------|-----|------|------|------|------|

| FIELD |      | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0    | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  | FC6H |      |       |     |      |      |      |      |

### Table 36. Interrupt Request 2 Register (IRQ2)

Reserved—Must be 0

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x

1 = An interrupt request from GPIO Port C pin x is awaiting service

where x indicates the specific GPIO Port C pin number (0-3)

# **IRQ0 Enable High and Low Bit Registers**

Table 37 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 38 and Table 39) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register.

| -          |            |          |             |

|------------|------------|----------|-------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

### Table 38. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6     | 5     | 4      | 3      | 2        | 1        | 0      |

|-------|----------|-------|-------|--------|--------|----------|----------|--------|

| FIELD | Reserved | T1ENH | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |

| RESET | 0        | 0     | 0     | 0      | 0      | 0        | 0        | 0      |

| R/W   | R/W      | R/W   | R/W   | R/W    | R/W    | R/W      | R/W      | R/W    |

| ADDR  | FC1H     |       |       |        |        |          |          |        |

| BITS  | 7    | 6 | 5           | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|---|-------------|----|----|---|---|---|--|--|

| FIELD | IRQE |   | Reserved    |    |    |   |   |   |  |  |

| RESET | 0    | 0 | 0 0 0 0 0 0 |    |    |   |   |   |  |  |

| R/W   | R/W  | R | R R R R R R |    |    |   |   |   |  |  |

| ADDR  |      |   |             | FC | FH |   |   |   |  |  |

## Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP<sup>®</sup> F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! XP F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 57 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

### Table 57. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value |            | e Time-Out Delay<br>VDT oscillator frequency) |

|------------------|------------------|------------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical    | Description                                   |

| 000004           | 4                | 400 μs     | Minimum time-out delay                        |

| FFFFF            | 16,777,215       | 28 minutes | Maximum time-out delay                        |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP<sup>®</sup> F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

| Table 78. Flash Code Pr | rotection Using  | the Flash O | ntion Bits |

|-------------------------|------------------|-------------|------------|

|                         | olection bailing | the mash o  |            |

| FWP | Flash Code Protection Description                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code programming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                           |

### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total size of the Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal.

The Sector Protect Register controls the protection state of each Flash sector. This register is shared with the Page Select Register. It is accessed by writing 73H followed by 5EH to the Flash controller. The next write to the Flash Control Register targets the Sector Protect Register.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After

a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

### Byte Programming

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming is accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

### Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

### Table 95. Serialization Data Locations

| Info Page<br>Address | Memory Address | Usage                                    |

|----------------------|----------------|------------------------------------------|

| 1C                   | FE1C           | Serial Number Byte 3 (most significant)  |

| 1D                   | FE1D           | Serial Number Byte 2                     |

| 1E                   | FE1E           | Serial Number Byte 1                     |

| 1F                   | FE1F           | Serial Number Byte 0 (least significant) |

# **Randomized Lot Identifier**

### Table 96. Lot Identification Number (RAND\_LOT)

| BITS      | 7                                               | 6            | 5            | 4          | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------------------------|--------------|--------------|------------|-----|-----|-----|-----|--|--|--|--|

| FIELD     | RAND_LOT                                        |              |              |            |     |     |     |     |  |  |  |  |

| RESET     | U                                               |              |              |            |     |     |     |     |  |  |  |  |

| R/W       | R/W                                             | R/W          | R/W          | R/W        | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR      | Interspersed throughout Information Page Memory |              |              |            |     |     |     |     |  |  |  |  |

| Note: U = | Unchanged by                                    | y Reset. R/W | = Read/Write | <b>)</b> . |     |     |     |     |  |  |  |  |

RAND LOT-Randomized Lot ID

The randomized lot ID is a 32 byte binary value that changes for each production lot.

### Table 97. Randomized Lot ID Locations

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG mode. For more details, see OCD Unlock Sequence (8-Pin Devices Only) on page 156.

### Exiting DEBUG Mode

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a system reset

### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

| <br>STADT | 00 | D1 | 50 | 50 | D4 | DE | D6 | D7 | STOD |

|-----------|----|----|----|----|----|----|----|----|------|

| STAN      | DU | Ы  | DZ | 05 | D4 | 5  | DU | ы  | 5101 |

### Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open-drain output.

### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

|   |                           |                            |                              |                                |                            |                             | Lo                            | ower Nil                       | oble (He                      | x)                             |                            |                          |                    |                           |                  |                          |

|---|---------------------------|----------------------------|------------------------------|--------------------------------|----------------------------|-----------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|--------------------|---------------------------|------------------|--------------------------|

|   | 0                         | 1                          | 2                            | 3                              | 4                          | 5                           | 6                             | 7                              | 8                             | 9                              | А                          | В                        | С                  | D                         | Е                | F                        |

| 0 | 1.1<br>BRK                | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br>LD<br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                    |                           |                  | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1          | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br><b>SUB</b><br>IR1,IM    | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1, 2<br>ATM              |

| 3 | 2.2<br>DEC<br>R1          | 2.3<br><b>DEC</b><br>IR1   | 2.3<br><b>SBC</b><br>r1,r2   | 2.4<br><b>SBC</b><br>r1,lr2    | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br><b>SBC</b><br>IR2,R1 | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                    |                           |                  |                          |

| 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                    |                           |                  |                          |

| 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                    |                           |                  | 1.2<br>WDT               |

| 6 | 2.2<br>COM<br>R1          | 2.3<br>COM<br>IR1          | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.2<br>STOP              |

| 7 | 2.2<br>PUSH<br>R2         | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>HALT              |

| 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,Irr2 | 2.9<br><b>LDEI</b><br>Ir1,Irr2 | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>lr1,ER2       | 3.4<br>LDX<br>IRR2,R1         | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                    |                           |                  | 1.2<br>DI                |

| 9 | 2.2<br><b>RL</b><br>R1    | 2.3<br><b>RL</b><br>IR1    | 2.5<br><b>LDE</b><br>r2,Irr1 | 2.9<br><b>LDEI</b><br>Ir2,Irr1 | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>lr2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br><b>LDX</b><br>IR2,IRR1  | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                    |                           |                  | 1.2<br>El                |

| А | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.4<br>RET               |

| В | 2.2<br>CLR<br>R1          | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br>XORX<br>IM,ER1          |                            |                          |                    |                           |                  | 1.5<br>IRET              |

| С | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,Irr2 | 2.9<br>LDCI<br>Ir1,Irr2        | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>lr1,lrr2      |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                    |                           |                  | 1.2<br>RCF               |

| D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                    |                           |                  | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1         | 2.3<br><b>SWAP</b><br>IR1  | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | V                          | V                        | ▼                  | ♥                         | ▼                |                          |

Figure 27. First Opcode Map

190

Upper Nibble (Hex)

### Table 117. Absolute Maximum Ratings (Continued)

| Parameter                                                      | Minimum Maximum | Units | Notes |

|----------------------------------------------------------------|-----------------|-------|-------|

| Maximum current into $V_{\text{DD}}$ or out of $V_{\text{SS}}$ | 125             | mA    |       |

|                                                                |                 |       |       |

Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 118 lists the DC characteristics of the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F0823 Series products. All voltages are referenced to V<sub>SS</sub>, the primary system ground.

### Table 118. DC Characteristics

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | _                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | _                      | -                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                               |

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **Ordering Information**

| Part Number              | Flash      | RAM       | . I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------|------------|-----------|-------------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP with 8     |            |           | Analog      | j-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperatur      |            |           |             | 10         | <u> </u>               | 4                   | 4              |                     |

| Z8F0823PB005SC           | 8 KB       | 1 KB      | 6           | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005SC           | 8 KB       | 1 KB      | 6           | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005SC           | 8 KB       | 1 KB      | 6           | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005SC           | 8 KB       | 1 KB      | 16          | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005SC           | 8 KB       | 1 KB      | 16          | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005SC           | 8 KB       | 1 KB      | 16          | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005SC           | 8 KB       | 1 KB      | 22          | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005SC           | 8 KB       | 1 KB      | 22          | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005SC           | 8 KB       | 1 KB      | 22          | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur      | re: -40 °C | to 105 °0 | 0           |            |                        |                     |                |                     |

| Z8F0823PB005EC           | 8 KB       | 1 KB      | 6           | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005EC           | 8 KB       | 1 KB      | 6           | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005EC           | 8 KB       | 1 KB      | 6           | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005EC           | 8 KB       | 1 KB      | 16          | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005EC           | 8 KB       | 1 KB      | 16          | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005EC           | 8 KB       | 1 KB      | 16          | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005EC           | 8 KB       | 1 KB      | 22          | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005EC           | 8 KB       | 1 KB      | 22          | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005EC           | 8 KB       | 1 KB      | 22          | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lea | d-Free Pac | kaging    |             |            |                        |                     |                |                     |