# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113sh005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Internal Precision Oscillator

The internal precision oscillator (IPO)astrimmable clock source that requires no external components.

## 10-Bit Analog-to-Dig ital Converter

The optional analog-to-digital **overter** (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from **eigif**ferent analog input pins in both single-ended and differential modes.

### Analog Comparator

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a secopdtipin. The comparator output can be used to drive either an output pipr to generate an interrupt.

## Universal Asynchronous Receiver/Transmitter

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and settlet parity. The UART also supports multidrop address processing in hardware. The UART baud rate generator can be configured and used **as**basic 16-bit timer.

### Timers

Two enhanced 16-bit reloadable timers canused for timing/counting events or for motor control operations. These timers previad16-bit programmable load counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

### Interrupt Controller

Z8 Encore! X<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal perimeral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three level programmable interrupt priority.

memory addresses returnes. Writing to these unimplemented Program Memory addresses produces no effectible 6 describes the Program Merry maps for the Z8 Encore! XP<sup>®</sup> F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

| Z8F0123 and Z8F0113 Products |                          |

| 0000–0001                    | Flash Option Bits        |

|                              |                          |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

| Program Memory Address (Hex)                                            | Function                 |  |  |  |  |

|-------------------------------------------------------------------------|--------------------------|--|--|--|--|

| 0002–0003                                                               | Reset Vector             |  |  |  |  |

| 0004–0005                                                               | WDT Interrupt Vector     |  |  |  |  |

| 0006–0007                                                               | Illegal Instruction Trap |  |  |  |  |

| 0008–0037                                                               | Interrupt Vectors*       |  |  |  |  |

| 0038–003D                                                               | Oscillator Fail Traps*   |  |  |  |  |

| 003E-03FF                                                               | Program Memory           |  |  |  |  |

| *See Table 33 on page 54 for a list of the interrupt vectors and traps. |                          |  |  |  |  |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

# Data Memory

Z8 Encore! X<sup>®</sup> F0823 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# Flash Information Area

Table 7lists the Z8 Encore! XP F0823 SessiFlash Information Area. This 128 B Information Area is accessed softing bit 7 of the Flash Pagelect Register to 1. When access is enabled, the Flash Information Assertapped into the Program Memory and overlays the 128 bytes at addressesson to FF7FH. When the Information Area access is enabled, all reads from these Program Memory data. Accesse return the Information Area is read-only.

Table 7. Z8 Encore! XP F0823 Series Flash Memory Information Area Map

| Program Memory Address<br>(Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

## Table 32. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7            | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|--------------|------|-----|-----|-----|-----|-----|-----|--|

| FIELD | LEDLVLL[7:0] |      |     |     |     |     |     |     |  |

| RESET | 0            | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W          | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |              | F84H |     |     |     |     |     |     |  |

LEDLVLH[7:0]—LED Level High Bit {LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin. 00 = 3 mA

01 = 7 mA10 = 13 mA

11 = 20 mA

#### COMPARATOR COUNTER Mode

In COMPARATOR COUNTER mode timer counts input ansitions from the analog comparator output. The POL bit in the Timer Control Register selects whether the count occurs on the rising edge or the fallied ge of the comparator output signal. In COMPARATOR COUNTER mode, the prescaler is disabled.

Caution: The frequency of the comparator output must not exceed one-fourth the system clock frequency.

After reaching the Reload value stored in Thimer Reload High and Low Byte registers, the timer generates anterrupt, the count value in theriter High and Low Byte registers is reset to 001H and counting resumes. Also, if there output alternate function is enabled, the Timer Output pin changes states Low to High or from High to Low) at timer Reload.

Follow the steps below for configuringimer for COMPARATOR COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CØPARATOR COUNTER mode.

- Select either the rising edge or falling edge comparator output signal for the count. This also sets the initial logic/de (High or Low) for the Timer Output alternate function. However, the Timer toput function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registrs to set the startincount value. This action only affects the first pass in **ODP**ARATOR COUNTER mode. After the first timer Reload in COMPARATOR COUNTER ode, counting always begins at the reset value of 001H. Generally, in COMPARATORCOUNTER mode the Timer High and Low Byte registers resube written with the value001H.

- 3. Write to the Timer Reload High and LoByte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt asset the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions = Current Count Value – Start Value

Watchdog Timer Reload Byte registers (WD,TWDTH, and WDTL) to allow changes to the time-out period. These writeperations to the WDTCTL register address produce no effect on the bits in the WDTCTL register he locking mechanis prevents spurious writes to the Reload registers.

This register address is shared with the read-only Reset Status Register.

| BITS  | 7       | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---------|---|---|---|---|---|---|---|

| FIELD | WDTUNLK |   |   |   |   |   |   |   |

| RESET | Х       | Х | Х | Х | Х | Х | Х | Х |

| R/W   | W       | W | W | W | W | W | W | W |

| ADDR  | FFOH    |   |   |   |   |   |   |   |

Table 58. Watchdog Timer Control Register (WDTCTL)

### WDTUNLK—Watchdog Timer Unlock

The software must write the correct unlocking usence to this register before it is allowed to modify the contents of the Watchdog Timer reload registers.

# Watchdog Timer Reload Upper, High and Low Byte Registers

The Watchdog Timer Reload Upper, Hiand Low Byte (WDTU, WDTH, WDTL) registers (ables 59throughTable 61) form the 24-bit reload value that is loaded into the Watchdog Timer when BDT instruction executes. The 24-bit reload value is {WDTU[7:0], WDTH[7:0], WDTL[7:0]}. Writing to these registers sets the appropriate Reload Value. Reading from these registers registers the current Watchdog Timer count value.

Caution: The 24-bit WDT Reload Value moust be set to a value less theorem 0004H.

- 6. Check the TDRE bit in the UART Status 0 registed determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to p 7 If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 7. Write the UART Control 1 register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmittem (BT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmittat register. The transmitter automatically transfers the data to the Transmittifs hegister and transmits the data.

- 10. Make any changes to tMeultiprocessor Bit Transmittem(₽BT) value, if appropriate and MULTIPROCESSOR mode is enabled,.

- 11. To transmit additional bytes, returnsteep 5

Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the adarbility of the Transmit Data register to accept new data for transmission. Followe sheps below to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Lobyte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configing the associated GPIO port pins for alternate function operation.

- 3. Execute api instruction to disable interrupts.

- 4. Write to the Interrupt control registers enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions, if MULTIPROCESSOR mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (€N) to Enable MULTIPROCESSOR mode.

- 7. Write to the UART Control 0 register to:

- Set the transmit enable bitt(N) to enable the UART for data transmission.

- Enable parity, if appropriate and if MUIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or cleaCTSE to enable or disable control frothe remote receiver using the CTS pin.

- 8. Execute an instruction to enable interrupts.

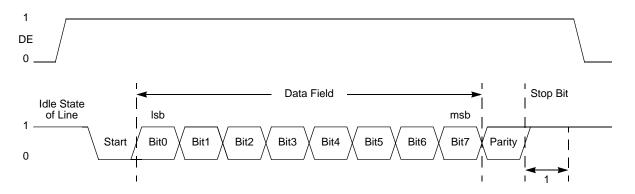

# **External Driver Enable**

The UART provides a Driver Enable (DE)gnal for off-chip bus transceivers. This feature reduces the software overhead as sockienth using a GPIO pin to control the transceiver when communicating on altimuansceiver bus, such as RS-485.

Driver Enable is an active High signal theativelopes the entire transmitted data frame including parity and Stopits as displayed in Figure 14 The Driver Enable signal asserts when a byte is written to the UART Transmitted register. The Driver Enable signal asserts at least one UART bit period and greater than two UART bit periods before the Start bit is transmitted. This allows a seturpe to enable the transceiver. The Driver Enable signal deasserts one system clock parted the final Stop bit is transmitted. This one system clock delay allows both time fortacter clear the transceiver before disabling it, as well as the ability to deterine if another character follows the current character. In the event of back to back characters (related must be written to the Transmit Data Register before the previous character is probetely transmitted) the DE signal is not deasserted between characters. The Driver Link to the Driver Enable signal.

The Driver Enable to Start bitetup time is calculated as follows:

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

## **UART** Interrupts

The UART features separate interrupts fortthe smitter and the reiver. In addition, when the UART primary functionality is disketed, the Baud Rate Generator can also function as a basic timer with interrupt capability.

# Comparator

Z8 Encore! X<sup>®</sup> F0823 Series devices feature **agra**l purpose comparator that compares two analog input signals. A GPkOm(P) pin provides the positive comparator input. The negative input (INN) can be taken from either an external GPIO pin or an internal reference. The output is availableasinterrupt source or can be routed to an external pin using the GPIO multipleThe features of Comparator include:

- Two inputs which can be connected using the GPIO multiplex (MUX)

- One input can be connected tpragrammable internal reference

- One input can be connected the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connetted in internal reference which is a user selectable reference that is user grammable with 200 mV resolution.

The comparator can be powered dowsatve on supply current. For details, Besver Control Register On page 32.

Caution: Because of the propagation delay of thenparator, it is not recommended to enable the comparator without first disabling intrupts and waiting forthe comparator output to settle. Doing so can result in spuriouserrupts after comparator enabling. The following example shows how to felay enable the comparator:

```

di

ld cmp0

nop

, wait for output to settle

clr irq0; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definitions**

# **Comparator Control Register**

The Comparator Control register (CMPCTdo)nfigures the comparator inputs and sets the value of the internal voltage reference.

#### Table 76. Comparator Control Register (CMP0)

| BITS  | 7      | 6      | 5               | 4   | 3   | 2   | 1   | 0   |

|-------|--------|--------|-----------------|-----|-----|-----|-----|-----|

| FIELD | INPSEL | INNSEL | REFLVL Reserved |     |     |     |     |     |

| RESET | 0      | 0      | 0               | 1   | 0   | 1   | 0   | 0   |

| R/W   | R/W    | R/W    | R/W             | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F90H   |        |                 |     |     |     |     |     |

INPSEL—Signal Select for Positive Input

0 = GPIO pin used as positive comparator input

1 = temperature sensor used positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPb0 used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level

Note:

This reference is independent the ADC voltage reference.

$0000 = 0.0 \vee$   $0001 = 0.2 \vee$   $0010 = 0.4 \vee$   $0011 = 0.6 \vee$   $0100 = 0.8 \vee$   $0101 = 1.0 \vee$  (Default)  $0110 = 1.2 \vee$   $0111 = 1.4 \vee$   $1000 = 1.6 \vee$   $1001 = 1.8 \vee$ 1010-1111 = Reserved

Reserved—R/W bits must beduring writes; 0 when read

# Z8 Encore! XP <sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# Flash Information Area

The Flash information area is separater from ogram memory and is mapped to the address rangeeooh to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here.

value63H to the Flash Control register initiatterse Mass Erase operation. While the Flash Controller executes the Mass Erase operative 28 CPU idles but the system clock and on-chip peripherals continue to operate ing the On-Chip Debugger, poll the Flash Status register to determine when the Masse operation is complete. When the Mass Erase is complete, the Flash Content of the oreturns to its locked state.

### Flash Controller Bypass

The Flash Controller can be bypassed taked control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the lash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit inlitize ogramming of the Flash memory. Page Erase operations are also supported involves flash Controller is bypassed.

For more information on bypassitting Flash Controller, refer third-Party Flash Programming Support for Z8 Encore! (AN011aW)ailable for download artww.zilog.com

### Flash Controller Beh avior in DEBUG Mode

The following changes in behavior of et Flash Controller occur when the Flash Controller is accessed ing the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is diged for programming and erase operations

- Programming operations are not limited he page selected in the Page Select register

- Bits in the Flash Sector Protectifister can be written to one or zero

- The second write of the Page Select regitat unlock the Flash Controller is not necessary

- The Page Select register can be writtenen the Flash Controller is unlocked

- The Mass Erase command is enabled ugh the Flash Control register

- Caution: For security reasons, Flash controller allowsly a single page to be opened for write/ erase. When writing multiple Flaspages, the Flash controllenust go through the unlock sequence again to select another page.

• Read Program Memory CRC (0EH)—The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16-bit CRC-CCITT polynomial. If the device isst in DEBUG mode, this command returnsFFFFH for the CRC value. Unlike most othoCD Read commands, there is a delay from issuing of the command until the OCED urns the data. The OCD reads the Program Memory, calculates the CRC value, and resultine result. The delay a function of the Program Memory size and approximately equal to the same clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location be device is not in DEBUG mode or the Flash Read Protect Option bit is elready the OCD ignores this command.

```

DBG \leftarrow 10H

```

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the style of the instruction he remaining 0-4 bytes of the instruction are read from Program MemoryisTcommand is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Filatead Protect Optidation is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the executed. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG mode or the Flash ReadtEct Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

# **OCD** Control Register

The OCD Control register controls the statehorf OCD. This register is used to enter or exit DEBUG mode and to enable the instruction. It also resets Z8 Encore! P0823 Series device.

# **Electrical Characteristics**

The data in this chapter is pre-qualification d pre-characterization and is subject to change. Additional electrica haracteristics may be four indthe individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those liste daible 117 may cause permanent damage to the device. These ratings are stress ratings only. Operational data device at any condition outside those indicated in the operational stions of these specifications more implied. Exposure to absolute maximum rating coitions for extended periods ay affect device reliability. For improved reliability, tie unused puts to one of the supply voltages  $O(V \text{ or } V_{SS})$ .

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

### Table 119. Power Consumption (Continued)

|                    |                 | V <sub>DE</sub>      | <sub>0</sub> = 2.7 V to 3 |                      |       |                        |  |  |

|--------------------|-----------------|----------------------|---------------------------|----------------------|-------|------------------------|--|--|

|                    |                 |                      | Maximum <sup>2</sup>      | Maximum <sup>3</sup> |       |                        |  |  |

| Symbol             | Parameter       | Typical <sup>1</sup> | Std Temp                  | Ext Temp             | Units | Conditions             |  |  |

| I <sub>DD</sub> BG | Band Gap Supply | 320                  | 480                       | 500                  | μA    | For 20-/28-pin devices |  |  |

|                    | Current         |                      |                           |                      |       | For 8-pin devices      |  |  |

| Notes              |                 |                      |                           |                      |       |                        |  |  |

1. Typical conditions are defined as  $V_{DD}$  = 3.3 V and +30 °C.

Standard temperature is defined as T<sub>A</sub> = 0 °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

3. Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

# **AC Characteristics**

The section provides information about the AlGaracteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                                   |                                                        | $V_{DD} = 2.7 V \text{ to } 3.6 V$<br>$T_A = -40 \text{ °C to } +105 \text{ °C}$<br>(unless otherwise<br>stated) |                   |          |                                           |

|-----------------------------------|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|-------------------|----------|-------------------------------------------|

| Symbol                            | Parameter                                              | Minimum                                                                                                          | Maximum           | Units    | Conditions                                |

| F <sub>SYSCLK</sub>               | System Clock Frequency                                 | _                                                                                                                | 20.0 <sup>1</sup> | MHz      | Read-only from Flash memory               |

|                                   |                                                        | 0.032768                                                                                                         | 20.0 <sup>1</sup> | MHz      | Program or erasure of the<br>Flash memory |

| T <sub>XIN</sub>                  | System Clock Period                                    | 50                                                                                                               | -                 | ns       | T <sub>CLK</sub> = 1/F <sub>syscik</sub>  |

| T <sub>XINH</sub>                 | System Clock High Time                                 | 20                                                                                                               | 30                | ns       | T <sub>CLK</sub> = 50 ns                  |

| T <sub>XINL</sub>                 | System Clock Low Time                                  | 20                                                                                                               | 30                | ns       | T <sub>CLK</sub> = 50 ns                  |

| T <sub>XINR</sub>                 | System Clock Rise Time                                 | _                                                                                                                | 3                 | ns       | T <sub>CLK</sub> = 50 ns                  |

| T <sub>XINF</sub>                 | System Clock Fall Time                                 | _                                                                                                                | 3                 | ns       | T <sub>CLK</sub> = 50 ns                  |

| <sup>1</sup> System 0<br>Table 12 | Clock Frequency is limited by the Int<br>10n page 198. | ernal Precisi                                                                                                    | on Oscillator o   | n the Z8 | Encore! XP <sup>®</sup> F0823 Series. See |

Table 120. AC Characteristics

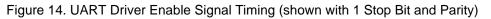

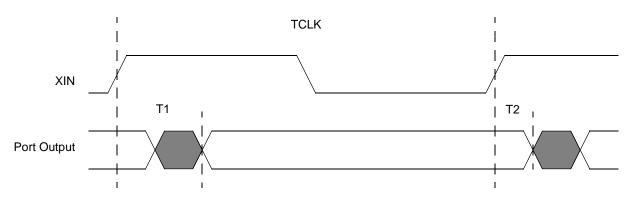

# General Purpose I/O Port Output Timing

Figure 30andTable 128provide timing information for GPIO Port pins.

Figure 30. GPIO Port Output Timing

Table 128. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |  |

|----------------|-------------------------------------|------------|---------|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |

| GPIO Port p    | vins                                |            |         |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | -          | 15      |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |

# Z8 Encore! XP <sup>®</sup> F0823 Series Product Specification