Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | ·                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0113sj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

Z8 Encore! XP<sup>®</sup> F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information on physical package specifications, see Packaging on page 209.

## **Available Packages**

Table 2 lists the package styles that are available for each device in the Z8 Encore! XP F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | X             | X             | X              | X              | X              | X              | X              | X              | X                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. Z8 Encore! XP F0823 Series Package Options

## **Pin Configurations**

Figure 2 through Figure 4 displays the pin configurations for all packages available in the Z8 Encore! XP F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANA*x*) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

| Signal Mnemonic                                      | I/O | Description                                                                                                                                                                                                           |

|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog                                               |     |                                                                                                                                                                                                                       |

| ANA[7:0]                                             | Ι   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                                                 | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                                          |     |                                                                                                                                                                                                                       |

| CLKIN                                                | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                                          |     |                                                                                                                                                                                                                       |

| LED                                                  | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger                                     |     |                                                                                                                                                                                                                       |

| DBG                                                  | I/O | Debug. This signal is the control and data input and output to and from the OCD.                                                                                                                                      |

|                                                      |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull                                                                                                                                               |

|                                                      |     | up resistor to ensure proper operation.                                                                                                                                                                               |

| Reset                                                |     |                                                                                                                                                                                                                       |

| RESET                                                | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                                         |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>                                      | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub>                                     | Ι   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>                                      | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>                                     | I   | Analog Ground.                                                                                                                                                                                                        |

| Note: The AV <sub>DD</sub> and A<br>PB7 on 28-pin pa |     | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and without ADC.                                                                                                                        |

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

| ial Conditions                              |

|---------------------------------------------|

| t delay begins after supply voltage exceeds |

| Table 10. | <b>Reset Sources</b> | and Resulting | Reset Type |

|-----------|----------------------|---------------|------------|

|           |                      | and Resulting | Redet Type |

| Operating Mode       | Reset Source                                      | Special Conditions                                                                                             |  |  |

|----------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                     |  |  |

|                      | Watchdog Timer time-out when configured for Reset | None.                                                                                                          |  |  |

|                      | RESET pin assertion                               | All reset pulses less than three system clocks ir width are ignored.                                           |  |  |

|                      | OCD initiated Reset<br>(OCDCTL[0] set to 1)       | System Reset, except the OCD is unaffected by the reset.                                                       |  |  |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                     |  |  |

|                      | RESET pin assertion                               | All reset pulses less than the specified analog delay are ignored. See Electrical Characteristics on page 193. |  |  |

|                      | DBG pin driven Low                                | None.                                                                                                          |  |  |

### **Power-On Reset**

Each device in the Z8 Encore! XP F0823 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following the POR, the POR status bit in Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 5 displays POR operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 193.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–C Control Registers on page 44), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overline{\text{RESET}}$  pin Low. The  $\overline{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) register is set.

## **Stop Mode Recovery**

The device enters into STOP mode when eZ8 CPU executes a STOP instruction. For more details on STOP mode, see Low-Power Modes on page 31. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

WDT-Watchdog Timer time-out Indicator

If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

Reserved-0 when read

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| PS024314-0308 |  |

|---------------|--|

| Port      | Pin | Mnemonic              | Alternate Function Description | Alternate Function<br>Set Register AFS1 |

|-----------|-----|-----------------------|--------------------------------|-----------------------------------------|

| Port B PB | PB0 | Reserved              |                                | AFS1[0]: 0                              |

|           |     | ANA0                  | ADC Analog Input               | AFS1[0]: 1                              |

|           | PB1 | Reserved              |                                | AFS1[1]: 0                              |

|           |     | ANA1                  | ADC Analog Input               | AFS1[1]: 1                              |

|           | PB2 | Reserved              |                                | AFS1[2]: 0                              |

|           |     | ANA2 ADC Analog Input |                                | AFS1[2]: 1                              |

|           | PB3 | CLKIN                 | External Clock Input           | AFS1[3]: 0                              |

|           |     | ANA3                  | ADC Analog Input               | AFS1[3]: 1                              |

|           | PB4 | Reserved              |                                | AFS1[4]: 0                              |

|           |     | ANA7                  | ADC Analog Input               | AFS1[4]: 1                              |

|           | PB5 | Reserved              |                                | AFS1[5]: 0                              |

|           |     | VREF*                 | ADC Voltage Reference          | AFS1[5]: 1                              |

|           | PB6 | Reserved              |                                | AFS1[6]: 0                              |

|           |     | Reserved              |                                | AFS1[6]: 1                              |

|           | PB7 | Reserved              |                                | AFS1[7]: 0                              |

|           |     | Reserved              |                                | AFS1[7]: 1                              |

**Note:** Because there are at most two choices of alternate function for any pin of Port B, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, alternate function selection as described in Port A–C Alternate Function Sub-Registers must also be enabled.

\* VREF is available on PB5 in 28-pin products only.

40

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

#### Table 17. GPIO Port Registers and Sub-Registers

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6   | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|-----|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0   | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  | FC0H     |     |     |              |       |          |          |      |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

Reserved—Must be 0

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

#### Table 39. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |  |  |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|--|--|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |  |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |  |  |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |  |  |

| ADDR  |          | FC2H  |              |               |               |          |          |        |  |  |

Reserved—0 when read

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

### **IRQ1 Enable High and Low Bit Registers**

Table 40 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 41 and Table 42) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register.

|            |            | -        |             |

|------------|------------|----------|-------------|

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 40. IRQ1 Enable and Priority Encoding

where x indicates the register bits from 0–7.

| BITS  | 7    | 6        | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|----------|---|---|---|---|---|---|

| FIELD | IRQE | Reserved |   |   |   |   |   |   |

| RESET | 0    | 0        | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | R/W  | R        | R | R | R | R | R | R |

| ADDR  |      | FCFH     |   |   |   |   |   |   |

## Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value.

0000 = ONE-SHOT mode

0001 = CONTINUOUS mode

0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

- 1000 = PWM DUAL OUTPUT mode

- 1001 = CAPTURE RESTART mode

- 1010 = COMPARATOR COUNTER Mode

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 93.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO port alternate function for the corresponding pin.

# **Flash Sector Protect Register**

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| ADDR  |        | FF9H   |        |        |        |        |        |        |  |  |

Table 82. Flash Sector Protect Register (FPROT)

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 bytes Flash sector. For the Z8F08x3 devices, the upper 3 bits must be zero. For the Z8F04x3 devices all bits are used. For the Z8F02x3 devices, the upper 4 bits are unused. For the Z8F01x3 devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

```

FFREQ[15:0] = {FFREQH[7:0],FFREQL[7:0]} = System Clock Frequency

1000

```

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

## Table 105. Notational Shorthand

| Notation | Description                    | Operand | Range                                                                                                                        |

|----------|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                             |

| СС       | Condition Code                 | —       | See Condition Codes overview in the eZ8 CPU User Manual.                                                                     |

| DA       | Direct Address                 | Addrs   | Addrs represents a number in the range of 0000H to FFFFH.                                                                    |

| ER       | Extended Addressing Register   | Reg     | Reg represents a number in the range of 000H to FFFH.                                                                        |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH.                                                                                         |

| lr       | Indirect Working Register      | @Rn     | n = 0–15.                                                                                                                    |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH.                                                                         |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                            |

| IRR      | Indirect Register Pair         | @Reg    | Reg represents an even number in the range 00H to FEH                                                                        |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                    |

| r        | Working Register               | Rn      | n = 0–15.                                                                                                                    |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH.                                                                         |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                            |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                                   |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH.                                                                       |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.      |

# **Opcode Maps**

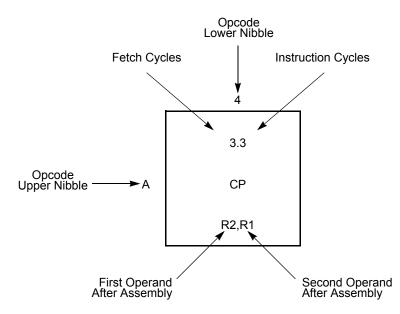

A description of the opcode map data and the abbreviations are provided in Figure 26. Figure 27 and Figure 28 provide information about each of the eZ8 CPU instructions. Table 116 lists Opcode Map abbreviations.

Figure 26. Opcode Map Cell Description

#### Table 119. Power Consumption (Continued)

|                                                                                                |                 | V <sub>DE</sub>      | <sub>0</sub> = 2.7 V to 3 | 3.6 V                |       |                        |  |  |  |

|------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------------------|----------------------|-------|------------------------|--|--|--|

|                                                                                                |                 |                      | Maximum <sup>2</sup>      | Maximum <sup>3</sup> |       |                        |  |  |  |

| Symbol                                                                                         | Parameter       | Typical <sup>1</sup> | Std Temp                  | Ext Temp             | Units | Conditions             |  |  |  |

| I <sub>DD</sub> BG                                                                             | Band Gap Supply | 320                  | 480                       | 500                  | μA    | For 20-/28-pin devices |  |  |  |

|                                                                                                | Current         |                      |                           |                      |       | For 8-pin devices      |  |  |  |

| <b>Notes</b><br>1. Typical conditions are defined as $V_{DD} = 3.3 V$ and $\pm 30 ^{\circ}C$ . |                 |                      |                           |                      |       |                        |  |  |  |

Typical conditions are defined as V<sub>DD</sub> = 3.3 V and +30 °C.

Standard temperature is defined as T<sub>A</sub> = 0 °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                                   |                                                         | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise<br>stated) |                   |                          |                                           |

|-----------------------------------|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|--------------------------|-------------------------------------------|

| Symbol                            | Parameter                                               | Minimum                                                                                                | Maximum           | Units                    | Conditions                                |

| F <sub>SYSCLK</sub>               | System Clock Frequency                                  | _                                                                                                      | 20.0 <sup>1</sup> | MHz                      | Read-only from Flash memory               |

|                                   |                                                         | 0.032768                                                                                               | 20.0 <sup>1</sup> | MHz                      | Program or erasure of the<br>Flash memory |

| T <sub>XIN</sub>                  | System Clock Period                                     | 50                                                                                                     | _                 | ns                       | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>  |

| T <sub>XINH</sub>                 | System Clock High Time                                  | 20                                                                                                     | 30                | ns                       | T <sub>CLK</sub> = 50 ns                  |

| T <sub>XINL</sub>                 | System Clock Low Time                                   | 20                                                                                                     | 30                | ns                       | T <sub>CLK</sub> = 50 ns                  |

| T <sub>XINR</sub>                 | System Clock Rise Time                                  | -                                                                                                      | 3                 | ns                       | T <sub>CLK</sub> = 50 ns                  |

| T <sub>XINF</sub>                 | System Clock Fall Time – 3                              |                                                                                                        | ns                | T <sub>CLK</sub> = 50 ns |                                           |

| <sup>1</sup> System 0<br>Table 12 | Clock Frequency is limited by the Int<br>l on page 198. | ernal Precisio                                                                                         | on Oscillator o   | n the Z8                 | Encore! XP <sup>®</sup> F0823 Series. See |

#### Table 120. AC Characteristics

| Part Number              | F           |           | ines      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part                     | Flash       | RAM       | I/O Lines | Inter      | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |

| Z8 Encore! XP with 8     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0813PB005SC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005SC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005SC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005SC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005SC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005SC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005SC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005SC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005SC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu       | re: -40 °C  | to 105 °( | 0         |            |                        |                     |                |                     |

| Z8F0813PB005EC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005EC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005EC           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005EC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005EC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005EC           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005EC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005EC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005EC           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lea | ad-Free Pac | kaging    |           |            |                        |                     |                |                     |

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

timing 205 OCD commands execute instruction (12H) 161 read data memory (0DH) 160 read OCD control register (05H) 158 read OCD revision (00H) 158 read OCD status register (02H) 158 read program counter (07H) 159 read program memory (0BH) 160 read program memory CRC (0EH) 161 read register (09H) 159 read runtime counter (03H) 158 step instruction (10H) 161 stuff instruction (11H) 161 write data memory (0CH) 160 write OCD control register (04H) 158 write program counter (06H) 159 write program memory (0AH) 159 write register (08H) 159 on-chip debugger (OCD) 151 on-chip debugger signals 10 ONE-SHOT mode 84 opcode map abbreviations 189 cell description 188 first 190 second after 1FH 191 Operational Description 21, 31, 35, 53, 67, 87, 93, 113, 117, 127, 129, 141, 151, 165, 169 OR 177 ordering information 217 **ORX 178**

status register 163

# Ρ

p 173 packaging 20-pin PDIP 211, 212 20-pin SSOP 212, 215 28-pin PDIP 213 28-pin SOIC 214 8-pin PDIP 209 8-pin SOIC 210

PDIP 214, 215 part selection guide 2 PC 174 PDIP 214, 215 peripheral AC and DC electrical characteristics 199 pin characteristics 10 Pin Descriptions 7 polarity 173 POP 177 pop using extended addressing 177 **POPX 177** port availability, device 35 port input timing (GPIO) 203 port output timing, GPIO 204 power supply signals 10 power-down, automatic (ADC) 118 Power-on and Voltage Brownout electrical characteristics and timing 199 Power-On Reset (POR) 23 program control instructions 178 program counter 174 program memory 13 **PUSH 177** push using extended addressing 177 PUSHX 177 PWM mode 84, 85 PxADDR register 44

## R

PxCTL register 45

R 173 r 173 RA register address 173 RCF 176 receive IrDA data 115 receiving UART data-interrupt-driven method 98 receiving UART data-polled method 97 register 173 ADC control (ADCCTL) 122, 124 232

RL 178

**RLC 178**

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

ADC data low bits (ADCDL) 125 flash control (FCTL) 137, 143, 144 flash high and low byte (FFREQH and FREEQL) 139 flash page select (FPS) 138, 139 flash status (FSTAT) 137 GPIO port A-H address (PxADDR) 44 GPIO port A-H alternate function sub-registers 46 GPIO port A-H control address (PxCTL) 45 GPIO port A-H data direction sub-registers 45 OCD control 161 OCD status 163 UARTx baud rate high byte (UxBRH) 110 UARTx baud rate low byte (UxBRL) 110 UARTx Control 0 (UxCTL0) 107, 110 UARTx control 1 (UxCTL1) 108 UARTx receive data (UxRXD) 105 UARTx status 0 (UxSTAT0) 105 UARTx status 1 (UxSTAT1) 106 UARTx transmit data (UxTXD) 104 Watchdog Timer control (WDTCTL) 90, 128 watch-dog timer control (WDTCTL) 167 Watchdog Timer reload high byte (WDTH) 91 Watchdog Timer reload low byte (WDTL) 91 Watchdog Timer reload upper byte (WD-TU) 91 register file 13 register pair 173 register pointer 174 reset and stop mode characteristics 22 and stop mode recovery 21 carry flag 176 sources 22 **RET 178** return 178

ADC data high byte (ADCDH) 124

rotate and shift instructions 178 rotate left 178 rotate left through carry 178 rotate right 178 rotate right through carry 178 RP 174 RR 173, 178 rr 173 RRC 178

# S

SBC 175 SCF 176, 177 second opcode map after 1FH 191 set carry flag 176, 177 set register pointer 177 shift right arithmetic 179 shift right logical 179 signal descriptions 9 single-sho conversion (ADC) 119 software trap 178 source operand 174 SP 174 SRA 179 src 174 SRL 179 **SRP 177** stack pointer 174 **STOP 177** STOP mode 31, 177 Stop Mode Recovery sources 26 using a GPIO port pin transition 27, 28 using Watchdog Timer time-out 27 SUB 175 subtract 175 subtract - extended addressing 175 subtract with carry 175 subtract with carry - extended addressing 175 **SUBX 175 SWAP 179** swap nibbles 179 symbols, additional 174