Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0123pb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| ial Conditions                              |

|---------------------------------------------|

| t delay begins after supply voltage exceeds |

| Table 10. | <b>Reset Sources</b> | and Resulting | Reset Type |

|-----------|----------------------|---------------|------------|

|           |                      | and Resulting | Redet Type |

| Operating Mode       | Reset Source                                      | Special Conditions                                                                                            |  |  |

|----------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|--|--|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                    |  |  |

|                      | Watchdog Timer time-out when configured for Reset | None.                                                                                                         |  |  |

|                      | RESET pin assertion                               | All reset pulses less than three system clocks in width are ignored.                                          |  |  |

|                      | OCD initiated Reset<br>(OCDCTL[0] set to 1)       | System Reset, except the OCD is unaffected by the reset.                                                      |  |  |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                    |  |  |

|                      | RESET pin assertion                               | All reset pulses less than the specified analog delay are ignored. See Electrical Characteristic on page 193. |  |  |

|                      | DBG pin driven Low                                | None.                                                                                                         |  |  |

#### **Power-On Reset**

Each device in the Z8 Encore! XP F0823 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following the POR, the POR status bit in Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 5 displays POR operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 193.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

#### Table 17. GPIO Port Registers and Sub-Registers

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6    | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|------|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I  | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0    | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W  | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          | FC0H |     |              |       |          |          |      |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

### Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Flash Option Bit, see Flash Option Bits on page 141.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see Reset Status Register on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and Z8 Encore! XP F0823 Series are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

- 6. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to step 7. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 7. Write the UART Control 1 register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR mode is enabled,.

- 11. To transmit additional bytes, return to step 5.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow the steps below to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions, if MULTIPROCESSOR mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 7. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

# **MULTIPROCESSOR (9-Bit) Mode**

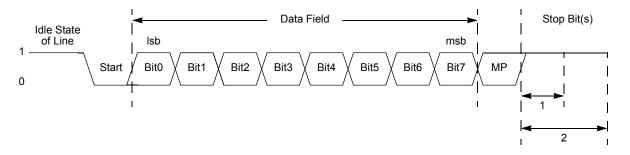

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made

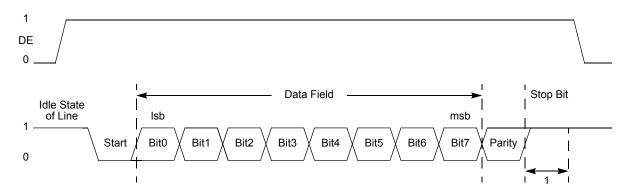

### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

108

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |

|-------|---------|------|---------|------|-------|--------|--------|------|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |

| ADDR  | F43H    |      |         |      |       |        |        |      |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

| BITS  | 7    | 6         | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------|-----------|-----|-----|-----|-----|-----|-----|

| FIELD |      | COMP_ADDR |     |     |     |     |     |     |

| RESET | 0    | 0         | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W  | R/W       | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F45H |           |     |     |     |     |     |     |

#### Table 68. UART Address Compare Register (U0ADDR)

COMP ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

# UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (Table 69 and Table 70) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

#### Table 69. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------|-----|-----|-----|-----|-----|-----|-----|

| FIELD |      | BRH |     |     |     |     |     |     |

| RESET | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F46H |     |     |     |     |     |     |     |

#### Table 70. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7    | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------|-----|-----|-----|-----|-----|-----|-----|

| FIELD |      | BRL |     |     |     |     |     |     |

| RESET | 1    | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W  | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F47H |     |     |     |     |     |     |     |

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# **Flash Control Register Definitions**

# **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FTCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| BITS  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|---|------|---|---|---|---|---|---|

| FIELD |   | FCMD |   |   |   |   |   |   |

| RESET | 0 | 0    | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | W | W    | W | W | W | W | W | W |

| ADDR  |   | FF8H |   |   |   |   |   |   |

Table 79. Flash Control Register (FCTL)

FCMD—Flash Command

73H = First unlock command

8CH = Second unlock command

95H = Page Erase command (must be third command in sequence to initiate Page Erase) 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase)

5EH = Enable Flash Sector Protect Register Access

# **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Table 80. Flash Status | Register (FSTAT) |

|------------------------|------------------|

|------------------------|------------------|

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|------|-------|-------|---|---|---|---|---|--|--|--|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |  |  |  |

| RESET | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |  |  |  |

| R/W   | R    | R     | R     | R | R | R | R | R |  |  |  |

| ADDR  |      | FF8H  |       |   |   |   |   |   |  |  |  |

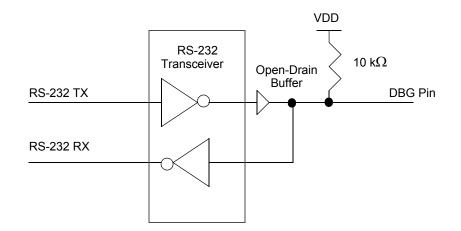

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP mode

- All enabled on-chip peripherals operate unless in STOP mode

- Automatically exits HALT mode

- Constantly refreshes the Watchdog Timer, if enabled.

#### **Entering DEBUG Mode**

The device enters DEBUG mode following the operations below:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG mode upon exiting System Reset

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 154).

• If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled high. At this

point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG mode. For more details, see OCD Unlock Sequence (8-Pin Devices Only) on page 156.

#### Exiting DEBUG Mode

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a system reset

### OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

| STADT | 00 | D1 | 50 | 50 | D4 | DE | D6 | D7 | STOD |

|-------|----|----|----|----|----|----|----|----|------|

| START | DU | Ы  | DZ | 03 | D4 | 05 | DO | Dī | STOP |

#### Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open-drain output.

### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous

178

Table 112. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

#### Table 113. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | —               | Return                        |

| TRAP     | vector          | Software Trap                 |

#### Table 114. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| 184 |  |

|-----|--|

|-----|--|

| Assembly        | -                                                               | Addre   | Address Mode<br>Opcode(s) |            |     | Flags |              |   |   |        |   | Instr. |

|-----------------|-----------------------------------------------------------------|---------|---------------------------|------------|-----|-------|--------------|---|---|--------|---|--------|

| Mnemonic        |                                                                 | dst     | src                       | (Hex)      | CZS | v     | D            | н |   | Cycles |   |        |

| OR dst, src     | $dst \gets dst \ OR \ src$                                      | r       | r                         | 42         | _   | _ *   | *            | 0 | _ | _      | 2 | 3      |

|                 |                                                                 | r       | lr                        | 43         | -   |       |              |   |   |        | 2 | 4      |

|                 |                                                                 | R       | R                         | 44         | -   |       |              |   |   |        | 3 | 3      |

|                 |                                                                 | R       | IR                        | 45         | _   |       |              |   |   |        | 3 | 4      |

|                 |                                                                 | R       | IM                        | 46         | -   |       |              |   |   |        | 3 | 3      |

|                 |                                                                 | IR      | IM                        | 47         | -   |       |              |   |   |        | 3 | 4      |

| ORX dst, src    | $dst \gets dst \: OR \: src$                                    | ER      | ER                        | 48         | -   | *     | *            | 0 | _ | -      | 4 | 3      |

|                 |                                                                 | ER      | IM                        | 49         | _   |       |              |   |   |        | 4 | 3      |

| POP dst         | dst ← @SP                                                       | R       |                           | 50         | _   | _     | _            | _ | _ | _      | 2 | 2      |

|                 | $SP \leftarrow SP + 1$                                          | IR      |                           | 51         | -   |       |              |   |   |        | 2 | 3      |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                        | ER      |                           | D8         | _   | _     | _            | _ | _ | -      | 3 | 2      |

| PUSH src        | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                  | R       |                           | 70         | _   | _     | _            | _ | - | -      | 2 | 2      |

|                 |                                                                 | IR      |                           | 71         | -   |       |              |   |   |        | 2 | 3      |

|                 |                                                                 | IM      |                           | IF70       | _   |       |              |   |   |        | 3 | 2      |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER      |                           | C8         | _   | _     | _            | _ | _ | _      | 3 | 2      |

| RCF             | C ← 0                                                           |         |                           | CF         | 0   | _     | -            | _ | _ | _      | 1 | 2      |

| RET             | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |         |                           | AF         | _   | -     | -            | _ | _ | _      | 1 | 4      |

| RL dst          | C                                                               | R       |                           | 90         | *   | *     | *            | * | - | _      | 2 | 2      |

|                 |                                                                 | IR      |                           | 91         | -   |       |              |   |   |        | 2 | 3      |

| RLC dst         | C D7D6D5D4D3D2D1D0                                              | R       |                           | 10         | *   | *     | *            | * | _ | _      | 2 | 2      |

|                 |                                                                 | IR      |                           | 11         |     |       |              |   |   |        | 2 | 3      |

| Flags Notation: | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he resu | It of the c               | operation. |     |       | ese<br>et to |   | 0 |        |   |        |

### Table 115. eZ8 CPU Instruction Summary (Continued)

Index

**COMPARE 84** compare - extended addressing 175 COMPARE mode 84 compare with carry 175 compare with carry - extended addressing 175 complement 177 complement carry flag 176 condition code 173 continuous conversion (ADC) 120 CONTINUOUS mode 84 control register definition, UART 104 Control Registers 13, 17 COUNTER modes 84 CP 175 **CPC 175 CPCX 175** CPU and peripheral overview 4 CPU control instructions 176 **CPX 175** Customer Support 237

# D

DA 173, 175 data memory 15 DC characteristics 194 debugger, on-chip 151 **DEC 175** decimal adjust 175 decrement 175 decrement and jump non-zero 178 decrement word 175 **DECW 175** destination operand 174 device, port availability 35 DI 176 direct address 173 disable interrupts 176 **DJNZ 178** dst 174

# Ε

EI 176

electrical characteristics 193 ADC 201 flash memory and timing 200 GPIO input data sample timing 202 Watchdog Timer 200, 202 enable interrupt 176 ER 173 extended addressing register 173 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 174 eZ8 CPU instruction notation 172 eZ8 CPU instruction set 171 eZ8 CPU instruction set 171

# F

FCTL register 137, 143, 144 features, Z8 Encore! 1 first opcode map 190 FLAGS 174 flags register 174 flash controller 4 option bit address space 144 option bit configuration - reset 141 program memory address 0000H 144 program memory address 0001H 145 flash memory 129 arrangement 130 byte programming 135 code protection 133 configurations 129 control register definitions 137, 143 controller bypass 136 electrical characteristics and timing 200 flash control register 137, 143, 144 flash option bits 134 flash status register 137 flow chart 132 frequency high and low byte registers 139 mass erase 135 operation 131 operation timing 133

228

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

timing 205 OCD commands execute instruction (12H) 161 read data memory (0DH) 160 read OCD control register (05H) 158 read OCD revision (00H) 158 read OCD status register (02H) 158 read program counter (07H) 159 read program memory (0BH) 160 read program memory CRC (0EH) 161 read register (09H) 159 read runtime counter (03H) 158 step instruction (10H) 161 stuff instruction (11H) 161 write data memory (0CH) 160 write OCD control register (04H) 158 write program counter (06H) 159 write program memory (0AH) 159 write register (08H) 159 on-chip debugger (OCD) 151 on-chip debugger signals 10 ONE-SHOT mode 84 opcode map abbreviations 189 cell description 188 first 190 second after 1FH 191 Operational Description 21, 31, 35, 53, 67, 87, 93, 113, 117, 127, 129, 141, 151, 165, 169 OR 177 ordering information 217 **ORX 178**

status register 163

# Ρ

p 173 packaging 20-pin PDIP 211, 212 20-pin SSOP 212, 215 28-pin PDIP 213 28-pin SOIC 214 8-pin PDIP 209 8-pin SOIC 210

PDIP 214, 215 part selection guide 2 PC 174 PDIP 214, 215 peripheral AC and DC electrical characteristics 199 pin characteristics 10 Pin Descriptions 7 polarity 173 POP 177 pop using extended addressing 177 **POPX 177** port availability, device 35 port input timing (GPIO) 203 port output timing, GPIO 204 power supply signals 10 power-down, automatic (ADC) 118 Power-on and Voltage Brownout electrical characteristics and timing 199 Power-On Reset (POR) 23 program control instructions 178 program counter 174 program memory 13 **PUSH 177** push using extended addressing 177 PUSHX 177 PWM mode 84, 85 PxADDR register 44

# R

PxCTL register 45

R 173 r 173 RA register address 173 RCF 176 receive IrDA data 115 receiving UART data-interrupt-driven method 98 receiving UART data-polled method 97 register 173 ADC control (ADCCTL) 122, 124 232

# Т

**TCM 176 TCMX 176** test complement under mask 176 test complement under mask - extended addressing 176 test under mask 176 test under mask - extended addressing 176 timer signals 9 timers 67 architecture 67 block diagram 67 CAPTURE mode 74, 75, 84, 85 CAPTURE/COMPARE mode 78, 85 COMPARE mode 76, 84 CONTINUOUS mode 69, 84 COUNTER mode 70, 71 COUNTER modes 84 GATED mode 77, 84 ONE-SHOT mode 68, 84 operating mode 68 PWM mode 72, 73, 84, 85 reading the timer count values 79 reload high and low byte registers 80 timer control register definitions 80 timer output signal operation 79 timers 0-3 control registers 82, 83 high and low byte registers 80, 81 TM 176 TMX 176 tools, hardware and software 226 transmit IrDA data 114 transmitting UART data-polled method 95 transmitting UART dat-interrupt-driven method 96 **TRAP 178**

# U

UART 4 architecture 93 baud rate generator 103

control register definitions 104 controller signals 9 data format 94 interrupts 101 MULTIPROCESSOR mode 99 receiving data using interrupt-driven method 98 receiving data using the polled method 97 transmitting data using the interrupt-driven method 96 transmitting data using the polled method 95 x baud rate high and low registers 110 x control 0 and control 1 registers 107 x status 0 and status 1 registers 105, 106 UxBRH register 110 UxBRL register 110 UxCTL0 register 107, 110 UxCTL1 register 108 UxRXD register 105 UxSTAT0 register 105 UxSTAT1 register 106 UxTXD register 104

# V

vector 173 Voltage Brownout reset (VBR) 24

# W

Watchdog Timer approximate time-out delay 87 CNTL 24 control register 89, 127, 167 electrical characteristics and timing 200, 202 interrupt in normal operation 88 interrupt in STOP mode 88 refresh 88, 177 reload unlock sequence 89 reload upper, high and low registers 90 reset 25 reset in normal operation 89