Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0123pj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Reading the Timer Count Values                           |     |

|----------------------------------------------------------|-----|

| Timer Control Register Definitions                       | 80  |

| Timer 0–1 High and Low Byte Registers                    | 80  |

| Timer Reload High and Low Byte Registers                 | 80  |

| Timer 0-1 PWM High and Low Byte Registers                | 81  |

| Timer 0–1 Control Registers                              | 82  |

| Watchdog Timer                                           | 87  |

| Operation                                                | 87  |

| Watchdog Timer Refresh                                   |     |

| Watchdog Timer Time-Out Response                         | 88  |

| Watchdog Timer Reload Unlock Sequence                    |     |

| Watchdog Timer Control Register Definitions              | 89  |

| Watchdog Timer Control Register                          |     |

| Watchdog Timer Reload Upper, High and Low Byte Registers |     |

| Universal Asynchronous Receiver/Transmitter              | 93  |

| Architecture                                             | 93  |

| Operation                                                | 94  |

|                                                          | ~ 4 |

Shared Interrupt Select Register ..... 64 Interrupt Control Register ..... 64

#### vi

memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP<sup>®</sup> F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

| Z8F0123 and Z8F0113 Products |                          |

| 0000–0001                    | Flash Option Bits        |

|                              |                          |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

| Address (Hex)   | Register Description    | Mnemonic | Reset (Hex) | Page No |

|-----------------|-------------------------|----------|-------------|---------|

| F91–FBF         | Reserved                | —        | XX          |         |

| Interrupt Contr | oller                   |          |             |         |

| FC0             | Interrupt Request 0     | IRQ0     | 00          | 58      |

| FC1             | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | 60      |

| FC2             | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | 61      |

| FC3             | Interrupt Request 1     | IRQ1     | 00          | 59      |

| FC4             | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | 62      |

| FC5             | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | 62      |

| FC6             | Interrupt Request 2     | IRQ2     | 00          | 60      |

| FC7             | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | 63      |

| FC8             | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | 63      |

| FC9–FCC         | Reserved                |          | XX          |         |

| FCD             | Interrupt Edge Select   | IRQES    | 00          | 64      |

| FCE             | Shared Interrupt Select | IRQSS    | 00          | 64      |

| FCF             | Interrupt Control       | IRQCTL   | 00          | 65      |

| GPIO Port A     |                         |          |             |         |

| FD0             | Port A Address          | PAADDR   | 00          | 43      |

| FD1             | Port A Control          | PACTL    | 00          | 45      |

| FD2             | Port A Input Data       | PAIN     | XX          | 45      |

| FD3             | Port A Output Data      | PAOUT    | 00          | 45      |

| GPIO Port B     |                         |          |             |         |

| FD4             | Port B Address          | PBADDR   | 00          | 43      |

| FD5             | Port B Control          | PBCTL    | 00          | 45      |

| FD6             | Port B Input Data       | PBIN     | XX          | 45      |

| FD7             | Port B Output Data      | PBOUT    | 00          | 45      |

| GPIO Port C     | ·                       |          |             |         |

| FD8             | Port C Address          | PCADDR   | 00          | 43      |

| FD9             | Port C Control          | PCCTL    | 00          | 45      |

| FDA             | Port C Input Data       | PCIN     | XX          | 45      |

| FDB             | Port C Output Data      | PCOUT    | 00          | 45      |

| FDC-FEF         | Reserved                | _        | XX          |         |

| Watchdog Time   |                         |          |             |         |

| FF0             | Reset Status            | RSTSTAT  | XX          | 90      |

| -               | Watchdog Timer Control  | WDTCTL   | XX          | 90      |

|                 | 0                       | WDTU     |             |         |

#### Table 8. Register File Address Map (Continued)

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

# **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data register (Table 63). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

#### Table 63. UART Receive Data Register (U0RXD)

| BITS  | 7 | 6               | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|----|---|---|---|--|

| FIELD |   | RXD             |   |    |    |   |   |   |  |

| RESET | Х | X X X X X X X X |   |    |    |   |   |   |  |

| R/W   | R | R R R R R R R   |   |    |    |   |   |   |  |

| ADDR  |   |                 |   | F4 | 0H |   |   |   |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 64 and Table 65) identify the current UART operating configuration and status.

Table 64. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6  | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|----|----|----|------|------|-----|-----|

| FIELD | RDA | PE | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0  | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W   | R   | R  | R  | R  | R    | R    | R   | R   |

| ADDR  |     |    |    | F4 | 1H   |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty

1 = There is a byte in the UART Receive Data register

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred

1 = A parity error has occurred

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is

Reserved—R/W bits must be 0 during writes; 0 when read.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame

1 = The current byte is the first data byte of a new frame

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

#### **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 66 and Table 67) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Table 66. UART Control 0 Register (U0CTL0)

| BITS  | 7   | 6    | 5    | 4   | 3    | 2    | 1    | 0    |

|-------|-----|------|------|-----|------|------|------|------|

| FIELD | TEN | REN  | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET | 0   | 0    | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W  | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     | F42H |      |     |      |      |      |      |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled

1 = Transmitter enabled

REN—Receive Enable

This bit enables or disables the receiver.

0 =Receiver disabled

1 = Receiver enabled

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte)

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte)

DEPOL—Driver Enable Polarity

0 = DE signal is Active High

1 = DE signal is Active Low

BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 = Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

#### **UART Address Compare Register**

The UART Address Compare register stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match. bits of resolution are lost because of a rounding error. As a result, the final value is an 11- bit number.

#### Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control register.

#### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

a bit of the Sector Protect Register has been set, it cannot be cleared except by powering down the device.

#### Byte Programming

The Flash Memory is enabled for byte programming after unlocking the Flash Controller and successfully enabling either Mass Erase or Page Erase. When the Flash Controller is unlocked and Mass Erase is successfully completed, all Program Memory locations are available for byte programming. In contrast, when the Flash Controller is unlocked and Page Erase is successfully enabled, only the locations of the selected page are available for byte programming. An erased Flash byte contains all 1's (FFH). The programming operation can only be used to change bits from 1 to 0. To change a Flash bit (or multiple bits) from 0 to 1 requires execution of either the Page Erase or Mass Erase commands.

Byte Programming is accomplished using the On-Chip Debugger's Write Memory command or eZ8 CPU execution of the LDC or LDCI instructions. For a description of the LDC and LDCI instructions, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>. While the Flash Controller programs the Flash memory, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. To exit programming mode and lock the Flash, write any value to the Flash Control register, except the Mass Erase or Page Erase commands.

**Caution:** The byte at each address of the Flash memory cannot be programmed (any bits written to 0) more than twice before an erase cycle occurs. Doing so may result in corrupted data at the target byte.

#### Page Erase

The Flash memory can be erased one page (512 bytes) at a time. Page Erasing the Flash memory sets all bytes in that page to the value FFH. The Flash Page Select register identifies the page to be erased. Only a page residing in an unprotected sector can be erased. With the Flash Controller unlocked and the active page set, writing the value 95h to the Flash Control register initiates the Page Erase operation. While the Flash Controller executes the Page Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. The eZ8 CPU resumes operation after the Page Erase operation completes. If the Page Erase operation is performed using the On-Chip Debugger, poll the Flash Status register to determine when the Page Erase operation is complete. When the Page Erase is complete, the Flash Controller returns to its locked state.

#### Mass Erase

The Flash memory can also be Mass Erased using the Flash Controller, but only by using the On-Chip Debugger. Mass Erasing the Flash memory sets all bytes to the value FFH. With the Flash Controller unlocked and the Mass Erase successfully enabled, writing the

configurations. The information contained here is lost when page 0 of the Program Memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in Flash Information Area on page 15

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (for more details, see Reading the Flash Information Page on page 143 and Serialization Data on page 148) and are unaffected by mass erasure of the device's Flash memory.

#### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

Note:

Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

#### Flash Program Memory Address 0001H

#### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6           | 5            | 4        | 3        | 2       | 1   | 0   |

|------------|----------------------|-------------|--------------|----------|----------|---------|-----|-----|

| FIELD      |                      | Reserved    |              | XTLDIS   | Reserved |         |     |     |

| RESET      | U                    | U           | U            | U        | U        | U U U U |     |     |

| R/W        | R/W                  | R/W         | R/W          | R/W      | R/W      | R/W     | R/W | R/W |

| ADDR       | Program Memory 0001H |             |              |          |          |         |     |     |

| Note:    = | Inchanged b          | V Reset R/M | = Read/Write | <b>`</b> |          |         |     |     |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- $0 = Crystal \ oscillator \ is \ enabled \ during \ reset, \ resulting \ in \ longer \ reset \ timing$

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

#### Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS        | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD       | Reserved                                        |     |     |     |     |     |     |     |  |

| RESET       | U                                               | U   | U   | U   | U   | U   | U   | U   |  |

| R/W         | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR        | Information Page Memory 0020H                   |     |     |     |     |     |     |     |  |

| Note: U = U | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |

Reserved—Altering this register may result in incorrect device operation.

#### Trim Bit Address 0001H—Reserved

#### Table 90. Trim Option Bits at 0001H

| BITS      | 7                             | 6            | 5            | 4          | 3                                               | 2   | 1   | 0   |  |  |  |  |  |

|-----------|-------------------------------|--------------|--------------|------------|-------------------------------------------------|-----|-----|-----|--|--|--|--|--|

| FIELD     | Reserved                      |              |              |            |                                                 |     |     |     |  |  |  |  |  |

| RESET     | U                             | U            | U            | U          | U                                               | U   | U   | U   |  |  |  |  |  |

| R/W       | R/W                           | R/W          | R/W          | R/W        | R/W                                             | R/W | R/W | R/W |  |  |  |  |  |

| ADDR      | Information Page Memory 0021H |              |              |            |                                                 |     |     |     |  |  |  |  |  |

| Note: U = | Unchanged b                   | y Reset. R/W | = Read/Write | <b>)</b> . | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |  |  |  |  |  |

147

Reserved— Altering this register may result in incorrect device operation.

#### Trim Bit Address 0002H

#### Table 91. Trim Option Bits at 0002H (TIPO)

| BITS      | 7           | 6                             | 5            | 4          | 3 | 2 | 1 | 0 |  |  |

|-----------|-------------|-------------------------------|--------------|------------|---|---|---|---|--|--|

| FIELD     | IPO_TRIM    |                               |              |            |   |   |   |   |  |  |

| RESET     |             | U                             |              |            |   |   |   |   |  |  |

| R/W       |             |                               |              | R          | W |   |   |   |  |  |

| ADDR      |             | Information Page Memory 0022H |              |            |   |   |   |   |  |  |

| Note: U = | Unchanged b | y Reset. R/W                  | = Read/Write | <b>)</b> . |   |   |   |   |  |  |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

#### Trim Bit Address 0003H—Reserved

#### Trim Bit Address 0004H—Reserved

# **Zilog Calibration Data**

#### **ADC Calibration Data**

#### Table 92. ADC Calibration Bits

| BITS                                            | 7                                   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD                                           | ADC_CAL                             |     |     |     |     |     |     |     |

| RESET                                           | U                                   | U   | U   | U   | U   | U   | U   | U   |

| R/W                                             | R/W                                 | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR                                            | Information Page Memory 0060H–007DH |     |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                     |     |     |     |     |     |     |     |

ADC CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

174

Table 106 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

|        | -                         |  |  |  |

|--------|---------------------------|--|--|--|

| Symbol | Definition                |  |  |  |

| dst    | Destination Operand       |  |  |  |

| src    | Source Operand            |  |  |  |

| @      | Indirect Address Prefix   |  |  |  |

| SP     | Stack Pointer             |  |  |  |

| PC     | Program Counter           |  |  |  |

| FLAGS  | Flags Register            |  |  |  |

| RP     | Register Pointer          |  |  |  |

| #      | Immediate Operand Prefix  |  |  |  |

| В      | Binary Number Suffix      |  |  |  |

| %      | Hexadecimal Number Prefix |  |  |  |

| Н      | Hexadecimal Number Suffix |  |  |  |

|        |                           |  |  |  |

Table 106. Additional Symbols

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

# **On-Chip Peripheral AC and DC Electrical Characteristics**

### Table 122. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = -40 °C to +105 °C |                 |              |          |                                                                                                       |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------|--------------|----------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                                      | Minimum Typical <sup>1</sup> Maxir |                 | Maximum      | Units    | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20                               | 2.45            | 2.70         | V        | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15                               | 2.40            | 2.65         | V        | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                                    | 50              | 75           | mV       |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | _                                  | V <sub>SS</sub> | -            | V        |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                                  | 70              | -            | μs       | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                                    | 16              |              | μs       | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                                                             |                                    | 16              |              | μs       | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                                  | 10              | _            | μs       | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10                               | _               | 100          | ms       |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                                    | 20              |              | ns       | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

|                   | he typical column is from char are not tested in production.                                                   | acterization                       | at 3.3 V and    | 30 °C. These | values a | re provided for design guidance                                                                       |  |

199

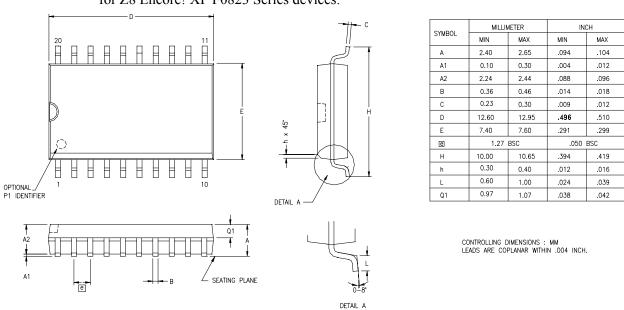

Figure 38 displays the 20-pin Small Outline Integrated Circuit Package (SOIC) available for Z8 Encore! XP F0823 Series devices.

Figure 38. 20-Pin Small Outline Integrated Circuit Package (SOIC)

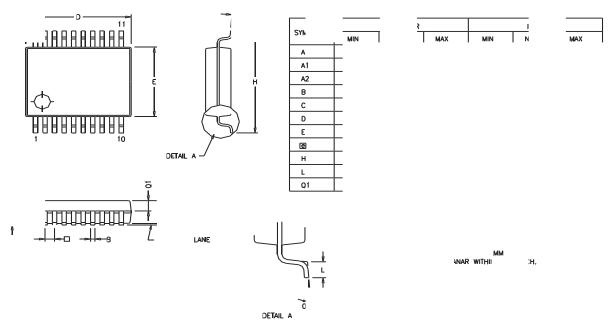

Figure 39 displays the 20-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

Figure 39. 20-Pin Small Shrink Outline Package (SSOP)