Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 1KB (1K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 256 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0123qb005sc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active Low<br>or Active<br>High | Tristate<br>Output | Internal Pull-up<br>or Pull-down                        | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                    | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------|--------------------|---------------------------------------------------------|------------------------------|---------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if key<br>sequence<br>detected) | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| RESET/<br>PA2      | I/O       | I/O<br>(defaults<br>to RESET)                                           | N/A                             | Yes                | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes                          | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

| VSS                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

# Table 5. Pin Characteristics (8-Pin Devices)

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 151.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 167), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0], and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see Oscillator Control Register Definitions on page 167) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP<sup>®</sup> F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! XP F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 57 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 57. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value |            | te Time-Out Delay<br>WDT oscillator frequency) |  |  |

|------------------|------------------|------------|------------------------------------------------|--|--|

| (Hex)            | (Decimal)        | Typical    | Description                                    |  |  |

| 000004           | 4                | 400 μs     | Minimum time-out delay                         |  |  |

| FFFFF            | 16,777,215       | 28 minutes | Maximum time-out delay                         |  |  |

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte)

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte)

DEPOL—Driver Enable Polarity

0 = DE signal is Active High

1 = DE signal is Active Low

BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 = Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

## **UART Address Compare Register**

The UART Address Compare register stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match. Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

## **Transmitting IrDA Data**

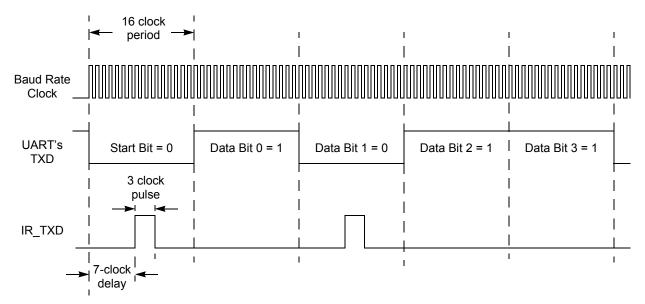

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

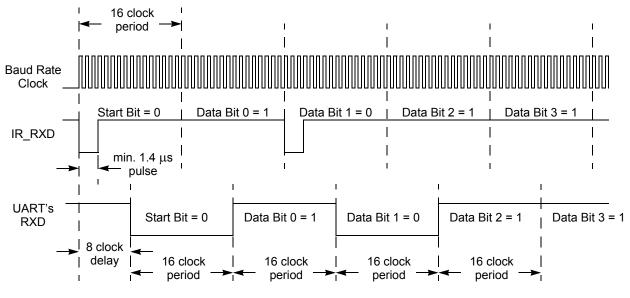

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the 1.4 μs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

# ADC Data Low Bits Register

The ADC Data Low Byte register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 75. ADC Data Low Bits Register (ADCD\_L)

| BITS  | 7     | 6    | 5 | 4 | 3   | 2 | 1 | 0 |  |

|-------|-------|------|---|---|-----|---|---|---|--|

| FIELD | ADCDL |      |   |   | OVF |   |   |   |  |

| RESET | Х     | Х    | Х | Х | Х   | Х | Х | Х |  |

| R/W   | R     | R    | R | R | R   | R | R | R |  |

| ADDR  |       | F73H |   |   |     |   |   |   |  |

ADCDL—ADC Data Low Bits

These bits are the least significant three bits of the 11-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Undefined when read

OVF—Overflow Status

0= An overflow did not occur in the digital filter for the current sample

1= An overflow did occur in the digital filter for the current sample

# Flash Operation Timing Using the Flash Frequency Registers

Before performing either a program or erase operation on Flash memory, you must first configure the Flash Frequency High and Low Byte registers. The Flash Frequency registers allow programming and erasing of the Flash with system clock frequencies ranging from 32 kHz (32768 Hz) through 20 MHz.

The Flash Frequency High and Low Byte registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz). This value is calculated using the following equation:

FFREQ[15:0] = System Clock Frequency (Hz) 1000

**Caution:** Flash programming and erasure are not supported for system clock frequencies below 32 kHz (32768 Hz) or above 20 MHz. The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure operation of Z8 Encore! XP<sup>®</sup> F0823 Series devices.

## Flash Code Protection Against External Access

The user code contained within the Flash memory can be protected against external access with the On-Chip Debugger. Programming the FRP Flash Option Bit prevents reading of the user code with the On-Chip Debugger. For more information, see Flash Option Bits on page 141 and On-Chip Debugger on page 151.

## Flash Code Protection Against Accidental Program and Erasure

Z8 Encore! XP F0823 Series provides several levels of protection against accidental program and erasure of the Flash memory contents. This protection is provided by a combination of the Flash Option bits, the register locking mechanism, the page select redundancy and the sector level protection control of the Flash Controller.

#### Flash Code Protection Using the Flash Option Bits

The FRP and FWP Flash Option Bits combine to provide three levels of Flash Program Memory protection as listed in Table 78. For more information, see Flash Option Bits on page 141.

point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG mode. For more details, see OCD Unlock Sequence (8-Pin Devices Only) on page 156.

#### Exiting DEBUG Mode

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a system reset

## OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

| <br>  |    |    |    |    |    |    |    |    |      |

|-------|----|----|----|----|----|----|----|----|------|

| START | D0 | D1 | D2 | D3 | D4 | D5 | D6 | D7 | STOP |

#### Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open-drain output.

## **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous

155

datastreams, the maximum recommended baud rate is the system clock frequency divided by eight. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by four, but this theoretical maximum is possible only for low noise designs with clean signals. Table 98 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended<br>Maximum Baud<br>Rate (kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (kbps) |

|---------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|

| 5.5296                          | 1382.4                                     | 691,200                                       | 1.08                        |

| 0.032768 (32 kHz)               | 4.096                                      | 2400                                          | 0.064                       |

#### Table 98. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the auto-baud detector/generator resets. Reconfigure the auto-baud detector/generator by sending 80H.

### **OCD Serial Errors**

The OCD detects any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the auto-baud detector/generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F0823 Series devices or when recovering from an error. A Serial Break from the host resets the auto-baud generator/detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host sends a Serial Break to the OCD even if the OCD is transmitting a character.

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control register.

### **Oscillator Control Register**

The Oscillator Control register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6        | 5     | 4     | 3     | 2   | 1      | 0   |  |  |

|-------|-------|----------|-------|-------|-------|-----|--------|-----|--|--|

| FIELD | INTEN | Reserved | WDTEN | POFEN | WDFEN |     | SCKSEL |     |  |  |

| RESET | 1     | 0        | 1     | 0     | 0     | 0   | 0      | 0   |  |  |

| R/W   | R/W   | R/W      | R/W   | R/W   | R/W   | R/W | R/W    | R/W |  |  |

| ADDR  |       | F86H     |       |       |       |     |        |     |  |  |

Table 102. Oscillator Control Register (OSCCTL)

174

Table 106 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

|        | -                         |

|--------|---------------------------|

| Symbol | Definition                |

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Table 106. Additional Symbols

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

# eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

192

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Part Number                         | F          |            | /O Lines | nterrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

|-------------------------------------|------------|------------|----------|-----------|------------------------|---------------------|----------------|---------------------|--|--|

| Part                                | Flash      | RAM        | 10 L     | Inter     | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |  |  |

| Z8 Encore! XP with 1                |            | , 10-Bit A | Analog   | j-to-D    | igital C               | onve                | erter          |                     |  |  |

| Standard Temperature: 0 °C to 70 °C |            |            |          |           |                        |                     |                |                     |  |  |

| Z8F0123PB005SC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005SC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005SC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005SC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005SC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005SC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005SC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005SC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005SC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatur                 | e: -40 °C  | to 105 °C  | ;        |           |                        |                     |                |                     |  |  |

| Z8F0123PB005EC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005EC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005EC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005EC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005EC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005EC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005EC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005EC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005EC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Replace C with G for Lea            | d-Free Pac | kaging     |          |           |                        |                     |                |                     |  |  |

223

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

231

L LD 177 LDC 177 LDCI 176, 177 LDE 177 LDEI 176, 177 LDX 177 LEA 177 load 177 load constant 176 load constant to/from program memory 177 load constant with auto-increment addresses 177 load effective address 177 load external data 177 load external data to/from data memory and auto-increment addresses 176 load external to/from data memory and auto-increment addresses 177 load instructions 177 load using extended addressing 177 logical AND 177 logical AND/extended addressing 177 logical exclusive OR 178 logical exclusive OR/extended addressing 178 logical instructions 177 logical OR 177 logical OR/extended addressing 178 low power modes 31

# Μ

master interrupt enable 55 memory data 15 program 13 mode CAPTURE 84, 85 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 84 ONE-SHOT 84 PWM 84, 85 modes 84 MULT 175 multiply 175 MULTIPROCESSOR mode, UART 99

# Ν

NOP (no operation) 176 notation b 173 cc 173 DA 173 ER 173 IM 173 IR 173 Ir 173 **IRR 173** Irr 173 p 173 R 173 r 173 RA 173 RR 173 rr 173 vector 173 X 173 notational shorthand 173

#### O OCD

architecture 151 auto-baud detector/generator 154 baud rate limits 155 block diagram 151 breakpoints 156 commands 157 control register 161 data format 154 DBG pin to RS-232 Interface 152 DEBUG mode 153 debugger break 178 interface 152 serial errors 155