Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213pb005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Dessiving Data using the Dallad Mathad                | 07         |

|-------------------------------------------------------|------------|

| Receiving Data using the Polled Method                |            |

| Clear To Send (CTS) Operation                         |            |

| MULTIPROCESSOR (9-Bit) Mode                           |            |

| External Driver Enable                                |            |

| UART Interrupts                                       |            |

| UART Baud Rate Generator                              |            |

| UART Control Register Definitions                     | 104        |

| UART Transmit Data Register                           |            |

| UART Receive Data Register                            |            |

| UART Status 0 Register                                | 105        |

| UART Status 1 Register                                |            |

| UART Control 0 and Control 1 Registers                |            |

| UART Address Compare Register                         |            |

| UART Baud Rate High and Low Byte Registers            |            |

| Infrared Encoder/Decoder                              |            |

| Architecture                                          | 113        |

| Operation                                             | 113        |

| Transmitting IrDA Data                                |            |

| Receiving IrDA Data                                   |            |

| Infrared Encoder/Decoder Control Register Definitions | 116        |

| Analog-to-Digital Converter                           | 117        |

| Architecture                                          | 117        |

| Operation                                             | 118        |

| Data Format                                           | 118        |

| Automatic Powerdown                                   |            |

| Single-Shot Conversion                                |            |

| Continuous Conversion                                 |            |

| Interrupts                                            |            |

| Calibration and Compensation                          |            |

| ADC Control Register Definitions                      |            |

| ADC Control Register 0                                |            |

| ADC Control/Status Register 1                         | 124        |

| ADC Data Low Bits Register                            |            |

|                                                       | 120        |

| Comparator                                            | 127        |

| Comparator                                            |            |

| Operation                                             | 127        |

| -                                                     | 127<br>127 |

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

### 17

# **Register Map**

Table 8 lists the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0823 Series devices. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, or all GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page No   |

|----------------|-----------------------------------|---------------|-------------|-----------|

| General-Purpos | <u> </u>                          |               |             | 1 490 110 |

| Z8F0823/Z8F08  |                                   |               |             |           |

|                |                                   |               | ~~~         |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | _             | XX          |           |

| Z8F0423/Z8F04  |                                   |               |             |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | —             | XX          |           |

| Z8F0223/Z8F02  | 13 Devices                        |               |             |           |

| 000–1FF        | General-Purpose Register File RAM | —             | XX          |           |

| 200–EFF        | Reserved                          | —             | XX          |           |

| Z8F0123/Z8F01  | 13 Devices                        |               |             |           |

| 000–0FF        | General-Purpose Register File RAM | _             | XX          |           |

| 100–EFF        | Reserved                          | _             | XX          |           |

| Timer 0        |                                   |               |             |           |

| F00            | Timer 0 High Byte                 | ТОН           | 00          | 80        |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | 80        |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | 81        |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | 81        |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | 81        |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | 82        |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | 82        |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | 83        |

| Timer 1        |                                   |               |             |           |

| F08            | Timer 1 High Byte                 | T1H           | 00          | 80        |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | 80        |

| F0A            | Timer 1 Reload High Byte          | T1RH          | FF          | 81        |

| F0B            | Timer 1 Reload Low Byte           | T1RL          | FF          | 81        |

# **Reset and Stop Mode Recovery**

The Reset Controller within the Z8 Encore! XP<sup>®</sup> F0823 Series controls Reset and Stop Mode Recovery operation and provides indication of low supply voltage conditions. In typical operation, the following events cause a Reset:

- Power-On Reset (POR)

- Voltage Brownout (VBO)

- Watchdog Timer time-out (when configured by the WDT\_RES Flash Option Bit to initiate a reset)

- External RESET pin assertion (when the alternate RESET function is enabled by the GPIO register)

- On-chip Debugger initiated Reset (OCDCTL[0] set to 1)

When the device is in STOP mode, a Stop Mode Recovery is initiated by either of the following:

- Watchdog Timer time-out

- GPIO port input pin transition on an enabled Stop Mode Recovery source

The VBO circuitry on the device performs the following function:

• Generates the VBO reset when the supply voltage drops below a minimum safe level

## **Reset Types**

Z8 Encore! XP F0823 Series provides several different types of Reset operation. Stop Mode Recovery is considered a form of Reset. Table 9 lists the types of Reset and their operating characteristics. The System Reset is longer if the external crystal oscillator is enabled by the Flash option bits, allowing additional time for oscillator start-up.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

## **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

#### Table 17. GPIO Port Registers and Sub-Registers

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

## **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 35. Interrupt Request 1 Register (IRQ1)

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|-------|-------|------|------|------|------|------|------|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |       |       |      | FC   | 3H   |      |      |      |

PA7VI—Port A7 Interrupt Request

0 = No interrupt request is pending for GPIO Port A

1 = An interrupt request from GPIO Port A

PA6CI—Port A6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator

1 = An interrupt request from GPIO Port A or Comparator

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin x

1 = An interrupt request from GPIO Port A pin x is awaiting service

where x indicates the specific GPIO Port pin number (0-5)

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 36) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPARATOR COUNTER mode, the prescaler is disabled.

**Caution:** *The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.*

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COMPARATOR COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER mode. After the first timer Reload in COMPARATOR COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions = Current Count Value – Start Value

# **Timer Control Register Definitions**

## Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 49 and Table 50) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD | ТН         |     |     |     |     |     |     |     |  |  |  |

| RESET | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR  | F00H, F08H |     |     |     |     |     |     |     |  |  |  |

Table 49. Timer 0–1 High Byte Register (TxH)

#### Table 50. Timer 0–1 Low Byte Register (TxL)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |  |  |

|-------|-----|-----|-----|-------|------|-----|-----|-----|--|--|--|--|

| FIELD | TL  |     |     |       |      |     |     |     |  |  |  |  |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |  |  |  |  |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |  |  |

| ADDR  |     |     |     | F01H, | F09H |     |     |     |  |  |  |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value

## **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 51 and Table 52) store a 16-bit Reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

| BITS  | 7    | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |  |  |

|-------|------|-----|-----|-------|------|-----|-----|-----|--|--|--|--|

| FIELD | PWML |     |     |       |      |     |     |     |  |  |  |  |

| RESET | 0    | 0   | 0   | 0     | 0    | 0   | 0   | 0   |  |  |  |  |

| R/W   | R/W  | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |  |  |

| ADDR  |      |     |     | F05H, | F0DH |     |     |     |  |  |  |  |

#### Table 54. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

### **Timer 0–1 Control Registers**

#### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input Capture event.

Table 55. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6    | 5    | 4        | 3    | 2    | 1   | 0   |

|-------|---------|------|------|----------|------|------|-----|-----|

| FIELD | TMODEHI | TICO | NFIG | Reserved |      | PWMD |     |     |

| RESET | 0       | 0    | 0    | 0        | 0    | 0    | 0   | 0   |

| R/W   | R/W     | R/W  | R/W  | R/W      | R/W  | R/W  | R/W | R/W |

| ADDR  |         |      |      | F06H,    | F0EH |      |     |     |

#### TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value. See the TxCTL1 register description for more details.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

### **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPROCESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## **MULTIPROCESSOR (9-Bit) Mode**

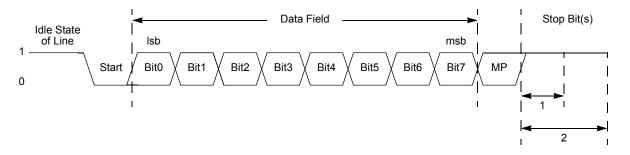

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made

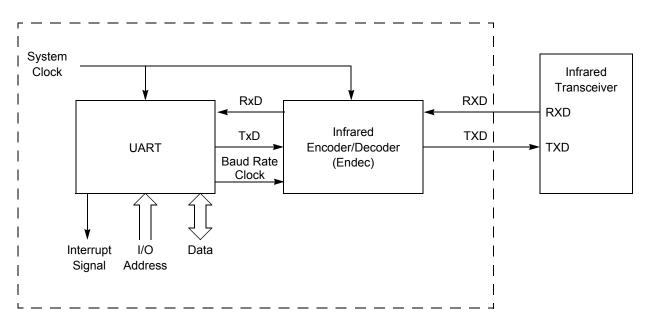

# **Infrared Encoder/Decoder**

Z8 Encore! XP<sup>®</sup> F0823 Series products contain a fully-functional, high-performance UART with Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

## Architecture

Figure 16 displays the architecture of the Infrared Endec.

Figure 16. Infrared Data Communication System Block Diagram

## Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 93.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO port alternate function for the corresponding pin.

| Assembly        |                                                                  | Addre   | ss Mode     | - Opcode(s) | Fla | ıgs |              |   |   |   | - Fetch | Instr.<br>Cycles |

|-----------------|------------------------------------------------------------------|---------|-------------|-------------|-----|-----|--------------|---|---|---|---------|------------------|

| Mnemonic        | Symbolic Operation                                               | dst     | src         |             | С   | Ζ   | S            | v | D | Н |         |                  |

| RR dst          |                                                                  | R       |             | E0          | *   | *   | *            | * | _ | - | 2       | 2                |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                             | IR      |             | E1          | -   |     |              |   |   |   | 2       | 3                |

| RRC dst         |                                                                  | R       |             | C0          | *   | *   | *            | * | _ | - | 2       | 2                |

|                 | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR      |             | C1          | _   |     |              |   |   |   | 2       | 3                |

| SBC dst, src    | $dst \gets dst - src - C$                                        | r       | r           | 32          | *   | *   | *            | * | 1 | * | 2       | 3                |

|                 |                                                                  | r       | lr          | 33          | _   |     |              |   |   |   | 2       | 4                |

|                 |                                                                  | R       | R           | 34          |     |     |              |   |   |   | 3       | 3                |

|                 |                                                                  | R       | IR          | 35          | _   |     |              |   |   |   | 3       | 4                |

|                 |                                                                  | R       | IM          | 36          |     |     |              |   |   |   | 3       | 3                |

|                 |                                                                  | IR      | IM          | 37          |     |     |              |   |   |   | 3       | 4                |

| SBCX dst, src   | $dst \gets dst - src - C$                                        | ER      | ER          | 38          | *   | *   | *            | * | 1 | * | 4       | 3                |

|                 |                                                                  | ER      | IM          | 39          | _   |     |              |   |   |   | 4       | 3                |

| SCF             | C ← 1                                                            |         |             | DF          | 1   | -   | -            | _ | _ | - | 1       | 2                |

| SRA dst         | <b>*</b> *                                                       | R       |             | D0          | *   | *   | *            | 0 | _ | - | 2       | 2                |

|                 | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR      |             | D1          |     |     |              |   |   |   | 2       | 3                |

| SRL dst         |                                                                  | R       |             | 1F C0       | *   | *   | 0            | * | _ | - | 3       | 2                |

|                 | dst                                                              | IR      |             | 1F C1       |     |     |              |   |   |   | 3       | 3                |

| SRP src         | $RP \leftarrow src$                                              |         | IM          | 01          | _   | _   | _            | _ | _ | _ | 2       | 2                |

| STOP            | STOP Mode                                                        |         |             | 6F          | _   | _   | _            | _ | _ | - | 1       | 2                |

| SUB dst, src    | $dst \gets dst - src$                                            | r       | r           | 22          | *   | *   | *            | * | 1 | * | 2       | 3                |

|                 |                                                                  | r       | lr          | 23          | _   |     |              |   |   |   | 2       | 4                |

|                 |                                                                  | R       | R           | 24          | _   |     |              |   |   |   | 3       | 3                |

|                 |                                                                  | R       | IR          | 25          | _   |     |              |   |   |   | 3       | 4                |

|                 |                                                                  | R       | IM          | 26          | -   |     |              |   |   |   | 3       | 3                |

|                 |                                                                  | IR      | IM          | 27          | _   |     |              |   |   |   | 3       | 4                |

| Flags Notation: | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu | It of the o | peration.   |     |     | ese<br>et to |   | 0 |   |         |                  |

### Table 115. eZ8 CPU Instruction Summary (Continued)

| Abbreviation | Description                           | Abbreviation                                   | Description            |  |

|--------------|---------------------------------------|------------------------------------------------|------------------------|--|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |  |

| СС           | Condition code                        | р                                              | Polarity (0 or 1)      |  |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |  |

| DA           | Destination address                   | R                                              | 8-bit register         |  |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |  |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |  |

| Ir           | Indirect Working Register             | RA                                             | Relative               |  |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |  |

## Table 116. Opcode Map Abbreviations

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

## **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

|                   |                               |         | 40 °C to +<br>therwise | 105 °C<br>specified) | Units |                                                                                 |

|-------------------|-------------------------------|---------|------------------------|----------------------|-------|---------------------------------------------------------------------------------|

| Symbol            | Parameter                     | Minimum | Typical                | Maximum              |       | Conditions                                                                      |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4     | _                      | -                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |

| I <sub>IH</sub>   | Input Leakage<br>Current      | -       | <u>+</u> 0.002         | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |

| IIL               | Input Leakage<br>Current      | -       | <u>+</u> 0.007         | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -       | -                      | <u>+</u> 5           | μA    |                                                                                 |

| I <sub>LED</sub>  | Controlled Current<br>Drive   | 1.8     | 3                      | 4.5                  | mA    | {AFS2,AFS1} = {0,0}                                                             |

|                   |                               | 2.8     | 7                      | 10.5                 | mA    | {AFS2,AFS1} = {0,1}                                                             |

|                   |                               | 7.8     | 13                     | 19.5                 | mA    | {AFS2,AFS1} = {1,0}                                                             |

|                   |                               | 12      | 20                     | 30                   | mA    | {AFS2,AFS1} = {1,1}                                                             |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -       | 8.0 <sup>2</sup>       | -                    | pF    |                                                                                 |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -       | 8.0 <sup>2</sup>       | _                    | pF    |                                                                                 |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -       | 9.5 <sup>2</sup>       | _                    | pF    |                                                                                 |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30      | 100                    | 350                  | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD     |                        |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |

#### Table 118. DC Characteristics (Continued)

Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

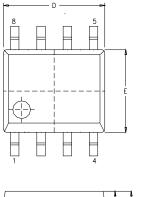

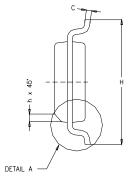

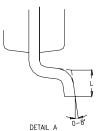

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIN  | IETER                                                                               | INCH                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|---------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MIN MAX |                                                                                     | MIN                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 1.55    | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                        | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.10    | 0.25                                                                                | 0.004                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.40    | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                        | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.36    | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                        | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.18    | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 4.80    | 4.98                                                                                | 0.189                                                                                                                                                                                                                                                                        | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3.81    | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                        | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.27    | BSC                                                                                 | .050 BSC                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 5.84    | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                        | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.25    | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                        | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.46    | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                        | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|         | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | 1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |  |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **Ordering Information**

| Part Number                                                       | Flash | RAM  | . I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|-------------------------------------------------------------------|-------|------|-------------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP with 8 KB Flash, 10-Bit Analog-to-Digital Converter |       |      |             |            |                        |                     |                |                     |

| Standard Temperatur                                               |       |      |             | 40         | 0                      | 4                   | 4              |                     |

| Z8F0823PB005SC                                                    | 8 KB  | 1 KB | 6           | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005SC                                                    | 8 KB  | 1 KB | 6           | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005SC                                                    | 8 KB  | 1 KB | 6           | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005SC                                                    | 8 KB  | 1 KB | 16          | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005SC                                                    | 8 KB  | 1 KB | 16          | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005SC                                                    | 8 KB  | 1 KB | 16          | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005SC                                                    | 8 KB  | 1 KB | 22          | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005SC                                                    | 8 KB  | 1 KB | 22          | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005SC                                                    | 8 KB  | 1 KB | 22          | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                            |       |      |             |            |                        |                     |                |                     |

| Z8F0823PB005EC                                                    | 8 KB  | 1 KB | 6           | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005EC                                                    | 8 KB  | 1 KB | 6           | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005EC                                                    | 8 KB  | 1 KB | 6           | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005EC                                                    | 8 KB  | 1 KB | 16          | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005EC                                                    | 8 KB  | 1 KB | 16          | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005EC                                                    | 8 KB  | 1 KB | 16          | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005EC                                                    | 8 KB  | 1 KB | 22          | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005EC                                                    | 8 KB  | 1 KB | 22          | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005EC                                                    | 8 KB  | 1 KB | 22          | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                          |       |      |             |            |                        |                     |                |                     |