Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213pb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

### **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

memory addresses returns FFH. Writing to these unimplemented Program Memory addresses produces no effect. Table 6 describes the Program Memory maps for the Z8 Encore! XP<sup>®</sup> F0823 Series products.

| Program Memory Address (Hex) | Function                 |

|------------------------------|--------------------------|

| Z8F0823 and Z8F0813 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0423 and Z8F0413 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-0FFF                    | Program Memory           |

| Z8F0223 and Z8F0213 Products |                          |

| 0000–0001                    | Flash Option Bits        |

| 0002–0003                    | Reset Vector             |

| 0004–0005                    | WDT Interrupt Vector     |

| 0006–0007                    | Illegal Instruction Trap |

| 0008–0037                    | Interrupt Vectors*       |

| 0038–003D                    | Oscillator Fail Traps*   |

| 003E-07FF                    | Program Memory           |

| Z8F0123 and Z8F0113 Products |                          |

| 0000–0001                    | Flash Option Bits        |

|                              |                          |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps

# **Register Map**

Table 8 lists the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0823 Series devices. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, or all GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page No   |

|----------------|-----------------------------------|---------------|-------------|-----------|

| General-Purpos | <u> </u>                          |               |             | 1 490 110 |

| Z8F0823/Z8F08  |                                   |               |             |           |

|                |                                   |               | ~~~         |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | _             | XX          |           |

| Z8F0423/Z8F04  |                                   |               |             |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | —             | XX          |           |

| Z8F0223/Z8F02  | 13 Devices                        |               |             |           |

| 000–1FF        | General-Purpose Register File RAM | —             | XX          |           |

| 200–EFF        | Reserved                          | —             | XX          |           |

| Z8F0123/Z8F01  | 13 Devices                        |               |             |           |

| 000–0FF        | General-Purpose Register File RAM | _             | XX          |           |

| 100–EFF        | Reserved                          | _             | XX          |           |

| Timer 0        |                                   |               |             |           |

| F00            | Timer 0 High Byte                 | ТОН           | 00          | 80        |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | 80        |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | 81        |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | 81        |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | 81        |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | 82        |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | 82        |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | 83        |

| Timer 1        |                                   |               |             |           |

| F08            | Timer 1 High Byte                 | T1H           | 00          | 80        |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | 80        |

| F0A            | Timer 1 Reload High Byte          | T1RH          | FF          | 81        |

| F0B            | Timer 1 Reload Low Byte           | T1RL          | FF          | 81        |

| Address (Hex)   | Register Description      | Mnemonic | Reset (Hex) | Page No |  |

|-----------------|---------------------------|----------|-------------|---------|--|

| F0C             | Timer 1 PWM High Byte     | T1PWMH   | 00          | 81      |  |

| F0D             | Timer 1 PWM Low Byte      | T1PWML   | 00          | 82      |  |

| F0E             | Timer 1 Control 0         | T1CTL0   | 00          | 82      |  |

| F0F             | Timer 1 Control 1         | T1CTL1   | 00          | 80      |  |

| F10–F3F         | Reserved                  | —        | XX          |         |  |

| UART            |                           |          |             |         |  |

| F40             | UART0 Transmit Data       | U0TXD    | XX          | 104     |  |

|                 | UART0 Receive Data        | U0RXD    | XX          | 105     |  |

| F41             | UART0 Status 0            | U0STAT0  | 0000011Xb   | 105     |  |

| F42             | UART0 Control 0           | U0CTL0   | 00          | 107     |  |

| F43             | UART0 Control 1           | U0CTL1   | 00          | 107     |  |

| F44             | UART0 Status 1            | U0STAT1  | 00          | 106     |  |

| F45             | UART0 Address Compare     | U0ADDR   | 00          | 109     |  |

| F46             | UART0 Baud Rate High Byte | U0BRH    | FF          | 110     |  |

| F47             | UART0 Baud Rate Low Byte  | U0BRL    | FF          | 110     |  |

| F48–F6F         | Reserved                  | _        | XX          |         |  |

| Analog-to-Digit | al Converter (ADC)        |          |             |         |  |

| F70             | ADC Control 0             | ADCCTL0  | 00          | 122     |  |

| F71             | ADC Control 1             | ADCCTL1  | 80          | 122     |  |

| F72             | ADC Data High Byte        | ADCD_H   | XX          | 124     |  |

| F73             | ADC Data Low Bits         | ADCD_L   | XX          | 124     |  |

| F74–F7F         | Reserved                  | _        | XX          |         |  |

| Low Power Cor   | ntrol                     |          |             |         |  |

| F80             | Power Control 0           | PWRCTL0  | 80          | 33      |  |

| F81             | Reserved                  |          | XX          |         |  |

| LED Controller  |                           |          |             |         |  |

| F82             | LED Drive Enable          | LEDEN    | 00          | 51      |  |

| F83             | LED Drive Level High Byte | LEDLVLH  | 00          | 51      |  |

| F84             | LED Drive Level Low Byte  | LEDLVLL  | 00          | 52      |  |

| F85             | Reserved                  | _        | XX          |         |  |

| Oscillator Cont | rol                       |          |             |         |  |

| F86             | Oscillator Control        | OSCCTL   | A0          | 167     |  |

| F87–F8F         | Reserved                  | _        | XX          |         |  |

| Comparator 0    |                           |          |             |         |  |

| F90             | Comparator 0 Control      | CMP0     | 14          | 128     |  |

|                 |                           |          |             |         |  |

| Address (Hex)   | Register Description    | Mnemonic | Reset (Hex) | Page No |

|-----------------|-------------------------|----------|-------------|---------|

| F91–FBF         | Reserved                | —        | XX          |         |

| Interrupt Contr | oller                   |          |             |         |

| FC0             | Interrupt Request 0     | IRQ0     | 00          | 58      |

| FC1             | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | 60      |

| FC2             | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | 61      |

| FC3             | Interrupt Request 1     | IRQ1     | 00          | 59      |

| FC4             | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | 62      |

| FC5             | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | 62      |

| FC6             | Interrupt Request 2     | IRQ2     | 00          | 60      |

| FC7             | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | 63      |

| FC8             | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | 63      |

| FC9–FCC         | Reserved                |          | XX          |         |

| FCD             | Interrupt Edge Select   | IRQES    | 00          | 64      |

| FCE             | Shared Interrupt Select | IRQSS    | 00          | 64      |

| FCF             | Interrupt Control       | IRQCTL   | 00          | 65      |

| GPIO Port A     |                         |          |             |         |

| FD0             | Port A Address          | PAADDR   | 00          | 43      |

| FD1             | Port A Control          | PACTL    | 00          | 45      |

| FD2             | Port A Input Data       | PAIN     | XX          | 45      |

| FD3             | Port A Output Data      | PAOUT    | 00          | 45      |

| GPIO Port B     |                         |          |             |         |

| FD4             | Port B Address          | PBADDR   | 00          | 43      |

| FD5             | Port B Control          | PBCTL    | 00          | 45      |

| FD6             | Port B Input Data       | PBIN     | XX          | 45      |

| FD7             | Port B Output Data      | PBOUT    | 00          | 45      |

| GPIO Port C     | ·                       |          |             |         |

| FD8             | Port C Address          | PCADDR   | 00          | 43      |

| FD9             | Port C Control          | PCCTL    | 00          | 45      |

| FDA             | Port C Input Data       | PCIN     | XX          | 45      |

| FDB             | Port C Output Data      | PCOUT    | 00          | 45      |

| FDC-FEF         | Reserved                | _        | XX          |         |

| Watchdog Time   |                         |          |             |         |

| FF0             | Reset Status            | RSTSTAT  | XX          | 90      |

| -               | Watchdog Timer Control  | WDTCTL   | XX          | 90      |

|                 | 0                       | WDTU     |             |         |

#### Table 8. Register File Address Map (Continued)

## **Low-Power Modes**

Z8 Encore! XP<sup>®</sup> F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT mode).

## **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

## HALT Mode

Executing the eZ8 CPU's HALT instruction places the device into HALT mode, which powers down the CPU but leaves all other peripherals active. In HALT mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program counter stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- If enabled, the Watchdog Timer continues to operate.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout reset

- External **RESET** pin assertion

To minimize current in HALT mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails ( $V_{CC}$  or GND).

## **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F0823 Series devices. Disabling a given peripheral minimizes its power consumption.

## **Power Control Register Definitions**

The following sections describe the power control registers.

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

| Port   | Pin | Mnemonic                | Alternate Function Description                         | Alternate Function<br>Set Register AFS1 |  |  |

|--------|-----|-------------------------|--------------------------------------------------------|-----------------------------------------|--|--|

| Port C | PC0 | Reserved                |                                                        | AFS1[0]: 0                              |  |  |

|        |     | ANA4/CINP/LED<br>Drive  | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1                              |  |  |

|        | PC1 | Reserved                |                                                        | AFS1[1]: 0                              |  |  |

|        |     | ANA5/CINN/ LED<br>Drive | AFS1[1]: 1                                             |                                         |  |  |

|        | PC2 | Reserved                | AFS1[2]: 0                                             |                                         |  |  |

|        |     | ANA6/LED/<br>VREF*      | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1                              |  |  |

| PC3    |     | COUT                    | OUT Comparator Output                                  |                                         |  |  |

|        |     | LED                     | LED drive                                              | AFS1[3]: 1                              |  |  |

|        | PC4 | Reserved                |                                                        | AFS1[4]: 0                              |  |  |

|        |     | LED                     | LED Drive                                              | AFS1[4]: 1                              |  |  |

|        | PC5 | Reserved                |                                                        | AFS1[5]: 0                              |  |  |

|        |     | LED                     | LED Drive                                              | AFS1[5]: 1                              |  |  |

|        | PC6 | Reserved                | AFS1[6]: 0                                             |                                         |  |  |

|        |     | LED                     | LED Drive                                              | AFS1[6]: 1                              |  |  |

|        | PC7 | Reserved                |                                                        | AFS1[7]: 0                              |  |  |

|        |     | LED                     | LED Drive                                              | AFS1[7]: 1                              |  |  |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

**Note:** Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in Port A–C Alternate Function Sub-Registers must also be enabled. \*VREF is available on PC2 in 20-pin parts only.

0 PIN0 X R

| 10.010 201 |      |      |      | (1, , , , , , , , , , , , , , , , , , , |      |      |      |

|------------|------|------|------|-----------------------------------------|------|------|------|

| BITS       | 7    | 6    | 5    | 4                                       | 3    | 2    | 1    |

| FIELD      | PIN7 | PIN6 | PIN5 | PIN4                                    | PIN3 | PIN2 | PIN1 |

| RESET      | Х    | Х    | Х    | Х                                       | Х    | Х    | Х    |

| R/W        | R    | R    | R    | R                                       | R    | R    | R    |

## Table 28. Port A–C Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low)

1 = Input data is logical 1 (High)

## Port A–C Output Data Register

The Port A–C Output Data register (Table 29) controls the output data to the pins.

FD2H, FD6H, FDAH

#### Table 29. Port A–C Output Data Register (PxOUT)

| BITS  | 7     | 6                | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |

|-------|-------|------------------|-------|-------|-------|-------|-------|-------|--|--|--|

| FIELD | POUT7 | POUT6            | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |  |  |  |

| RESET | 0     | 0                | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |

| R/W   | R/W   | R/W              | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |  |

| ADDR  |       | FD3H, FD7H, FDBH |       |       |       |       |       |       |  |  |  |

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

## LED Drive Enable Register

The LED Drive Enable register (Table 30) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

ADDR

### Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Flash Option Bit, see Flash Option Bits on page 141.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see Reset Status Register on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and Z8 Encore! XP F0823 Series are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

#### Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

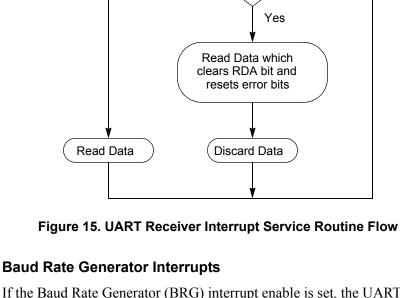

No

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

Receiver Ready

Receiver Interrupt

Read Status

Errors?

### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F0823 Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Factory trimming information for the internal precision oscillator

- Factory calibration values for ADC

- Factory serialization and randomized lot identifier (optional)

## Operation

## **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0823 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device

### OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 157).

#### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

#### **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

# **Opcode Maps**

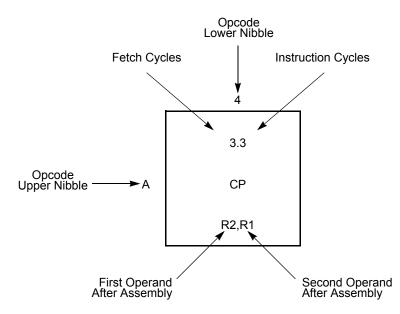

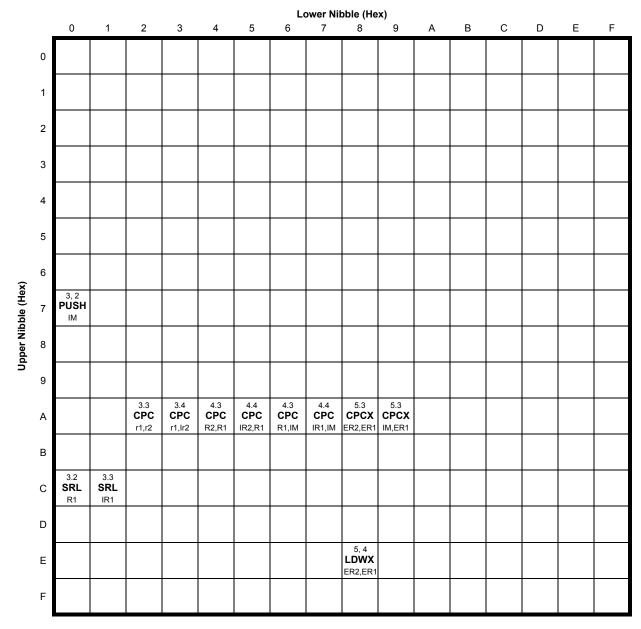

A description of the opcode map data and the abbreviations are provided in Figure 26. Figure 27 and Figure 28 provide information about each of the eZ8 CPU instructions. Table 116 lists Opcode Map abbreviations.

Figure 26. Opcode Map Cell Description

|   |                           |                            |                              |                                |                            |                               | Lo                            | ower Nil                       | oble (He                      | x)                             |                            |                          |                    |                           |                  |                          |

|---|---------------------------|----------------------------|------------------------------|--------------------------------|----------------------------|-------------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|--------------------|---------------------------|------------------|--------------------------|

|   | 0                         | 1                          | 2                            | 3                              | 4                          | 5                             | 6                             | 7                              | 8                             | 9                              | А                          | В                        | С                  | D                         | Е                | F                        |

| 0 | 1.1<br>BRK                | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1          | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br>LD<br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1          | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                    |                           |                  | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1          | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1          | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br><b>SUB</b><br>IR1,IM    | 4.3<br><b>SUBX</b><br>ER2,ER1 | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1, 2<br>ATM              |

| 3 | 2.2<br>DEC<br>R1          | 2.3<br><b>DEC</b><br>IR1   | 2.3<br><b>SBC</b><br>r1,r2   | 2.4<br><b>SBC</b><br>r1,lr2    | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br><b>SBC</b><br>IR2,R1   | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                    |                           |                  |                          |

| 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1    | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                    |                           |                  |                          |

| 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br><b>AND</b><br>IR2,R1   | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                    |                           |                  | 1.2<br>WDT               |

| 6 | 2.2<br>COM<br>R1          | 2.3<br>COM<br>IR1          | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1   | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.2<br>STOP              |

| 7 | 2.2<br>PUSH<br>R2         | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1    | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>HALT              |

| 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,Irr2 | 2.9<br><b>LDEI</b><br>Ir1,Irr2 | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>lr1,ER2         | 3.4<br>LDX<br>IRR2,R1         | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                    |                           |                  | 1.2<br>DI                |

| 9 | 2.2<br><b>RL</b><br>R1    | 2.3<br><b>RL</b><br>IR1    | 2.5<br><b>LDE</b><br>r2,Irr1 | 2.9<br><b>LDEI</b><br>Ir2,Irr1 | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>lr2,ER1         | 3.4<br>LDX<br>R2,IRR1         | 3.5<br><b>LDX</b><br>IR2,IRR1  | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                    |                           |                  | 1.2<br>El                |

| А | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1    | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.4<br>RET               |

| В | 2.2<br>CLR<br>R1          | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1   | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.5<br>IRET              |

| С | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,Irr2 | 2.9<br>LDCI<br>Ir1,Irr2        | 2.3<br><b>JP</b><br>IRR1   | 2.9<br><b>LDC</b><br>lr1,lrr2 |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                    |                           |                  | 1.2<br>RCF               |

| D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1     | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                    |                           |                  | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1    | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1         | 2.3<br><b>SWAP</b><br>IR1  | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1    | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | V                          | V                        | ▼                  | ♥                         | ▼                |                          |

Figure 27. First Opcode Map

190

Upper Nibble (Hex)

Figure 28. Second Opcode Map after 1FH

| Part Number                         | Flash      | RAM       | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

|-------------------------------------|------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|--|

| Z8 Encore! XP with 2                | KB Flash   | 1         |           |            |                        |                     |                |                     |  |  |

| Standard Temperature: 0 °C to 70 °C |            |           |           |            |                        |                     |                |                     |  |  |

| Z8F0213PB005SC                      | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0213QB005SC                      | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0213SB005SC                      | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0213SH005SC                      | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0213HH005SC                      | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0213PH005SC                      | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0213SJ005SC                      | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0213HJ005SC                      | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0213PJ005SC                      | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatur                 | re: -40 °C | to 105 °C | ;         |            |                        |                     |                |                     |  |  |

| Z8F0213PB005EC                      | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0213QB005EC                      | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |  |  |

| Z8F0213SB005EC                      | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0213SH005EC                      | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |  |  |

| Z8F0213HH005EC                      | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |  |  |

| Z8F0213PH005EC                      | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |  |  |

| Z8F0213SJ005EC                      | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |  |  |

| Z8F0213HJ005EC                      | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |  |  |

| Z8F0213PJ005EC                      | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |  |  |

| Replace C with G for Lea            | d-Free Pac | kaging    |           |            |                        |                     |                |                     |  |  |

| Part Number                              |       |       | Sel       | upts       | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | iption              |

|------------------------------------------|-------|-------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part N                                   | Flash | RAM   | I/O Lines | Interrupts | 16-Bit T<br>w/PWM      | 10-Bit              | UART           | Description         |

| Z8 Encore! XP with 1 KB Flash            |       |       |           |            |                        |                     |                |                     |

| Standard Temperature: 0 °C to 70 °C      |       |       |           |            |                        |                     |                |                     |

| Z8F0113PB005SC                           | 1 KB  | 256 B | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0113QB005SC                           | 1 KB  | 256 B | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0113SB005SC                           | 1 KB  | 256 B | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0113SH005SC                           | 1 KB  | 256 B | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0113HH005SC                           | 1 KB  | 256 B | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0113PH005SC                           | 1 KB  | 256 B | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0113SJ005SC                           | 1 KB  | 256 B | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0113HJ005SC                           | 1 KB  | 256 B | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0113PJ005SC                           | 1 KB  | 256 B | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C   |       |       |           |            |                        |                     |                |                     |

| Z8F0113PB005EC                           | 1 KB  | 256 B | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0113QB005EC                           | 1 KB  | 256 B | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0113SB005EC                           | 1 KB  | 256 B | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0113SH005EC                           | 1 KB  | 256 B | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0113HH005EC                           | 1 KB  | 256 B | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0113PH005EC                           | 1 KB  | 256 B | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0113SJ005EC                           | 1 KB  | 256 B | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0113HJ005EC                           | 1 KB  | 256 B | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0113PJ005EC                           | 1 KB  | 256 B | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |       |       |           |            |                        |                     |                |                     |