Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213ph005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Program Memory Address (Hex)                | Function                   |

|---------------------------------------------|----------------------------|

| 0002–0003                                   | Reset Vector               |

| 0004–0005                                   | WDT Interrupt Vector       |

| 0006–0007                                   | Illegal Instruction Trap   |

| 0008–0037                                   | Interrupt Vectors*         |

| 0038–003D                                   | Oscillator Fail Traps*     |

| 003E-03FF                                   | Program Memory             |

| ee Table 33 on page 54 for a list of the in | terrupt vectors and traps. |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

### **Data Memory**

Z8 Encore! XP<sup>®</sup> F0823 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# **Flash Information Area**

Table 7 lists the Z8 Encore! XP F0823 Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address<br>(Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. Z8 Encore! XP F0823 Series Flash Memory Information Area Map

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

### Table 17. GPIO Port Registers and Sub-Registers

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

### **Timer Operating Modes**

The timers can be configured to operate in the following modes:

### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control register to the start value before enabling ONE-SHOT mode. After starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode

- Set the prescale value

- Set the initial output level (High or Low) if using the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

#### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

### **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1001 = Divide by 2

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP<sup>®</sup> F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! XP F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 57 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 57. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value WDT Reload Value |            | e Time-Out Delay<br>VDT oscillator frequency) |

|------------------|-----------------------------------|------------|-----------------------------------------------|

| (Hex)            | (Decimal)                         | Typical    | Description                                   |

| 000004           | 4                                 | 400 μs     | Minimum time-out delay                        |

| FFFFF            | 16,777,215                        | 28 minutes | Maximum time-out delay                        |

No

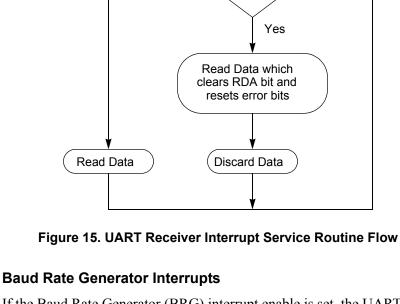

If the Baud Rate Generator (BRG) interrupt enable is set, the UART Receiver interrupt asserts when the UART Baud Rate Generator reloads. This condition allows the Baud Rate Generator to function as an additional counter if the UART functionality is not employed.

Receiver Ready

Receiver Interrupt

Read Status

Errors?

### **UART Baud Rate Generator**

The UART Baud Rate Generator creates a lower frequency baud rate clock for data transmission. The input to the Baud Rate Generator is the system clock. The UART Baud Rate High and Low Byte registers combine to create a 16-bit baud rate divisor value

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

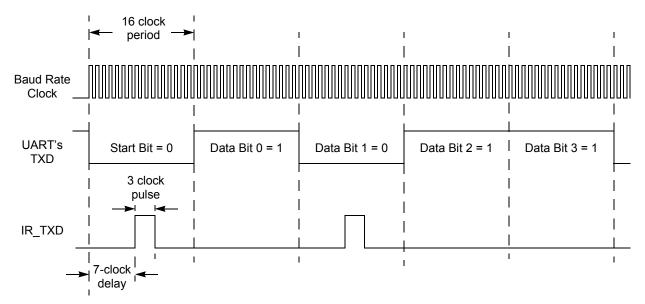

### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

# **Analog-to-Digital Converter**

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# **Flash Control Register Definitions**

## **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FTCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| BITS  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|---|---|---|---|---|---|---|

| FIELD | FCMD |   |   |   |   |   |   |   |

| RESET | 0    | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| R/W   | W    | W | W | W | W | W | W | W |

| ADDR  | FF8H |   |   |   |   |   |   |   |

Table 79. Flash Control Register (FCTL)

FCMD—Flash Command

73H = First unlock command

8CH = Second unlock command

95H = Page Erase command (must be third command in sequence to initiate Page Erase) 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase)

5EH = Enable Flash Sector Protect Register Access

### **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Table 80. Flash Status | Register (FSTAT) |

|------------------------|------------------|

|------------------------|------------------|

| BITS  | 7    | 6     | 5     | 4 | 3 | 2 | 1 | 0 |

|-------|------|-------|-------|---|---|---|---|---|

| FIELD | Rese | erved | FSTAT |   |   |   |   |   |

| RESET | 0    | 0     | 0     | 0 | 0 | 0 | 0 | 0 |

| R/W   | R    | R     | R     | R | R | R | R | R |

| ADDR  | FF8H |       |       |   |   |   |   |   |

### **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

Table 86. Trim Bit Data Register (TRMDR)

| BITS  | 7                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | TRMDR - Trim Bit Data |     |     |     |     |     |     |     |

| RESET | 0                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | FF7H                  |     |     |     |     |     |     |     |

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

### Flash Program Memory Address 0000H

Table 87. Flash Option Bits at Program Memory Address 0000H

| BITS                                            | 7                    | 6      | 5    | 4     | 3      | 2   | 1        | 0   |

|-------------------------------------------------|----------------------|--------|------|-------|--------|-----|----------|-----|

| FIELD                                           | WDT_RES              | WDT_AO | Rese | erved | VBO_AO | FRP | Reserved | FWP |

| RESET                                           | U                    | U      | U    | U     | U      | U   | U        | U   |

| R/W                                             | R/W                  | R/W    | R/W  | R/W   | R/W    | R/W | R/W      | R/W |

| ADDR                                            | Program Memory 0000H |        |      |       |        |     |          |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |        |      |       |        |     |          |     |

WDT RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always ON

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the

# **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

### Example 1

If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 103. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, s  | rc) |

|------------------------|-----|------|-----|--------------|-----|

| Object Code            | 04  | 08   | 43  | (OPC src, da | st) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 104. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

# eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 105.

• Rotate and Shift

Tables 107 through Table 114 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

|          | •        |                                               |

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| CP       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| СРХ      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

|          |          |                                               |

#### **Table 107. Arithmetic Instructions**

178

Table 112. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

### Table 113. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |  |  |  |  |

|----------|-----------------|-------------------------------|--|--|--|--|

| BRK      | _               | On-Chip Debugger Break        |  |  |  |  |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |  |  |  |  |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |  |  |  |  |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |  |  |  |  |

| CALL     | dst             | Call Procedure                |  |  |  |  |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |  |  |  |  |

| IRET     | _               | Interrupt Return              |  |  |  |  |

| JP       | dst             | Jump                          |  |  |  |  |

| JP cc    | dst             | Jump Conditional              |  |  |  |  |

| JR       | DA              | Jump Relative                 |  |  |  |  |

| JR cc    | DA              | Jump Relative Conditional     |  |  |  |  |

| RET      | —               | Return                        |  |  |  |  |

| TRAP     | vector          | Software Trap                 |  |  |  |  |

### Table 114. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

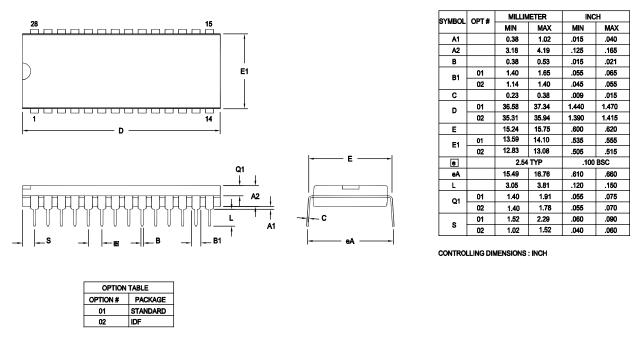

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

|                                          |             |            |           |            |                        | annels              | ۷              |                     |

|------------------------------------------|-------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash       | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP with 4                     | KB Flash    | , 10-Bit / | Analog    | j-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperatur                      | re: 0 °C to | 70 °C      |           |            |                        |                     |                |                     |

| Z8F0423PB005SC                           | 4 KB        | 1 KB       | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SC                           | 4 KB        | 1 KB       | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SC                           | 4 KB        | 1 KB       | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SC                           | 4 KB        | 1 KB       | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SC                           | 4 KB        | 1 KB       | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SC                           | 4 KB        | 1 KB       | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SC                           | 4 KB        | 1 KB       | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SC                           | 4 KB        | 1 KB       | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SC                           | 4 KB        | 1 KB       | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatu                       | re: -40 °C  | to 105 °C  | C         |            |                        |                     |                |                     |

| Z8F0423PB005EC                           | 4 KB        | 1 KB       | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EC                           | 4 KB        | 1 KB       | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EC                           | 4 KB        | 1 KB       | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EC                           | 4 KB        | 1 KB       | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EC                           | 4 KB        | 1 KB       | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EC                           | 4 KB        | 1 KB       | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EC                           | 4 KB        | 1 KB       | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EC                           | 4 KB        | 1 KB       | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EC                           | 4 KB        | 1 KB       | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |             |            |           |            |                        |                     |                |                     |

219

| mber                                     |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |

|------------------------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |

| Z8 Encore! XP with 2                     | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature                     | e: 0 °C to | 70 °C      |           |            |                        |                     |                |                     |

| Z8F0223PB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur                      | 'e: -40 °C | to 105 °C  | )         |            |                        |                     |                |                     |

| Z8F0223PB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |            |            |           |            |                        |                     |                |                     |

221

231

L LD 177 LDC 177 LDCI 176, 177 LDE 177 LDEI 176, 177 LDX 177 LEA 177 load 177 load constant 176 load constant to/from program memory 177 load constant with auto-increment addresses 177 load effective address 177 load external data 177 load external data to/from data memory and auto-increment addresses 176 load external to/from data memory and auto-increment addresses 177 load instructions 177 load using extended addressing 177 logical AND 177 logical AND/extended addressing 177 logical exclusive OR 178 logical exclusive OR/extended addressing 178 logical instructions 177 logical OR 177 logical OR/extended addressing 178 low power modes 31

# Μ

master interrupt enable 55 memory data 15 program 13 mode CAPTURE 84, 85 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 84 ONE-SHOT 84 PWM 84, 85 modes 84 MULT 175 multiply 175 MULTIPROCESSOR mode, UART 99

# Ν

NOP (no operation) 176 notation b 173 cc 173 DA 173 ER 173 IM 173 IR 173 Ir 173 **IRR 173** Irr 173 p 173 R 173 r 173 RA 173 RR 173 rr 173 vector 173 X 173 notational shorthand 173

### O OCD

architecture 151 auto-baud detector/generator 154 baud rate limits 155 block diagram 151 breakpoints 156 commands 157 control register 161 data format 154 DBG pin to RS-232 Interface 152 DEBUG mode 153 debugger break 178 interface 152 serial errors 155