Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213qb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Information Area                                        | . 130 |

|---------------------------------------------------------------|-------|

| Operation                                                     | . 131 |

| Flash Operation Timing Using the Flash Frequency Registers    |       |

| Flash Code Protection Against External Access                 |       |

| Flash Code Protection Against Accidental Program and Erasure  |       |

| Byte Programming                                              |       |

| Page Erase                                                    |       |

| Mass Erase                                                    |       |

| Flash Controller Bypass                                       |       |

| Flash Controller Behavior in DEBUG Mode                       |       |

| Flash Control Register Definitions                            |       |

| Flash Control Register                                        |       |

| Flash Status Register                                         |       |

| Flash Page Select Register      Flash Sector Protect Register |       |

| Flash Frequency High and Low Byte Registers                   |       |

|                                                               |       |

| Flash Option Bits                                             |       |

| Operation                                                     |       |

| Option Bit Configuration By Reset                             |       |

| Option Bit Types                                              |       |

| Reading the Flash Information Page                            |       |

| Flash Option Bit Control Register Definitions                 |       |

| Trim Bit Address Register                                     | -     |

| Trim Bit Data Register                                        |       |

| Flash Option Bit Address Space                                |       |

| Flash Program Memory Address 0000H                            |       |

| Flash Program Memory Address 0001H                            |       |

| Trim Bit Address Space                                        |       |

| Trim Bit Address 0000H—Reserved                               |       |

| Trim Bit Address 0001H—Reserved                               |       |

| Trim Bit Address 0002H                                        |       |

| Trim Bit Address 00031—Reserved                               |       |

|                                                               |       |

| Zilog Calibration Data                                        |       |

| Serialization Data                                            |       |

| Randomized Lot Identifier                                     |       |

|                                                               |       |

| On-Chip Debugger                                              |       |

| Architecture                                                  | . 151 |

|                                                               |       |

## viii

## 1

# **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

# **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

vector address. Following Stop Mode Recovery, the STOP bit in the Watchdog Timer Control Register is set to 1. Table 11 lists the Stop Mode Recovery sources and resulting actions. The section following the table provides more detailed information on each of the Stop Mode Recovery sources.

#### Table 11. Stop Mode Recovery Sources and Resulting Action

| Operating Mode                                                              | Stop Mode Recovery Source                             | Action                                                               |

|-----------------------------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------|

| STOP mode                                                                   | Watchdog Timer time-out when configured for Reset     | Stop Mode Recovery                                                   |

|                                                                             | Watchdog Timer time-out when configured for interrupt | Stop Mode Recovery followed by interrupt (if interrupts are enabled) |

| Data transition on any GPIO port pin<br>enabled as a Stop Mode Recovery sou |                                                       | Stop Mode Recovery                                                   |

|                                                                             | Assertion of external RESET Pin                       | System Reset                                                         |

|                                                                             | Debug Pin driven Low                                  | System Reset                                                         |

## Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Watchdog Timer Control register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and Z8 Encore! XP<sup>®</sup> F0823 Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

## Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

- **Note:** The SMR pulses shorter than specified does not trigger a recovery. When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

- **Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the port transition only if the signal stays on the port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the port pin can initiate Stop Mode Recovery without being written to the Port Input Data register or without initiating an interrupt (if enabled for that pin).

| BITS  | 7    | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|-----------------------------|---|---|---|---|---|---|

| FIELD | PWML |                             |   |   |   |   |   |   |

| RESET | 0    | 0 0 0 0 0 0 0 0             |   |   |   |   |   |   |

| R/W   | R/W  | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  |      | F05H, F0DH                  |   |   |   |   |   |   |

## Table 54. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## **Timer 0–1 Control Registers**

## Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input Capture event.

Table 55. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6          | 5   | 4        | 3       | 2   | 1   | 0      |

|-------|---------|------------|-----|----------|---------|-----|-----|--------|

| FIELD | TMODEHI | TICONFIG   |     | Reserved | ed PWMD |     |     | INPCAP |

| RESET | 0       | 0          | 0   | 0        | 0       | 0   | 0   | 0      |

| R/W   | R/W     | R/W        | R/W | R/W      | R/W     | R/W | R/W | R/W    |

| ADDR  |         | F06H, F0EH |     |          |         |     |     |        |

## TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value. See the TxCTL1 register description for more details.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

## **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

## **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 =Count occurs on the rising edge of the Timer Input signal

- 1 = Count occurs on the falling edge of the Timer Input signal

## **PWM SINGLE OUTPUT Mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

## **CAPTURE Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

### **COMPARE Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### GATED Mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flowchart in Figure 21 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

# Flash Sector Protect Register

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| ADDR  | FF9H   |        |        |        |        |        |        |        |

Table 82. Flash Sector Protect Register (FPROT)

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 bytes Flash sector. For the Z8F08x3 devices, the upper 3 bits must be zero. For the Z8F04x3 devices all bits are used. For the Z8F02x3 devices, the upper 4 bits are unused. For the Z8F01x3 devices, the upper 6 bits are unused.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

```

FFREQ[15:0] = {FFREQH[7:0],FFREQL[7:0]} = System Clock Frequency

1000

```

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP<sup>®</sup> F0823 Series products. When this option is enabled, several of the OCD commands are disabled. Table 99 on page 162 is a summary of the OCD commands. Each OCD command is described in further detail in the bulleted list following this table. Table 99 on page 162 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|----------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                                                                                                                                                         |

| Reserved                   | 01H             | _                                     | _                                                                                                                                                                         |

| Read OCD Status Register   | 02H             | Yes                                   | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H             | _                                     | -                                                                                                                                                                         |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                                                                                                                                                 |

| Read OCD Control Register  | 05H             | Yes                                   | -                                                                                                                                                                         |

| Write Program Counter      | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter       | 07H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Register             | 08H             | _                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register              | 09H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory       | 0AH             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory        | 0BH             | _                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory          | 0CH             | _                                     | Yes.                                                                                                                                                                      |

| Read Data Memory           | 0DH             | -                                     | -                                                                                                                                                                         |

| Read Program Memory CRC    | 0EH             | -                                     | -                                                                                                                                                                         |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                         |

| Step Instruction           | 10H             | _                                     | Disabled.                                                                                                                                                                 |

• **Read Program Memory CRC (0EH)**—The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

## **OCD Control Register**

The OCD Control register controls the state of the OCD. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It also resets Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0823 Series device.

168

INTEN—Internal Precision Oscillator Enable

1 = Internal precision oscillator is enabled

0 = Internal precision oscillator is disabled

Reserved—R/W bits must be 0 during writes; 0 when read

WDTEN—Watchdog Timer Oscillator Enable

1 = Watchdog Timer oscillator is enabled

0 = Watchdog Timer oscillator is disabled

POFEN—Primary Oscillator Failure Detection Enable

1 = Failure detection and recovery of primary oscillator is enabled

0 = Failure detection and recovery of primary oscillator is disabled

WDFEN—Watchdog Timer Oscillator Failure Detection Enable

1 = Failure detection of Watchdog Timer oscillator is enabled

0 = Failure detection of Watchdog Timer oscillator is disabled

SCKSEL—System Clock Oscillator Select

000 = Internal precision oscillator functions as system clock at 5.53 MHz

001 = Internal precision oscillator functions as system clock at 32 kHz

010 = Reserved

011 = Watchdog Timer oscillator functions as system clock

100 = External clock signal on PB3 functions as system clock

101 = Reserved

110 = Reserved

111 = Reserved

# eZ8 CPU Instruction Set

# **Assembly Language Programming Introduction**

The eZ8 CPU assembly language provides a means for writing an application program without concern for actual memory addresses or machine instruction formats. A program written in assembly language is called a source program. Assembly language allows the use of symbolic addresses to identify memory locations. It also allows mnemonic codes (opcodes and operands) to represent the instructions themselves. The opcodes identify the instruction while the operands represent memory locations, registers, or immediate data values.

Each assembly language program consists of a series of symbolic commands called statements. Each statement can contain labels, operations, operands, and comments.

Labels are assigned to a particular instruction step in a source program. The label identifies that step in the program as an entry point for use by other instructions.

The assembly language also includes assembler directives that supplement the machine instruction. The assembler directives, or pseudo-ops, are not translated into a machine instruction. Rather, the pseudo-ops are interpreted as directives that control or assist the assembly process.

The source program is processed (assembled) by the assembler to obtain a machine language program called the object code. The object code is executed by the eZ8 CPU. An example segment of an assembly language program is detailed in the following example.

## Assembly Language Source Program Example

| JP START      | ; Everything after the semicolon is a comment.                                                                                                                                                                                                                                      |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| START:        | ; A label called 'START'. The first instruction (JP START) in this ; example causes program execution to jump to the point within the ; program where the START label occurs.                                                                                                       |

| LD R4, R7     | ; A Load (LD) instruction with two operands. The first operand,<br>; Working Register R4, is the destination. The second operand,<br>; Working Register R7, is the source. The contents of R7 is<br>; written into R4.                                                              |

| LD 234H, #%01 | ; Another Load (LD) instruction with two operands.<br>; The first operand, Extended Mode Register Address 234H,<br>; identifies the destination. The second operand, Immediate Data<br>; value 01H, is the source. The value 01H is written into the<br>; Register at address 234H. |

| Table 1 | 08. Bit | Manipu | lation Ir | nstructions   |

|---------|---------|--------|-----------|---------------|

|         | 00. Dit | manipu |           | 1311 40110113 |

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 109. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                         |

|----------|----------|---------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment Addresses |

## Table 110. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | HALT Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

| 184 |  |

|-----|--|

|-----|--|

| Assembly        |                                                                 | Addre   | Address Mode<br>Opcode(s) |            | Flags |   |              |     | – Fetch | Instr |   |        |

|-----------------|-----------------------------------------------------------------|---------|---------------------------|------------|-------|---|--------------|-----|---------|-------|---|--------|

| Mnemonic        | Symbolic Operation                                              | dst     | src                       | (Hex)      | С     | Ζ | S            | v   | D       | н     |   | Cycles |

| OR dst, src     | $dst \gets dst \: OR \: src$                                    | r       | r                         | 42         | _     | * | *            | 0   | _       | _     | 2 | 3      |

|                 |                                                                 | r       | lr                        | 43         | -     |   |              |     |         |       | 2 | 4      |

|                 |                                                                 | R       | R                         | 44         | -     |   |              |     |         |       | 3 | 3      |

|                 |                                                                 | R       | IR                        | 45         | _     |   |              |     |         |       | 3 | 4      |

|                 |                                                                 | R       | IM                        | 46         | -     |   |              |     |         |       | 3 | 3      |

|                 |                                                                 | IR      | IM                        | 47         | -     |   |              |     |         |       | 3 | 4      |

| ORX dst, src    | $dst \gets dst \: OR \: src$                                    | ER      | ER                        | 48         | -     | * | *            | 0   | _       | _     | 4 | 3      |

|                 |                                                                 | ER      | IM                        | 49         | _     |   |              |     |         |       | 4 | 3      |

| POP dst         | dst ← @SP                                                       | R       |                           | 50         | _     | _ | _            | _   | _       | _     | 2 | 2      |

|                 | $SP \leftarrow SP + 1$                                          | IR      |                           | 51         | -     |   |              |     |         |       | 2 | 3      |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                        | ER      |                           | D8         | -     | _ | _            | _   | _       | -     | 3 | 2      |

| PUSH src        | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                  | R       |                           | 70         | _     | _ | _            |     | _       | -     | 2 | 2      |

|                 |                                                                 | IR      |                           | 71         | -     |   |              |     |         |       | 2 | 3      |

|                 |                                                                 | IM      |                           | IF70       | _     |   |              |     |         |       | 3 | 2      |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER      |                           | C8         | _     | _ | _            | _   | _       | _     | 3 | 2      |

| RCF             | C ← 0                                                           |         |                           | CF         | 0     | _ | -            | _   | _       | _     | 1 | 2      |

| RET             | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |         |                           | AF         | _     | - | -            | _   | _       | _     | 1 | 4      |

| RL dst          | C                                                               | R       |                           | 90         | *     | * | *            | *   | -       | _     | 2 | 2      |

|                 |                                                                 | IR      |                           | 91         | -     |   |              |     |         |       | 2 | 3      |

| RLC dst         | C - D7D6D5D4D3D2D1D0 - dst                                      | R       |                           | 10         | *     | * | *            | r * | _       | _     | 2 | 2      |

|                 |                                                                 | IR      |                           | 11         | _     |   |              |     |         |       | 2 | 3      |

| Flags Notation: | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he resu | It of the c               | operation. |       |   | ese<br>et to |     | 0       |       |   |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

|                   |                               |                                 | 40 °C to +<br>therwise | 105 °C<br>specified) |            |                                                                                 |  |

|-------------------|-------------------------------|---------------------------------|------------------------|----------------------|------------|---------------------------------------------------------------------------------|--|

| Symbol            | Parameter                     | eter Minimum Typical Maximum Ur |                        | Units                | Conditions |                                                                                 |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4                             | _                      | _                    | V          | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |  |

| IIH               | Input Leakage<br>Current      | -                               | <u>+</u> 0.002         | <u>+</u> 5           | μA         | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |  |

| IIL               | Input Leakage<br>Current      | -                               | <u>+</u> 0.007         | <u>+</u> 5           | μA         | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -                               | -                      | <u>+</u> 5           | μA         |                                                                                 |  |

| I <sub>LED</sub>  | Controlled Current            | 1.8                             | 3                      | 4.5                  | mA         | {AFS2,AFS1} = {0,0}                                                             |  |

|                   | Drive                         | 2.8                             | 7                      | 10.5                 | mA         | {AFS2,AFS1} = {0,1}                                                             |  |

|                   |                               | 7.8                             | 13                     | 19.5                 | mA         | {AFS2,AFS1} = {1,0}                                                             |  |

|                   |                               | 12                              | 20                     | 30                   | mA         | {AFS2,AFS1} = {1,1}                                                             |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -                               | 8.0 <sup>2</sup>       | -                    | pF         |                                                                                 |  |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -                               | 8.0 <sup>2</sup>       | _                    | pF         |                                                                                 |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -                               | 9.5 <sup>2</sup>       | -                    | pF         |                                                                                 |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30                              | 100                    | 350                  | μA         | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |  |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD                             |                        |                      | V          | Voltage at which RAM retains static values; no reading or writing is allowed.   |  |

## Table 118. DC Characteristics (Continued)

Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

200

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  |        |                                                                                                                                                                   |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                             |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |

| Flash Byte Program Time                       | 20        | -                                    | 40      | μs     |                                                                                                                                                                   |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |

| Flash Mass Erase Time                         | 200       | -                                    | _       | ms     |                                                                                                                                                                   |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                   |

| Flash Row Program Time                        | _         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |

| Data Retention                                | 100       | _                                    | -       | years  | 25 °C                                                                                                                                                             |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |

## Table 123. Flash Memory Electrical Characteristics and Timing

## Table 124. Watchdog Timer Electrical Characteristics and Timing

|                     |                          | $T_A = -4$ | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |             |       |                                                                        |

|---------------------|--------------------------|------------|-----------------------------------------------------------------------------------------------------|-------------|-------|------------------------------------------------------------------------|

| Symbol              | Parameter                | Minimum    | Typical                                                                                             | Maximum     | Units | Conditions                                                             |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |            | 10                                                                                                  |             | kHz   |                                                                        |

| F <sub>WDT</sub>    | WDT Oscillator Error     |            |                                                                                                     | <u>+</u> 50 | %     |                                                                        |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98       | 1                                                                                                   | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C                     |

|                     |                          | 0.70       | 1                                                                                                   | 1.30        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50       | 1                                                                                                   | 1.50        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |

# UART Timing

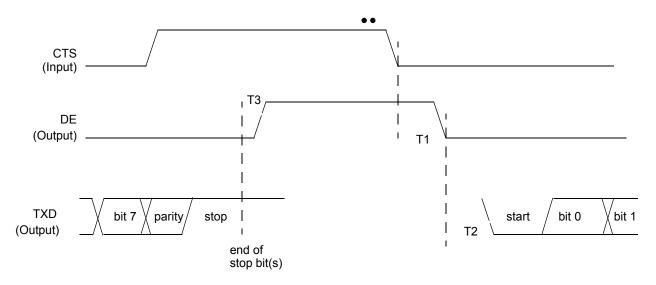

Figure 32 and Table 130 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

|                |                                                   | Delay (ns)        |                                |  |

|----------------|---------------------------------------------------|-------------------|--------------------------------|--|

| Parameter      | Abbreviation                                      | Minimum           | Maximum                        |  |

| UART           |                                                   |                   |                                |  |

| T <sub>1</sub> | CTS Fall to DE output delay                       | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) dela | y ± 5             |                                |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay        | ± 5               |                                |  |

## Table 130. UART Timing With CTS

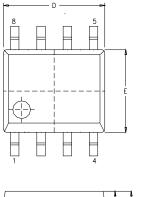

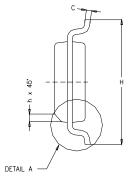

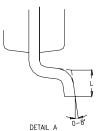

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIN | IETER                                                                               | INCH                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MIN    | MAX                                                                                 | MIN                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 1.55   | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                        | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.10   | 0.25                                                                                | 0.004                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.40   | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                        | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.36   | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                        | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.18   | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 4.80   | 4.98                                                                                | 0.189                                                                                                                                                                                                                                                                        | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3.81   | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                        | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.27   | BSC                                                                                 | .050 BSC                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 5.84   | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                        | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.25   | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                        | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.46   | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                        | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|        | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | 1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |  |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

## 237

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.