# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product StatusObsoleteCore ProcessoreZ8Core Size8-BitSpeedSMHzConnectivityirDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O16Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size-Nutage - Supply (Vcc/Vdd)2.7V ~ 3.6VOscillator TypeInternalOperating Temperature-A0°C ~ 105°C (TA)9.0°C ~ 105°C (TA)Mounting Type2.5°SOIC (0.295", 7.50mm Width)Supplier Device Package-Purchase URLhttps://www.exfl.com/product-detail/zilog/z8f0213sh005ec | Details                    |                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------|

| Core Size8-BitSpeed5MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O16Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Suppler Device Package-                                                                     | Product Status             | Obsolete                                                  |

| Speed5MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O16Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)                                                                                                          | Core Processor             | eZ8                                                       |

| ConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O16Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)                                                                                                                   | Core Size                  | 8-Bit                                                     |

| PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O16Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                       | Speed                      | 5MHz                                                      |

| Number of I/O16Program Memory Size2KB (2K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)                                                                                                                                                                                                    | Connectivity               | IrDA, UART/USART                                          |

| Program Memory Size2KB (2K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                           | Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Program Memory TypeFLASHEEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case2SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                            | Number of I/O              | 16                                                        |

| EEPROM Size-RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                                                  | Program Memory Size        | 2KB (2K x 8)                                              |

| RAM Size512 x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                                                              | Program Memory Type        | FLASH                                                     |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                             | EEPROM Size                | <u>.</u>                                                  |

| Data Converters-Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                  | RAM Size                   | 512 x 8                                                   |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                  | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Operating Temperature-40°C ~ 105°C (TA)Mounting TypeSurface MountPackage / Case20-SOIC (0.295", 7.50mm Width)Supplier Device Package-                                                                                                                                                                                                                                                                                                                                                         | Data Converters            | -                                                         |

| Mounting Type     Surface Mount       Package / Case     20-SOIC (0.295", 7.50mm Width)       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                   | Oscillator Type            | Internal                                                  |

| Package / Case     20-SOIC (0.295", 7.50mm Width)       Supplier Device Package     -                                                                                                                                                                                                                                                                                                                                                                                                         | Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Supplier Device Package -                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Mounting Type              | Surface Mount                                             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f0213sh005ec                                                                                                                                                                                                                                                                                                                                                                                                                        | Supplier Device Package    | -                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213sh005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

| Program Memory Address (Hex)                | Function                   |

|---------------------------------------------|----------------------------|

| 0002–0003                                   | Reset Vector               |

| 0004–0005                                   | WDT Interrupt Vector       |

| 0006–0007                                   | Illegal Instruction Trap   |

| 0008–0037                                   | Interrupt Vectors*         |

| 0038–003D                                   | Oscillator Fail Traps*     |

| 003E-03FF                                   | Program Memory             |

| ee Table 33 on page 54 for a list of the in | terrupt vectors and traps. |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

## **Data Memory**

Z8 Encore! XP<sup>®</sup> F0823 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

## **Flash Information Area**

Table 7 lists the Z8 Encore! XP F0823 Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address<br>(Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. Z8 Encore! XP F0823 Series Flash Memory Information Area Map

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

#### **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6    | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|------|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I  | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0    | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W  | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          | FC0H |     |              |       |          |          |      |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:  $PWM \text{ Period (s)} = \frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =  $\frac{PWM Value}{Reload Value} \times 100$

#### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the hold-ing register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

In COMPARE mode, the Timer Reload High and Low Byte registers store the 16-bit Compare value.

#### Table 51. Timer 0–1 Reload High Byte Register (TxRH)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|-----|-----|-------|------|-----|-----|-----|

| FIELD |     | TRH |     |       |      |     |     |     |

| RESET | 1   | 1   | 1   | 1     | 1    | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |     |     | F02H, | F0AH |     |     |     |

Table 52. Timer 0–1 Reload Low Byte Register (TxRL)

| BITS  | 7   | 6          | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------------|-----|-----|-----|-----|-----|-----|

| FIELD |     | TRL        |     |     |     |     |     |     |

| RESET | 1   | 1          | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W        | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     | F03H, F0BH |     |     |     |     |     |     |

TRH and TRL—Timer Reload Register High and Low

These two bytes form the 16-bit Reload value, {TRH[7:0], TRL[7:0]}. This value sets the maximum count value which initiates a timer reload to 0001H. In Compare mode, these two bytes form the 16-bit Compare value.

## **Timer 0-1 PWM High and Low Byte Registers**

The Timer 0-1 PWM High and Low Byte (TxPWMH and TxPWML) registers (Table 53 and Table 54) control pulse-width modulator (PWM) operations. These registers also store the Capture values for the CAPTURE and CAPTURE/COMPARE modes.

Table 53. Timer 0–1 PWM High Byte Register (TxPWMH)

| BITS  | 7   | 6    | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|------|-----|-------|------|-----|-----|-----|

| FIELD |     | PWMH |     |       |      |     |     |     |

| RESET | 0   | 0    | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W  | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |      |     | F04H, | F0CH |     |     |     |

### Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

### Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Flash Option Bit, see Flash Option Bits on page 141.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see Reset Status Register on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and Z8 Encore! XP F0823 Series are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

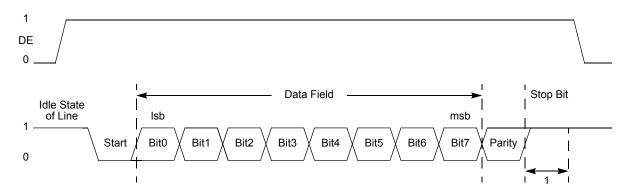

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

| BITS  | 7   | 6                           | 5 | 4    | 3     | 2 | 1 | 0 |

|-------|-----|-----------------------------|---|------|-------|---|---|---|

| FIELD |     |                             |   | COMP | _ADDR |   |   |   |

| RESET | 0   | 0                           | 0 | 0    | 0     | 0 | 0 | 0 |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |      |       |   |   |   |

| ADDR  |     | F45H                        |   |      |       |   |   |   |

#### Table 68. UART Address Compare Register (U0ADDR)

COMP ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

## UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (Table 69 and Table 70) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

#### Table 69. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     |     |     | BF  | RH  |     |     |     |

| RESET | 1   | 1   | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |     |     | F4  | 6H  |     |     |     |

#### Table 70. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|------|-----|-----|-----|-----|-----|-----|

| FIELD |     | BRL  |     |     |     |     |     |     |

| RESET | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |

| R/W   | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     | F47H |     |     |     |     |     |     |

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 71 provides information about data rate errors for 5.5296 MHz System Clock.

| 5.5296 MHz Syste         | m Clock                  |                      |           |

|--------------------------|--------------------------|----------------------|-----------|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |

| 1250.0                   | N/A                      | N/A                  | N/A       |

| 625.0                    | N/A                      | N/A                  | N/A       |

| 250.0                    | 1                        | 345.6                | 38.24     |

| 115.2                    | 3                        | 115.2                | 0.00      |

| 57.6                     | 6                        | 57.6                 | 0.00      |

| 38.4                     | 9                        | 38.4                 | 0.00      |

| 19.2                     | 18                       | 19.2                 | 0.00      |

| 9.60                     | 36                       | 9.60                 | 0.00      |

| 4.80                     | 72                       | 4.80                 | 0.00      |

| 2.40                     | 144                      | 2.40                 | 0.00      |

| 1.20                     | 288                      | 1.20                 | 0.00      |

| 0.60                     | 576                      | 0.60                 | 0.00      |

| 0.30                     | 1152                     | 0.30                 | 0.00      |

#### Table 71. UART Baud Rates

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Operation

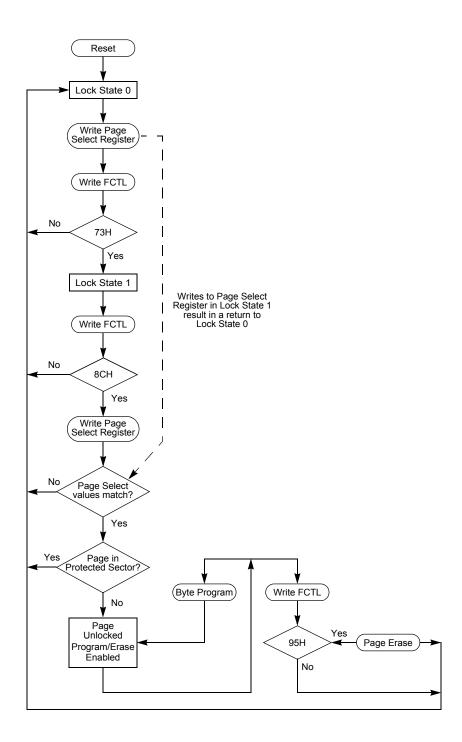

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flowchart in Figure 21 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

132

Figure 21. Flash Controller Operation Flowchart

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

#### **Flash Controller Bypass**

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Pro*gramming Support for Z8 Encore! (AN0117) available for download at <u>www.zilog.com</u>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select register

- Bits in the Flash Sector Protect register can be written to one or zero

- The second write of the Page Select register to unlock the Flash Controller is not necessary

- The Page Select register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control register

- **Caution:** For security reasons, Flash controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash controller must go through the unlock sequence again to select another page.

# **On-Chip Debugger**

Z8 Encore! XP<sup>®</sup> F0823 Series devices contain an integrated On-Chip Debugger (OCD) that provides advanced debugging features that include:

- Single pin interface

- Reading and writing of the register file

- Reading and writing of program and data memory

- Setting of breakpoints and watchpoints

- Executing eZ8 CPU instructions

- Debug pin sharing with general-purpose input-output function to maximize the pins available

# Architecture

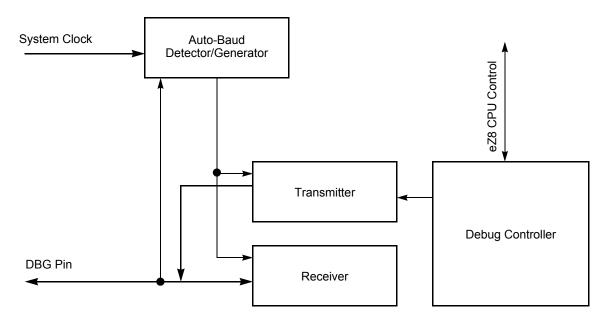

The on-chip debugger consists of four primary functional blocks: transmitter, receiver, auto-baud detector/generator, and debug controller. Figure 22 displays the architecture of the OCD.

Figure 22. On-Chip Debugger Block Diagram

is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0AH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

# **Opcode Maps**

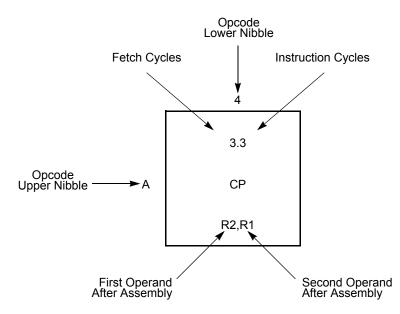

A description of the opcode map data and the abbreviations are provided in Figure 26. Figure 27 and Figure 28 provide information about each of the eZ8 CPU instructions. Table 116 lists Opcode Map abbreviations.

Figure 26. Opcode Map Cell Description

| 190 |

|-----|

|-----|

|                    |                                                         | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |            |            |       |                                                   |

|--------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------|------------|------------|-------|---------------------------------------------------|

| Symbol             | Parameter                                               | Minimum                                                                                             | Typical    | Maximum    | Units | Conditions                                        |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                                                                                                     | 5.53       |            | MHz   | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                                                                                                     | 32.7       |            | kHz   | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                                                                                                     | <u>+</u> 1 | <u>+</u> 4 | %     |                                                   |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                                                                                                     | 3          |            | μs    |                                                   |

#### Table 121. Internal Precision Oscillator Electrical Characteristics

RL 178

**RLC 178**

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

ADC data low bits (ADCDL) 125 flash control (FCTL) 137, 143, 144 flash high and low byte (FFREQH and FREEQL) 139 flash page select (FPS) 138, 139 flash status (FSTAT) 137 GPIO port A-H address (PxADDR) 44 GPIO port A-H alternate function sub-registers 46 GPIO port A-H control address (PxCTL) 45 GPIO port A-H data direction sub-registers 45 OCD control 161 OCD status 163 UARTx baud rate high byte (UxBRH) 110 UARTx baud rate low byte (UxBRL) 110 UARTx Control 0 (UxCTL0) 107, 110 UARTx control 1 (UxCTL1) 108 UARTx receive data (UxRXD) 105 UARTx status 0 (UxSTAT0) 105 UARTx status 1 (UxSTAT1) 106 UARTx transmit data (UxTXD) 104 Watchdog Timer control (WDTCTL) 90, 128 watch-dog timer control (WDTCTL) 167 Watchdog Timer reload high byte (WDTH) 91 Watchdog Timer reload low byte (WDTL) 91 Watchdog Timer reload upper byte (WD-TU) 91 register file 13 register pair 173 register pointer 174 reset and stop mode characteristics 22 and stop mode recovery 21 carry flag 176 sources 22 **RET 178** return 178

ADC data high byte (ADCDH) 124

rotate and shift instructions 178 rotate left 178 rotate left through carry 178 rotate right 178 rotate right through carry 178 RP 174 RR 173, 178 rr 173 RRC 178

# S

SBC 175 SCF 176, 177 second opcode map after 1FH 191 set carry flag 176, 177 set register pointer 177 shift right arithmetic 179 shift right logical 179 signal descriptions 9 single-sho conversion (ADC) 119 software trap 178 source operand 174 SP 174 SRA 179 src 174 SRL 179 **SRP 177** stack pointer 174 **STOP 177** STOP mode 31, 177 Stop Mode Recovery sources 26 using a GPIO port pin transition 27, 28 using Watchdog Timer time-out 27 SUB 175 subtract 175 subtract - extended addressing 175 subtract with carry 175 subtract with carry - extended addressing 175 **SUBX 175 SWAP 179** swap nibbles 179 symbols, additional 174