# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0213sh005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Dessiving Data using the Dallad Mathad                | 07         |

|-------------------------------------------------------|------------|

| Receiving Data using the Polled Method                |            |

| Clear To Send (CTS) Operation                         |            |

| MULTIPROCESSOR (9-Bit) Mode                           |            |

| External Driver Enable                                |            |

| UART Interrupts                                       |            |

| UART Baud Rate Generator                              |            |

| UART Control Register Definitions                     | 104        |

| UART Transmit Data Register                           |            |

| UART Receive Data Register                            |            |

| UART Status 0 Register                                | 105        |

| UART Status 1 Register                                |            |

| UART Control 0 and Control 1 Registers                |            |

| UART Address Compare Register                         |            |

| UART Baud Rate High and Low Byte Registers            |            |

| Infrared Encoder/Decoder                              |            |

| Architecture                                          | 113        |

| Operation                                             | 113        |

| Transmitting IrDA Data                                |            |

| Receiving IrDA Data                                   |            |

| Infrared Encoder/Decoder Control Register Definitions | 116        |

| Analog-to-Digital Converter                           | 117        |

| Architecture                                          | 117        |

| Operation                                             | 118        |

| Data Format                                           | 118        |

| Automatic Powerdown                                   |            |

| Single-Shot Conversion                                |            |

| Continuous Conversion                                 |            |

| Interrupts                                            |            |

| Calibration and Compensation                          |            |

| ADC Control Register Definitions                      |            |

| ADC Control Register 0                                |            |

| ADC Control/Status Register 1                         | 124        |

| ADC Data Low Bits Register                            |            |

|                                                       | 120        |

| Comparator                                            | 127        |

| Comparator                                            |            |

| Operation                                             | 127        |

| -                                                     | 127<br>127 |

# **CPU and Peripheral Overview**

## eZ8 CPU Features

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{\text{(R)}}$  instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory.

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks.

- Compatible with existing Z8 code.

- Expanded internal Register File allows access of up to 4 KB.

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C.

- Pipelined instruction fetch and execution.

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL.

- New instructions support 12-bit linear addressing of the Register file.

- Up to 10 MIPS operation.

- C-Compiler friendly.

- 2 to 9 clock cycles per instruction.

For more information on eZ8 CPU, refer to eZ8 CPU Core User Manual (UM0128) available for download at <u>www.zilog.com</u>.

## General-Purpose I/O

Z8 Encore! XP F0823 Series features 6 to 24 port pins (Ports A–C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

## Flash Controller

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\text{(R)}}$  F0823 Series 8-pin devices.

**Note:** All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 4 below describes 5 V-tolerance for the 20- and 28-pin packages only.

|                    |           |                               | Active<br>Low or          |                    |                                  | Schmitt-         |                        |                  |

|--------------------|-----------|-------------------------------|---------------------------|--------------------|----------------------------------|------------------|------------------------|------------------|

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>High            | Tristate<br>Output | Internal Pull-up<br>or Pull-down | Trigger<br>Input | Open Drain<br>Output   | 5 V<br>Tolerance |

| AVDD               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | N/A              |

| AVSS               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | NA               |

| DBG                | I/O       | I                             | N/A                       | Yes                | No                               | Yes              | Yes                    | Yes              |

| PA[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PA[7:2]<br>only  |

| PB[7:0]            | I/O       | Ι                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PB[7:6]<br>only  |

| PC[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PC[7:3]<br>only  |

| RESET              | I/O       | I/O<br>(defaults<br>to RESET) | Low (in<br>Reset<br>mode) | Yes (PD0<br>only)  | Alw <u>ays on</u> for<br>RESET   | Yes              | Always on for<br>RESET | Yes              |

| VDD                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

| VSS                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

#### Table 4. Pin Characteristics (20- and 28-pin Devices)

**Note:** *PB6 and PB7 are available only in the devices without ADC.*

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active Low<br>or Active<br>High | Tristate<br>Output | Internal Pull-up<br>or Pull-down                        | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                    | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------|--------------------|---------------------------------------------------------|------------------------------|---------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if key<br>sequence<br>detected) | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| RESET/<br>PA2      | I/O       | I/O<br>(defaults<br>to RESET)                                           | N/A                             | Yes                | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes                          | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

| VSS                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

# Table 5. Pin Characteristics (8-Pin Devices)

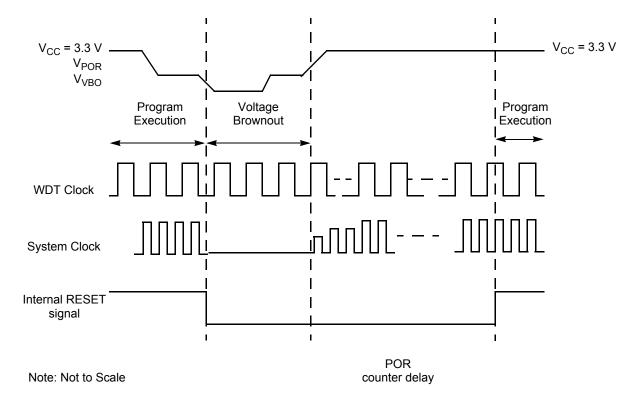

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is in NORMAL or STOP mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

# Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F0823 Series device is in STOP mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see Electrical Characteristics on page 193.

# **Reset Register Definitions**

## **Reset Status Register**

The Reset Status (RSTSTAT) register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer control register, which is writeonly (Table 12).

#### Table 12. Reset Status Register (RSTSTAT)

| BITS  | 7     | 6            | 5     | 4   | 3        | 2 | 1 | 0 |  |

|-------|-------|--------------|-------|-----|----------|---|---|---|--|

| FIELD | POR   | STOP         | WDT   | EXT | Reserved |   |   |   |  |

| RESET | See d | lescriptions | below | 0   | 0        | 0 | 0 | 0 |  |

| R/W   | R     | R            | R     | R   | R        | R | R | R |  |

| ADDR  |       | FFOH         |       |     |          |   |   |   |  |

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

#### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event is occurred. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

0 = The drains are enabled for any output mode (unless overridden by the alternate function).

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A–C High Drive Enable Sub-Registers

The Port A–C High Drive Enable sub-register (Table 23) is accessed through the Port A–C Control register by writing 04H to the Port A–C Address register. Setting the bits in the Port A–C High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–C High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 23. Port A–C High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6            | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|----------|--------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | PHDE7    | PHDE6        | PHDE5       | PHDE4         | PHDE3        | PHDE2         | PHDE1        | PHDE0    |

| RESET | 0        | 0            | 0           | 0             | 0            | 0             | 0            | 0        |

| R/W   | R/W      | R/W          | R/W         | R/W           | R/W          | R/W           | R/W          | R/W      |

| ADDR  | lf 04H i | n Port A–C / | Address Reg | gister, acces | sible throug | n the Port A- | -C Control F | Register |

PHDE[7:0]—Port High Drive Enabled.

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

#### Port A–C Stop Mode Recovery Source Enable Sub-Registers

The Port A–C Stop Mode Recovery Source Enable sub-register (Table 24) is accessed through the Port A–C Control register by writing 05H to the Port A–C Address register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6          | 5           | 4             | 3            | 2            | 1            | 0        |

|-------|----------|------------|-------------|---------------|--------------|--------------|--------------|----------|

| FIELD | PSMRE7   | PSMRE6     | PSMRE5      | PSMRE4        | PSMRE3       | PSMRE2       | PSMRE1       | PSMRE0   |

| RESET | 0        | 0          | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| ADDR  | lf 05H i | n Port A–C | Address Reg | gister, acces | sible throug | h the Port A | -C Control F | Register |

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |      |      |      | FC   | DH   |      |      |      |

#### Table 46. Interrupt Edge Select Register (IRQES)

IES*x*—Interrupt Edge Select *x*

0 = An interrupt request is generated on the falling edge of the PAx input or PDx

1 = An interrupt request is generated on the rising edge of the PAx input PDx where x indicates the specific GPIO port pin number (0 through 7)

## **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 47) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

Table 47. Shared Interrupt Select Register (IRQSS)

| BITS  | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|-------|----------|-------|----------|-----|-----|-----|-----|-----|

| FIELD | Reserved | PA6CS | Reserved |     |     |     |     |     |

| RESET | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| ADDR  |          |       |          | FC  | EH  |     |     |     |

PA6CS—PA6/Comparator Selection

0 = PA6 is used for the interrupt for PA6CS interrupt request

1 = The Comparator is used for the interrupt for PA6CS interrupt request

Reserved-Must be 0

### Interrupt Control Register

The Interrupt Control (IRQCTL) register (Table 48) contains the master enable bit for all interrupts.

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

Reserved—0 when read

FSTAT—Flash Controller Status 000000 = Flash Controller locked 000001 = First unlock command received (73H written) 000010 = Second unlock command received (8CH written) 000011 = Flash Controller unlocked 000100 = Sector protect register selected 001xxx = Program operation in progress 010xxx = Page erase operation in progress 100xxx = Mass erase operation in progress

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|------|-----|-----|-----|-----|-----|-----|

| FIELD | INFO_EN | PAGE |     |     |     |     |     |     |

| RESET | 0       | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |         |      |     | FF  | 9H  |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0.

# Flash Sector Protect Register

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |  |  |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|--|--|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |  |  |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |  |  |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |

| ADDR  | FF9H   |        |        |        |        |        |        |        |  |  |

Table 82. Flash Sector Protect Register (FPROT)

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 bytes Flash sector. For the Z8F08x3 devices, the upper 3 bits must be zero. For the Z8F04x3 devices all bits are used. For the Z8F02x3 devices, the upper 4 bits are unused. For the Z8F01x3 devices, the upper 6 bits are unused.

## Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

```

FFREQ[15:0] = {FFREQH[7:0],FFREQL[7:0]} = System Clock Frequency

1000

```

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

# Operation

The following sections describes the operation of OCD.

## **OCD** Interface

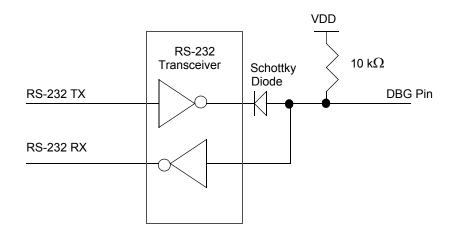

The OCD uses the DBG pin for communication with an external host. This one-pin interface is a bidirectional open-drain interface that transmits and receives data. Data transmission is half-duplex, in that transmit and receive cannot occur simultaneously. The serial data on the DBG pin is sent using the standard asynchronous data format defined in RS-232. This pin creates an interface from the Z8 Encore! XP F0823 Series products to the serial port of a host PC using minimal external hardware. Two different methods for connecting the DBG pin to an RS-232 interface are displayed in Figure 23 and Figure 24. The recommended method is the buffered implementation depicted in Figure 24. The DBG pin has a internal pull-up resistor which is sufficient for some applications (for more details on the pull-up current, see Electrical Characteristics on page 193). For OCD operation at higher data rates or in noisy systems, an external pull-up resistor is recommended.

**Caution:** For operation of the OCD, all power pins ( $V_{DD}$  and  $AV_{DD}$ ) must be supplied with power, and all ground pins ( $V_{SS}$  and  $AV_{SS}$ ) must be properly grounded. The DBG pin is opendrain and may require an external pull-up resistor to ensure proper operation.

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP<sup>®</sup> F0823 Series products. When this option is enabled, several of the OCD commands are disabled. Table 99 on page 162 is a summary of the OCD commands. Each OCD command is described in further detail in the bulleted list following this table. Table 99 on page 162 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|----------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                                                                                                                                                         |

| Reserved                   | 01H             | _                                     | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H             | Yes                                   | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H             | _                                     | -                                                                                                                                                                         |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                                                                                                                                                 |

| Read OCD Control Register  | 05H             | Yes                                   | -                                                                                                                                                                         |

| Write Program Counter      | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter       | 07H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Register             | 08H             | _                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register              | 09H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory       | 0AH             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory        | 0BH             | _                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory          | 0CH             | _                                     | Yes.                                                                                                                                                                      |

| Read Data Memory           | 0DH             | -                                     | -                                                                                                                                                                         |

| Read Program Memory CRC    | OEH             | -                                     | -                                                                                                                                                                         |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                         |

| Step Instruction           | 10H             | _                                     | Disabled.                                                                                                                                                                 |

is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0AH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

| Assembly        |                                                              | Addre      | ss Mode     | Opcode(s) | Flags |            |   |             |   | - Fetch | Instr.<br>Cycles |   |

|-----------------|--------------------------------------------------------------|------------|-------------|-----------|-------|------------|---|-------------|---|---------|------------------|---|

| Mnemonic        | Symbolic Operation                                           |            |             | (Hex)     | c z s |            |   | SVDH        |   |         |                  |   |

| XOR dst, src    | $dst \gets dst \ XOR \ src$                                  | r          | r           | B2        | _     | *          | * | 0           | - | _       | 2                | 3 |

|                 |                                                              | r          | lr          | B3        | _     |            |   |             |   |         | 2                | 4 |

|                 |                                                              | R          | R           | B4        | _     |            |   |             |   |         | 3                | 3 |

|                 |                                                              | R          | IR          | B5        | -     |            |   |             |   |         | 3                | 4 |

|                 |                                                              | R          | IM          | B6        | -     |            |   |             |   |         | 3                | 3 |

|                 |                                                              | IR         | IM          | B7        | _     |            |   |             |   |         | 3                | 4 |

| XORX dst, src   | $dst \gets dst \ XOR \ src$                                  | ER         | ER          | B8        | _     | *          | * | 0           | _ | _       | 4                | 3 |

|                 |                                                              | ER         | IM          | B9        | _     |            |   |             |   |         | 4                | 3 |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resu | It of the o | peration. | -     | = R<br>= S |   | t to<br>5 1 | 0 |         |                  |   |

### Table 115. eZ8 CPU Instruction Summary (Continued)

#### Table 117. Absolute Maximum Ratings (Continued)

| Parameter                                                      | Minimum Maximum | Units | Notes |

|----------------------------------------------------------------|-----------------|-------|-------|

| Maximum current into $V_{\text{DD}}$ or out of $V_{\text{SS}}$ | 125             | mA    |       |

|                                                                |                 |       |       |

Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 118 lists the DC characteristics of the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F0823 Series products. All voltages are referenced to V<sub>SS</sub>, the primary system ground.

#### Table 118. DC Characteristics

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | _                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | _                      | -                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                               |

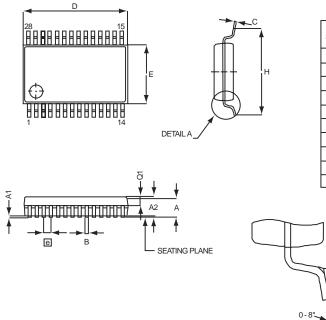

# Figure 42 displays the 28-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

|        |       | MILLIMETER | 2     | INCH       |       |       |  |  |

|--------|-------|------------|-------|------------|-------|-------|--|--|

| SYMBOL | MIN   | NOM        | MAX   | MIN        | NOM   | MAX   |  |  |

| А      | 1.73  | 1.86       | 1.99  | 0.068      | 0.073 | 0.078 |  |  |

| A1     | 0.05  | 0.13       | 0.21  | 0.002      | 0.005 | 0.008 |  |  |

| A2     | 1.68  | 1.73       | 1.78  | 0.066      | 0.068 | 0.070 |  |  |

| В      | 0.25  |            | 0.38  | 0.010      |       | 0.015 |  |  |

| С      | 0.09  | -          | 0.20  | 0.004      | 0.006 | 0.008 |  |  |

| D      | 10.07 | 10.20      | 10.33 | 0.397      | 0.402 | 0.407 |  |  |

| E      | 5.20  | 5.30       | 5.38  | 0.205      | 0.209 | 0.212 |  |  |

| е      |       | 0.65 TYP   |       | 0.0256 TYP |       |       |  |  |

| н      | 7.65  | 7.80       | 7.90  | 0.301      | 0.307 | 0.311 |  |  |

| L      | 0.63  | 0.75       | 0.95  | 0.025      | 0.030 | 0.037 |  |  |

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

Figure 42. 28-Pin Small Shrink Outline Package (SSOP)

| mber                                     |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |  |

|------------------------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|--|

| Part Number                              | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |  |

| Z8 Encore! XP with 2                     | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |  |

| Standard Temperature: 0 °C to 70 °C      |            |            |           |            |                        |                     |                |                     |  |

| Z8F0223PB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |

| Z8F0223QB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |

| Z8F0223SB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |

| Z8F0223SH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |

| Z8F0223HH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |

| Z8F0223PH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |

| Z8F0223SJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |

| Z8F0223HJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |

| Z8F0223PJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |

| Extended Temperatur                      | 'e: -40 °C | to 105 °C  | )         |            |                        |                     |                |                     |  |

| Z8F0223PB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |  |

| Z8F0223QB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |  |

| Z8F0223SB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |  |

| Z8F0223SH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |  |

| Z8F0223HH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |  |

| Z8F0223PH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |  |

| Z8F0223SJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |  |

| Z8F0223HJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |  |

| Z8F0223PJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |  |

| Replace C with G for Lead-Free Packaging |            |            |           |            |                        |                     |                |                     |  |

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Index

# Symbols

# 174 % 174 @ 174

# **Numerics**

10-bit ADC 4 40-lead plastic dual-inline package 214, 215

# Α

absolute maximum ratings 193 AC characteristics 197 ADC 175 architecture 117 automatic power-down 118 block diagram 118 continuous conversion 120 control register 122, 124 control register definitions 122 data high byte register 124 data low bits register 125 electrical characteristics and timing 201 operation 118 single-shot conversion 119 ADCCTL register 122, 124 ADCDH register 124 ADCDL register 125 ADCX 175 ADD 175 add - extended addressing 175 add with carry 175 add with carry - extended addressing 175 additional symbols 174 address space 13 ADDX 175 analog signals 10 analog-to-digital converter (ADC) 117 AND 177

ANDX 177 arithmetic instructions 175 assembly language programming 171 assembly language syntax 172

# В

B 174 b 173 baud rate generator, UART 103 **BCLR 176** binary number suffix 174 **BIT 176** bit 173 clear 176 manipulation instructions 176 set 176 set or clear 176 swap 176 test and jump 178 test and jump if non-zero 178 test and jump if zero 178 bit jump and test if non-zero 178 bit swap 178 block diagram 3 block transfer instructions 176 **BRK 178 BSET 176** BSWAP 176, 178 **BTJ 178 BTJNZ 178 BTJZ 178**

# С

CALL procedure 178 CAPTURE mode 84, 85 CAPTURE/COMPARE mode 85 cc 173 CCF 176 characteristics, electrical 193 clear 177 CLR 177 COM 177 227

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.