Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223hj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

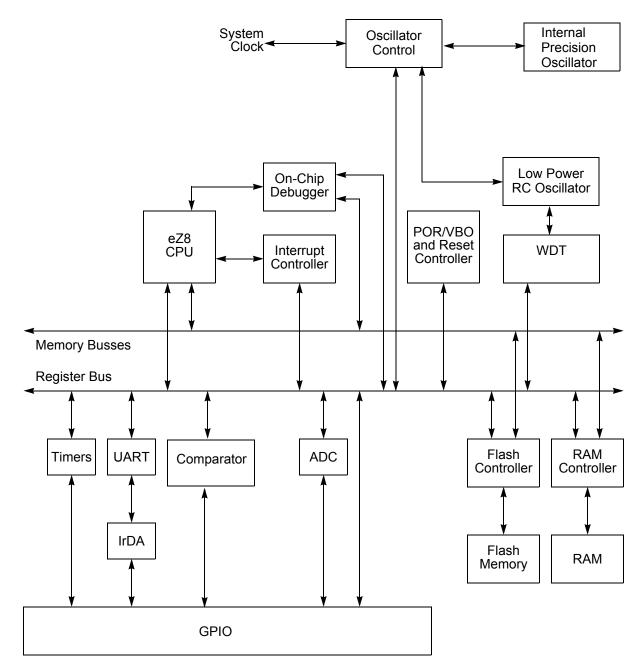

# Block Diagram

Figure 1 on page 3 displays the block diagram of the architecture of Z8 Encore! XP F0823 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0823 Series Block Diagram

## 13

# **Address Space**

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O port control registers.

- The Program Memory contains addresses for all memory locations having executable code and/or data.

- The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

# **Register File**

The Register File address space in the Z8 Encore! XP<sup>®</sup> MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256 B-1 KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

# **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. Z8 Encore! XP F0823 Series devices contain 1 KB to 8 KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash

| Address (Hex)   | Register Description    | Mnemonic | Reset (Hex) | Page No |

|-----------------|-------------------------|----------|-------------|---------|

| F91–FBF         | Reserved                | —        | XX          |         |

| Interrupt Contr | oller                   |          |             |         |

| FC0             | Interrupt Request 0     | IRQ0     | 00          | 58      |

| FC1             | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | 60      |

| FC2             | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | 61      |

| FC3             | Interrupt Request 1     | IRQ1     | 00          | 59      |

| FC4             | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | 62      |

| FC5             | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | 62      |

| FC6             | Interrupt Request 2     | IRQ2     | 00          | 60      |

| FC7             | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | 63      |

| FC8             | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | 63      |

| FC9–FCC         | Reserved                |          | XX          |         |

| FCD             | Interrupt Edge Select   | IRQES    | 00          | 64      |

| FCE             | Shared Interrupt Select | IRQSS    | 00          | 64      |

| FCF             | Interrupt Control       | IRQCTL   | 00          | 65      |

| GPIO Port A     |                         |          |             |         |

| FD0             | Port A Address          | PAADDR   | 00          | 43      |

| FD1             | Port A Control          | PACTL    | 00          | 45      |

| FD2             | Port A Input Data       | PAIN     | XX          | 45      |

| FD3             | Port A Output Data      | PAOUT    | 00          | 45      |

| GPIO Port B     |                         |          |             |         |

| FD4             | Port B Address          | PBADDR   | 00          | 43      |

| FD5             | Port B Control          | PBCTL    | 00          | 45      |

| FD6             | Port B Input Data       | PBIN     | XX          | 45      |

| FD7             | Port B Output Data      | PBOUT    | 00          | 45      |

| GPIO Port C     | ·                       |          |             |         |

| FD8             | Port C Address          | PCADDR   | 00          | 43      |

| FD9             | Port C Control          | PCCTL    | 00          | 45      |

| FDA             | Port C Input Data       | PCIN     | XX          | 45      |

| FDB             | Port C Output Data      | PCOUT    | 00          | 45      |

| FDC-FEF         | Reserved                | _        | XX          |         |

| Watchdog Time   |                         |          |             |         |

| FF0             | Reset Status            | RSTSTAT  | XX          | 90      |

| -               | Watchdog Timer Control  | WDTCTL   | XX          | 90      |

|                 | 0                       | WDTU     |             |         |

## Table 8. Register File Address Map (Continued)

## Architecture

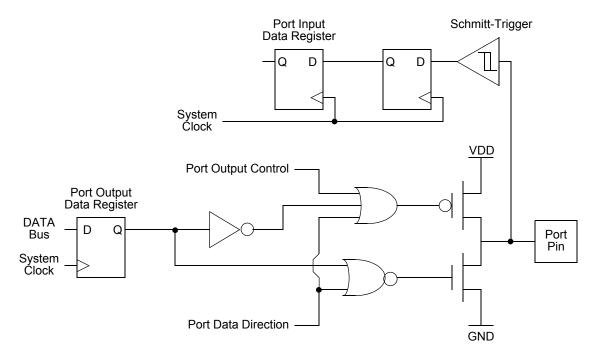

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 7. GPIO Port Pin Block Diagram

# **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function sub-registers configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 15 on page 39 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

| Port   | Pin   | Mnemonic          | Alternate Function<br>Description | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-------|-------------------|-----------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0   | TOIN              | Timer 0 Input                     | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |       | Reserved          |                                   | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |       | Reserved          |                                   | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |       | TOOUT             | Timer 0 Output Complement         | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1   | TOOUT             | Timer 0 Output                    | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |       | Reserved          |                                   | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |       | CLKIN             | External Clock Input              | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |       | Analog Functions* | ADC Analog Input/VREF             | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|        | PA2   | DE0               | UART 0 Driver Enable              | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        | RESET | External Reset    | AFS1[2]: 0                        | AFS2[2]: 1                                    |                                                     |

|        |       | T1OUT             | Timer 1 Output                    | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |       | Reserved          |                                   | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3   | CTS0              | UART 0 Clear to Send              | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |       | COUT              | Comparator Output                 | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |       | T1IN              | Timer 1 Input                     | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |       | Analog Functions* | ADC Analog Input                  | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4   | RXD0              | UART 0 Receive Data               | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |       | Reserved          |                                   | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |       | Reserved          |                                   | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |       | Analog Functions* | ADC/Comparator Input (N)          | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5   | TXD0              | UART 0 Transmit Data              | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |       | T1OUT             | Timer 1 Output Complement         | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |       | Reserved          |                                   | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |       | Analog Functions* | ADC/Comparator Input (P)          | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

|        |       |                   |                                   |                                               |                                                     |

## Table 16. Port Alternate Function Mapping (8-Pin Parts)

**Note:** \* Analog Functions include ADC inputs, ADC reference and comparator inputs. Also, alternate function selection as described in Port A–C Alternate Function Sub-Registers must be enabled.

Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Timer Oscillator Fail Trap

## **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all interrupts are enabled with identical interrupt priority (for example, all as Level 2 interrupts), the interrupt priority is assigned from highest to lowest as specified in Table 33 on page 54. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 33. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Timer Oscillator Fail Trap, and Illegal Instruction Trap always have highest (Level 3) priority.

### Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests: LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP<sup>®</sup> F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! XP F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 57 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 57. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value |            | e Time-Out Delay<br>VDT oscillator frequency) |

|------------------|------------------|------------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical    | Description                                   |

| 000004           | 4                | 400 μs     | Minimum time-out delay                        |

| FFFFF            | 16,777,215       | 28 minutes | Maximum time-out delay                        |

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **Flash Control Register Definitions**

# **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FTCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| BITS  | 7 | 6               | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|-----------------|---|----|----|---|---|---|--|

| FIELD |   | FCMD            |   |    |    |   |   |   |  |

| RESET | 0 | 0 0 0 0 0 0 0 0 |   |    |    |   |   |   |  |

| R/W   | W | w w w w w w w   |   |    |    |   |   |   |  |

| ADDR  |   |                 |   | FF | 8H |   |   |   |  |

Table 79. Flash Control Register (FCTL)

FCMD—Flash Command

73H = First unlock command

8CH = Second unlock command

95H = Page Erase command (must be third command in sequence to initiate Page Erase) 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase)

5EH = Enable Flash Sector Protect Register Access

## **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Table 80. Flash Status | Register (FSTAT) |

|------------------------|------------------|

|------------------------|------------------|

| BITS  | 7    | 6     | 5     | 4           | 3  | 2 | 1 | 0        |

|-------|------|-------|-------|-------------|----|---|---|----------|

| FIELD | Rese | erved | FSTAT |             |    |   |   |          |

| RESET | 0    | 0     | 0     | 0           | 0  | 0 | 0 | 0        |

| R/W   | R    | R     | R     | R R R R R R |    |   |   |          |

| ADDR  |      |       |       | FF          | 8H |   |   | <u>.</u> |

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

Table 86. Trim Bit Data Register (TRMDR)

| BITS  | 7   | 6                           | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|-----|-----------------------------|---|----|----|---|---|---|

| FIELD |     | TRMDR - Trim Bit Data       |   |    |    |   |   |   |

| RESET | 0   | 0                           | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |    |    |   |   |   |

| ADDR  |     |                             |   | FF | 7H |   |   |   |

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

## Flash Program Memory Address 0000H

Table 87. Flash Option Bits at Program Memory Address 0000H

| BITS      | 7                    | 6            | 5            | 4          | 3      | 2   | 1        | 0   |

|-----------|----------------------|--------------|--------------|------------|--------|-----|----------|-----|

| FIELD     | WDT_RES              | WDT_AO       | Rese         | erved      | VBO_AO | FRP | Reserved | FWP |

| RESET     | U                    | U            | U            | U          | U      | U   | U        | U   |

| R/W       | R/W                  | R/W          | R/W          | R/W        | R/W    | R/W | R/W      | R/W |

| ADDR      | Program Memory 0000H |              |              |            |        |     |          |     |

| Note: U = | Unchanged by         | y Reset. R/W | = Read/Write | <b>)</b> . |        |     |          |     |

WDT RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always ON

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the

Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

## Flash Program Memory Address 0001H

#### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6               | 5            | 4        | 3        | 2   | 1   | 0   |

|------------|----------------------|-----------------|--------------|----------|----------|-----|-----|-----|

| FIELD      | Reserved             |                 |              | XTLDIS   | Reserved |     |     |     |

| RESET      | U                    | U U U U U U U U |              |          |          |     | U   |     |

| R/W        | R/W                  | R/W             | R/W          | R/W      | R/W      | R/W | R/W | R/W |

| ADDR       | Program Memory 0001H |                 |              |          |          |     |     |     |

| Note:    = | Inchanged b          | V Reset R/M     | = Read/Write | <b>`</b> |          |     |     |     |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- $0 = Crystal \ oscillator \ is \ enabled \ during \ reset, \ resulting \ in \ longer \ reset \ timing$

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

## Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS        | 7                                               | 6               | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------|-------------------------------------------------|-----------------|-----|-----|-----|-----|-----|-----|--|

| FIELD       | Reserved                                        |                 |     |     |     |     |     |     |  |

| RESET       | U                                               | U U U U U U U U |     |     |     |     |     |     |  |

| R/W         | R/W                                             | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR        | Information Page Memory 0020H                   |                 |     |     |     |     |     |     |  |

| Note: U = U | lote: U = Unchanged by Reset. R/W = Read/Write. |                 |     |     |     |     |     |     |  |

Reserved—Altering this register may result in incorrect device operation.

## Trim Bit Address 0001H—Reserved

### Table 90. Trim Option Bits at 0001H

| BITS                                            | 7                             | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------------------------------------------------|-------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| FIELD                                           | Reserved                      |     |     |     |     |     |     |     |  |  |

| RESET                                           | U                             | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W                                             | R/W                           | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR                                            | Information Page Memory 0021H |     |     |     |     |     |     |     |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |     |     |     |     |     |     |     |  |  |

147

Reserved— Altering this register may result in incorrect device operation.

## Trim Bit Address 0002H

### Table 91. Trim Option Bits at 0002H (TIPO)

| BITS      | 7                                              | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-----------|------------------------------------------------|----------|---|---|---|---|---|---|--|--|--|

| FIELD     |                                                | IPO_TRIM |   |   |   |   |   |   |  |  |  |

| RESET     |                                                | U        |   |   |   |   |   |   |  |  |  |

| R/W       | R/W                                            |          |   |   |   |   |   |   |  |  |  |

| ADDR      | Information Page Memory 0022H                  |          |   |   |   |   |   |   |  |  |  |

| Note: U = | ote: U = Unchanged by Reset. R/W = Read/Write. |          |   |   |   |   |   |   |  |  |  |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

## Trim Bit Address 0003H—Reserved

## Trim Bit Address 0004H—Reserved

# **Zilog Calibration Data**

## **ADC Calibration Data**

## Table 92. ADC Calibration Bits

| BITS                                            | 7                                   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| FIELD                                           | ADC_CAL                             |     |     |     |     |     |     |     |  |  |

| RESET                                           | U                                   | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W                                             | R/W                                 | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR                                            | Information Page Memory 0060H–007DH |     |     |     |     |     |     |     |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                     |     |     |     |     |     |     |     |  |  |

ADC CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device

|                     |                                                    | T <sub>A</sub> = | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C      |                           | Conditions                                                                                   |  |

|---------------------|----------------------------------------------------|------------------|-------------------------------------|------------|---------------------------|----------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                                          | Minimum          | Typical                             | Maximum    | Units                     |                                                                                              |  |

|                     | Resolution                                         | 10               |                                     | _          | bits                      |                                                                                              |  |

|                     | Differential Nonlinearity<br>(DNL)                 | -1.0             | _                                   | 1.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |

|                     | Integral Nonlinearity (INL)                        | -3.0             | _                                   | 3.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |

|                     | Offset Error with Calibration                      |                  | <u>+</u> 1                          |            | LSB <sup>3</sup>          |                                                                                              |  |

|                     | Absolute Accuracy with Calibration                 |                  | <u>+</u> 3                          |            | LSB <sup>3</sup>          |                                                                                              |  |

| V <sub>REF</sub>    | Internal Reference Voltage                         | 1.0<br>2.0       | 1.1<br>2.2                          | 1.2<br>2.4 | V                         | REFSEL=01<br>REFSEL=10                                                                       |  |

| V <sub>REF</sub>    | Internal Reference<br>Variation with Temperature   |                  | <u>+</u> 1.0                        |            | %                         | Temperature variation<br>with V <sub>DD</sub> = 3.0                                          |  |

| V <sub>REF</sub>    | Internal Reference Voltage Variation with $V_{DD}$ |                  | <u>+</u> 0.5                        |            | %                         | Supply voltage variation<br>with T <sub>A</sub> = 30 °C                                      |  |

| R <sub>REFOUT</sub> | Reference Buffer Output<br>Impedance               |                  | 850                                 |            | Ω                         | When the internal<br>reference is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |

|                     | Single-Shot Conversion<br>Time                     | _                | 5129                                | -          | System<br>clock<br>cycles | All measurements but temperature sensor                                                      |  |

|                     |                                                    |                  | 10258                               |            |                           | Temperature sensor<br>measurement                                                            |  |

|                     | Continuous Conversion<br>Time                      | -                | 256                                 | -          |                           | All measurements but temperature sensor                                                      |  |

|                     |                                                    |                  | 512                                 |            |                           | Temperature sensor<br>measurement                                                            |  |

|                     | Signal Input Bandwidth                             | -                | 10                                  |            | kHz                       | As defined by -3 dB point                                                                    |  |

| R <sub>S</sub>      | Analog Source Impedance <sup>4</sup>               | _                | _                                   | 10         | kΩ                        | In unbuffered mode                                                                           |  |

## Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing

## UART Timing

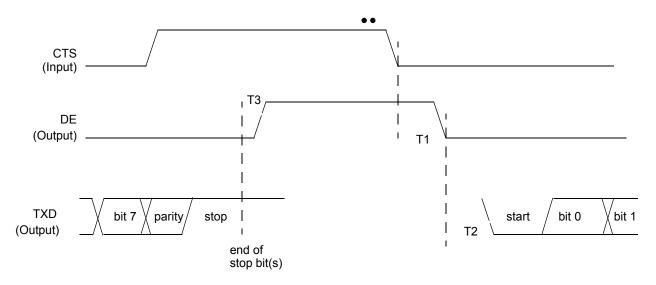

Figure 32 and Table 130 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

|                |                                                   | Delay (ns)        |                                |  |  |  |

|----------------|---------------------------------------------------|-------------------|--------------------------------|--|--|--|

| Parameter      | Abbreviation                                      | Minimum           | Maximum                        |  |  |  |

| UART           |                                                   |                   |                                |  |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                       | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) dela | y ± 5             |                                |  |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay        | ± 5               |                                |  |  |  |

### Table 130. UART Timing With CTS

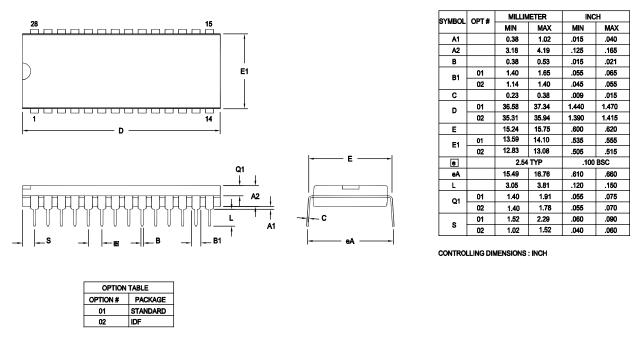

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

|                                          |             |           | S         | ots        | limers                 | 10-Bit A/D Channels | UART with IrDA | otion               |

|------------------------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash       | RAM       | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit /            | UART v         | Description         |

| Z8 Encore! XP with 4                     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur                      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0413PB005SC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu                       | re: -40 °C  | to 105 °0 | 0         |            |                        |                     |                |                     |

| Z8F0413PB005EC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |             |           |           |            |                        |                     |                |                     |

220

| mber                                     |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |

|------------------------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |

| Z8 Encore! XP with 2                     | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature                     | e: 0 °C to | 70 °C      |           |            |                        |                     |                |                     |

| Z8F0223PB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur                      | 'e: -40 °C | to 105 °C  | )         |            |                        |                     |                |                     |

| Z8F0223PB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |            |            |           |            |                        |                     |                |                     |

221