Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223pb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\text{(R)}}$  F0823 Series 8-pin devices.

**Note:** All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 4 below describes 5 V-tolerance for the 20- and 28-pin packages only.

|                    |           |                               | Active<br>Low or          |                    |                                  | Schmitt-         |                        |                  |

|--------------------|-----------|-------------------------------|---------------------------|--------------------|----------------------------------|------------------|------------------------|------------------|

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>High            | Tristate<br>Output | Internal Pull-up<br>or Pull-down | Trigger<br>Input | Open Drain<br>Output   | 5 V<br>Tolerance |

| AVDD               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | N/A              |

| AVSS               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | NA               |

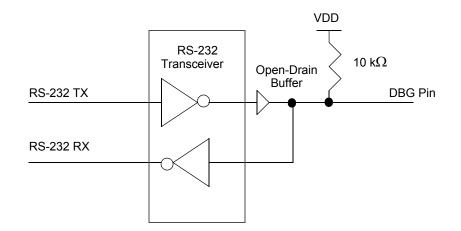

| DBG                | I/O       | I                             | N/A                       | Yes                | No                               | Yes              | Yes                    | Yes              |

| PA[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PA[7:2]<br>only  |

| PB[7:0]            | I/O       | Ι                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PB[7:6]<br>only  |

| PC[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PC[7:3]<br>only  |

| RESET              | I/O       | I/O<br>(defaults<br>to RESET) | Low (in<br>Reset<br>mode) | Yes (PD0<br>only)  | Alw <u>ays on</u> for<br>RESET   | Yes              | Always on for<br>RESET | Yes              |

| VDD                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

| VSS                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

### Table 4. Pin Characteristics (20- and 28-pin Devices)

**Note:** *PB6 and PB7 are available only in the devices without ADC.*

# **Low-Power Modes**

Z8 Encore! XP<sup>®</sup> F0823 Series products contain power-saving features. The highest level of power reduction is provided by the STOP mode, in which nearly all device functions are powered down. The next lower level of power reduction is provided by the HALT mode, in which the CPU is powered down.

Further power savings can be implemented by disabling individual peripheral blocks while in ACTIVE mode (defined as being in neither STOP nor HALT mode).

# **STOP Mode**

Executing the eZ8 CPU's Stop instruction places the device into STOP mode, powering down all peripherals except the Voltage Brownout detector, and the Watchdog Timer. These two blocks may also be disabled for additional power savings. In STOP mode, the operating characteristics are:

- Primary crystal oscillator and internal precision oscillator are stopped; XIN and XOUT (if previously enabled) are disabled, and PA0/PA1 revert to the states programmed by the GPIO registers.

- System clock is stopped.

- eZ8 CPU is stopped.

- Program counter (PC) stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate if enabled by the Oscillator Control Register.

- If enabled, the Watchdog Timer logic continues to operate.

- If enabled for operation in STOP mode by the associated Flash Option Bit, the Voltage Brownout protection circuit continues to operate.

- All other on-chip peripherals are idle.

To minimize current in STOP mode, all GPIO pins that are configured as digital inputs must be driven to one of the supply rails ( $V_{CC}$  or GND). Additionally, any GPIOs configured as outputs must also be driven to one of the supply rails. The device can be brought out of STOP mode using Stop Mode Recovery. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|-----|-----------------------------|---|---|---|---|---|---|--|--|--|

| FIELD |     | LEDEN[7:0]                  |   |   |   |   |   |   |  |  |  |

| RESET | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |  |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |  |  |

| ADDR  |     | F82H                        |   |   |   |   |   |   |  |  |  |

### Table 30. LED Drive Enable (LEDEN)

#### LEDEN[7:0]—LED Drive Enable

These bits determine which Port C pins are connected to an internal current sink.

0 = Tristate the Port C pin.

1= Connect controlled current sink to the Port C pin.

### LED Drive Level High Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 31). These two bits select between four programmable drive levels. Each pin is individually programmable.

### Table 31. LED Drive Level High Register (LEDLVLH)

| BITS  | 7            | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|--------------|------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD | LEDLVLH[7:0] |      |     |     |     |     |     |     |  |  |

| RESET | 0            | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |

| R/W   | R/W          | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |              | F83H |     |     |     |     |     |     |  |  |

LEDLVLH[7:0]—LED Level High Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA

10= 13 mA 11= 20 mA

# LED Drive Level Low Register

The LED Drive Level registers contain two control bits for each Port C pin (Table 32). These two bits select between four programmable drive levels. Each pin is individually programmable.

Reserved—Must be 0

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

### Table 39. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |  |  |  |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|--|--|--|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |  |  |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |  |  |  |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |  |  |  |

| ADDR  |          | FC2H  |              |               |               |          |          |        |  |  |  |

Reserved—0 when read

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

### **IRQ1 Enable High and Low Bit Registers**

Table 40 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 41 and Table 42) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register.

|            |            | -        |             |

|------------|------------|----------|-------------|

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 40. IRQ1 Enable and Priority Encoding

where x indicates the register bits from 0–7.

| BITS  | 7    | 6    | 5             | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------|------|---------------|---|---|---|---|---|--|--|

| FIELD | IRQE |      | Reserved      |   |   |   |   |   |  |  |

| RESET | 0    | 0    | 0 0 0 0 0 0 0 |   |   |   |   |   |  |  |

| R/W   | R/W  | R    | R R R R R R R |   |   |   |   |   |  |  |

| ADDR  |      | FCFH |               |   |   |   |   |   |  |  |

# Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

# Timers

Z8 Encore! XP<sup>®</sup> F0823 Series products contain up to two 16-bit reloadable timers that are used for timing, event counting, or generation of PWM signals. The timers' features include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the baud rate generator of the UART (if unused) also provides basic timing functionality. For information on using the baud rate generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 93.

# Architecture

Figure 9 displays the architecture of the timers. Timer Block Timer Data Bus Control Block Control Timer 16-Bit Interrupt, Compare Interrupt **Reload Register** PWM, and Timer Timer Output Output System Control Timer Clock 16-Bit Counter I Output with Prescaler Timer Complement Input Compare I Gate 16-Bit Input PWM/Compare Capture Input

Figure 9. Timer Block Diagram

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period. If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

### PWM Dual Output Mode

In PWM DUAL OUTPUT mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM Dual Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM Dual Output mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register

- Set the prescale value

- 0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

- 10 = Timer Interrupt only on defined Input Capture/Deassertion Events

- 11 = Timer Interrupt only on defined Reload/Compare Events

Reserved-Must be 0

#### PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

000 = No delay 001 = 2 cycles delay 010 = 4 cycles delay 011 = 8 cycles delay 100 = 16 cycles delay 101 = 32 cycles delay 110 = 64 cycles delay111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| BITS  | 7   | 6          | 5   | 4    | 3   | 2     | 1   | 0   |  |  |

|-------|-----|------------|-----|------|-----|-------|-----|-----|--|--|

| FIELD | TEN | TPOL       |     | PRES |     | TMODE |     |     |  |  |

| RESET | 0   | 0          | 0   | 0    | 0   | 0     | 0   | 0   |  |  |

| R/W   | R/W | R/W        | R/W | R/W  | R/W | R/W   | R/W | R/W |  |  |

| ADDR  |     | F07H, F0FH |     |      |     |       |     |     |  |  |

Table 56. Timer 0–1 Control Register 1 (TxCTL1)

TEN—Timer Enable

0 = Timer is disabled

1 = Timer enabled to count

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer

# **Receiving Data using the Interrupt-Driven Method**

The UART Receiver interrupt indicates the availability of new data (as well as error conditions). Follow the steps below to configure the UART receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupt in the applicable Interrupt Request register.

- 6. Write to the UART Control 1 Register to enable Multiprocessor (9-bit) mode functions, if appropriate.

- Set the Multiprocessor Mode Select (MPEN) to Enable MULTIPROCESSOR mode

- Set the Multiprocessor Mode Bits, MPMD[1:0], to select the acceptable address matching scheme

- Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikely to be useful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPROCESSOR modes only).

- 8. Write to the UART Control 0 register to:

- Set the receive enable bit (REN) to enable the UART for data reception

- Enable parity, if appropriate and if multiprocessor mode is not enabled, and select either even or odd parity

- 9. Execute an EI instruction to enable interrupts.

The UART is now configured for interrupt-driven data reception. When the UART Receiver interrupt is detected, the associated interrupt service routine (ISR) performs the following:

- 1. Checks the UART Status 0 register to determine the source of the interrupt error, break, or received data.

- 2. Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPROCESSOR (9-bit) mode, further actions may be required depending on the MULTIPROCESSOR mode bits MPMD[1:0].

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

### 118

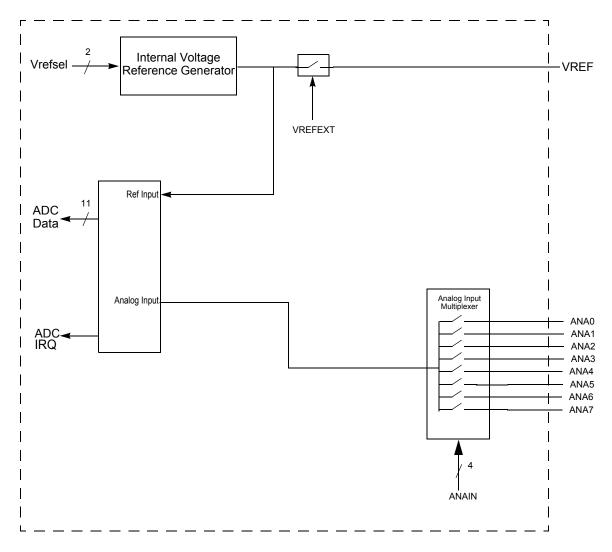

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

# **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

132

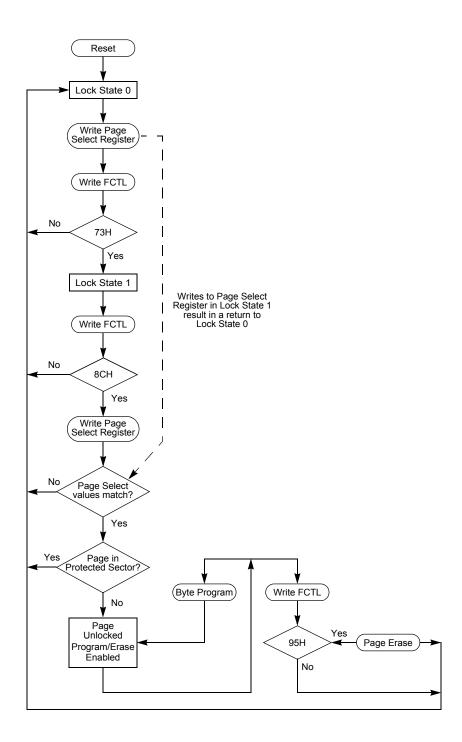

Figure 21. Flash Controller Operation Flowchart

# **Flash Control Register Definitions**

# **Flash Control Register**

The Flash Controller must be unlocked using the Flash Control (FTCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

| BITS  | 7    | 6             | 5 | 4  | 3    | 2 | 1 | 0 |  |  |  |  |  |

|-------|------|---------------|---|----|------|---|---|---|--|--|--|--|--|

| FIELD | FCMD |               |   |    |      |   |   |   |  |  |  |  |  |

| RESET | 0    | 0 0 0 0 0 0 0 |   |    |      |   |   |   |  |  |  |  |  |

| R/W   | W    | w w w w w w w |   |    |      |   |   |   |  |  |  |  |  |

| ADDR  |      |               |   | FF | FF8H |   |   |   |  |  |  |  |  |

Table 79. Flash Control Register (FCTL)

FCMD—Flash Command

73H = First unlock command

8CH = Second unlock command

95H = Page Erase command (must be third command in sequence to initiate Page Erase) 63H = Mass Erase command (must be third command in sequence to initiate Mass Erase)

5EH = Enable Flash Sector Protect Register Access

# **Flash Status Register**

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

| Table 80. Flash Status | Register (FSTAT) |

|------------------------|------------------|

|------------------------|------------------|

| BITS  | 7    | 6     | 5           | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|------|-------|-------------|---|---|---|---|---|--|--|

| FIELD | Rese | erved | FSTAT       |   |   |   |   |   |  |  |

| RESET | 0    | 0     | 0           | 0 | 0 | 0 | 0 | 0 |  |  |

| R/W   | R    | R     | R R R R R R |   |   |   |   |   |  |  |

| ADDR  |      | FF8H  |             |   |   |   |   |   |  |  |

Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

# Flash Program Memory Address 0001H

### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6           | 5            | 4        | 3        | 2   | 1   | 0   |  |

|------------|----------------------|-------------|--------------|----------|----------|-----|-----|-----|--|

| FIELD      |                      | Reserved    |              | XTLDIS   | Reserved |     |     |     |  |

| RESET      | U                    | U           | U            | U        | U U U U  |     |     |     |  |

| R/W        | R/W                  | R/W         | R/W          | R/W      | R/W      | R/W | R/W | R/W |  |

| ADDR       | Program Memory 0001H |             |              |          |          |     |     |     |  |

| Note:    = | Inchanged b          | V Reset R/M | = Read/Write | <b>`</b> |          |     |     |     |  |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

Figure 24. Interfacing the On-Chip Debugger's DBG Pin with an RS-232 Interface (2)

### **DEBUG Mode**

The operating characteristics of the devices in DEBUG mode are:

- The eZ8 CPU fetch unit stops, idling the eZ8 CPU, unless directed by the OCD to execute specific instructions

- The system clock operates unless in STOP mode

- All enabled on-chip peripherals operate unless in STOP mode

- Automatically exits HALT mode

- Constantly refreshes the Watchdog Timer, if enabled.

### **Entering DEBUG Mode**

The device enters DEBUG mode following the operations below:

- The device enters DEBUG mode after the eZ8 CPU executes a BRK (breakpoint) instruction

- If the DBG pin is held Low during the most recent clock cycle of System Reset, the part enters DEBUG mode upon exiting System Reset

**Note:** Holding the DBG pin Low for an additional 5000 (minimum) clock cycles after reset (making sure to account for any specified frequency error if using an internal oscillator) prevents a false interpretation of an Autobaud sequence (see OCD Auto-Baud Detector/Generator on page 154).

• If the PA2/RESET pin is held Low while a 32-bit key sequence is issued to the PA0/DBG pin, the DBG feature is unlocked. After releasing PA2/RESET, it is pulled high. At this

• **Read Program Memory CRC (0EH)**—The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

# **On-Chip Debugger Control Register Definitions**

# **OCD Control Register**

The OCD Control register controls the state of the OCD. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It also resets Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0823 Series device.

| 184 |  |

|-----|--|

|-----|--|

| Assembly        |                                                                 | Addre   | Address Mode<br>Opcode(s) |            |   | Flags |              |   |   |   | - Fetch | Instr |

|-----------------|-----------------------------------------------------------------|---------|---------------------------|------------|---|-------|--------------|---|---|---|---------|-------|

| Mnemonic        | Symbolic Operation                                              | dst     | src                       | (Hex)      | С | Ζ     | S            | v | D | н | Cycles  |       |

| OR dst, src     | $dst \gets dst \ OR \ src$                                      | r       | r                         | 42         | _ | *     | *            | 0 | _ | _ | 2       | 3     |

|                 |                                                                 | r       | lr                        | 43         | - |       |              |   |   |   | 2       | 4     |

|                 |                                                                 | R       | R                         | 44         | - |       |              |   |   |   | 3       | 3     |

|                 |                                                                 | R       | IR                        | 45         | _ |       |              |   |   |   | 3       | 4     |

|                 |                                                                 | R       | IM                        | 46         | - |       |              |   |   |   | 3       | 3     |

|                 |                                                                 | IR      | IM                        | 47         | - |       |              |   |   |   | 3       | 4     |

| ORX dst, src    | $dst \gets dst \: OR \: src$                                    | ER      | ER                        | 48         | - | *     | *            | 0 | _ | - | 4       | 3     |

|                 |                                                                 | ER      | IM                        | 49         | _ |       |              |   |   |   | 4       | 3     |

| POP dst         | dst $\leftarrow$ @SP<br>SP $\leftarrow$ SP + 1                  | R       |                           | 50         | _ | _     |              | _ | _ | _ | 2       | 2     |

|                 |                                                                 | IR      |                           | 51         | - |       |              |   |   |   | 2       | 3     |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                        | ER      |                           | D8         | _ | _     | _            | _ | _ | - | 3       | 2     |

| PUSH src        | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                  | R       |                           | 70         | _ | _     | _            | _ | - | - | 2       | 2     |

|                 |                                                                 | IR      |                           | 71         | - |       |              |   |   |   | 2       | 3     |

|                 |                                                                 | IM      |                           | IF70       | _ |       |              |   |   |   | 3       | 2     |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER      |                           | C8         | _ | _     | _            | _ | _ | _ | 3       | 2     |

| RCF             | C ← 0                                                           |         |                           | CF         | 0 | _     | -            | _ | _ | _ | 1       | 2     |

| RET             | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |         |                           | AF         | _ | -     | -            | _ | _ | _ | 1       | 4     |

| RL dst          | C D7D6D5D4D3D2D1D0                                              | R       |                           | 90         | * | *     | *            | * | - | _ | 2       | 2     |

|                 |                                                                 | IR      |                           | 91         | - |       |              |   |   |   | 2       | 3     |

| RLC dst         |                                                                 | R       |                           | 10         | * | *     | *            | * | _ | _ | 2       | 2     |

|                 | C D7D6D5D4D3D2D1D0                                              | IR      |                           | 11         | _ |       |              |   |   |   | 2       | 3     |

| Flags Notation: | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he resu | It of the c               | operation. |   |       | ese<br>et to |   | 0 |   |         |       |

### Table 115. eZ8 CPU Instruction Summary (Continued)

### Table 117. Absolute Maximum Ratings (Continued)

| Parameter                                                      | Minimum Maximum | Units | Notes |

|----------------------------------------------------------------|-----------------|-------|-------|

| Maximum current into $V_{\text{DD}}$ or out of $V_{\text{SS}}$ | 125             | mA    |       |

|                                                                |                 |       |       |

Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 118 lists the DC characteristics of the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F0823 Series products. All voltages are referenced to V<sub>SS</sub>, the primary system ground.

### Table 118. DC Characteristics

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |  |  |  |  |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |  |  |  |  |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |  |  |  |  |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |  |  |  |  |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |  |  |  |  |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |  |  |  |  |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | _                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |  |  |  |  |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | _                      | -                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |  |  |  |  |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                               |  |  |  |  |

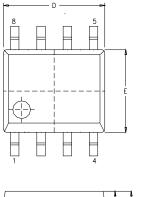

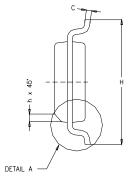

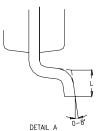

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIN | IETER                                                                               | INCH                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|--------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MIN    | MAX                                                                                 | MIN                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 1.55   | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                        | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.10   | 0.25                                                                                | 0.004                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1.40   | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                        | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.36   | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                        | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.18   | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 4.80   | 4.98                                                                                | 0.189                                                                                                                                                                                                                                                                        | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 3.81   | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                        | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1.27   | BSC                                                                                 | .050 BSC                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 5.84   | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                        | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.25   | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                        | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.46   | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                        | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

|        | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | 1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |  |  |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

| mber                                     |            |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |

|------------------------------------------|------------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash      | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |

| Z8 Encore! XP with 2                     | KB Flash   | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature                     | e: 0 °C to | 70 °C      |           |            |                        |                     |                |                     |

| Z8F0223PB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur                      | 'e: -40 °C | to 105 °C  | )         |            |                        |                     |                |                     |

| Z8F0223PB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EC                           | 2 KB       | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EC                           | 2 KB       | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EC                           | 2 KB       | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |            |            |           |            |                        |                     |                |                     |

221