Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223pj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date             | Revision<br>Level | Description                                                                                                                                                                                                       | Page No                              |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| March<br>2008    | 14                | Changed title to Z8 Encore! XP F0823 Series and the contents to match the title.                                                                                                                                  | •                                    |

| December<br>2007 | 13                | Updated title from Z8 Encore! 8K and 4K Series to Z8<br>Encore! XP Z8F0823 Series. Updated Figure 3, Table<br>15, Table 35, Table 59 through Table 61, Table 119,<br>and Part Number Suffix Designations section. | 8, 39,<br>59, 91,<br>196, and<br>226 |

| August<br>2007   | 12                | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                                            | 2, 42,<br>and 13                     |

| June 2007        | 11                | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                                        | All                                  |

| December<br>2006 | 10                | Updated Ordering Information chapter.                                                                                                                                                                             | 217                                  |

# **Table of Contents**

| Overview                                    | . 1 |

|---------------------------------------------|-----|

| Features                                    | . 1 |

| Part Selection Guide                        | . 2 |

| Block Diagram                               | . 3 |

| CPU and Peripheral Overview                 | . 4 |

| eZ8 CPU Features                            |     |

| General-Purpose I/O                         |     |

| Flash Controller                            |     |

| Internal Precision Oscillator               |     |

| Analog Comparator                           |     |

| Universal Asynchronous Receiver/Transmitter |     |

| Timers                                      |     |

| Interrupt Controller                        | . 5 |

| Reset Controller                            | . 6 |

| On-Chip Debugger                            |     |

| Pin Description                             | . 7 |

| Available Packages                          | . 7 |

| Pin Configurations                          |     |

| Signal Descriptions                         | . 9 |

| Pin Characteristics                         | 10  |

| Address Space                               | 13  |

| Register File                               | 13  |

| Program Memory                              | 13  |

| Data Memory                                 | 15  |

| Flash Information Area                      | 15  |

| Register Map                                | 17  |

| Reset and Stop Mode Recovery                | 21  |

| Reset Types                                 | 21  |

| Reset Sources                               | 22  |

| Power-On Reset                              |     |

| Voltage Brownout Reset                      |     |

| Watchdog Timer Reset                        |     |

| External Reset Input                        |     |

|                                             | 20  |

#### 1

# **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **General-Purpose Input/Output**

Z8 Encore! XP<sup>®</sup> F0823 Series products support a maximum of 24 port pins (Ports A–C) for general-purpose input/output (GPIO) operations. Each port contains control and data registers. The GPIO control registers determine data direction, open-drain, output drive current, programmable pull-ups, Stop Mode Recovery functionality, and alternate pin functions. Each port pin is individually programmable. In addition, the Port C pins are capable of direct LED drive at programmable drive strengths.

# **GPIO Port Availability By Device**

Table 14 lists the port pins available with each device and package type.

| Devices                                                                                      | Package | 10-Bit ADC | Port A | Port B | Port C | Total I/O |

|----------------------------------------------------------------------------------------------|---------|------------|--------|--------|--------|-----------|

| Z8F0823SB, Z8F0823PB<br>Z8F0423SB, Z8F0423PB<br>Z8F0223SB, Z8F0223PB<br>Z8F0123SB, Z8F0123PB | 8-pin   | Yes        | [5:0]  | No     | No     | 6         |

| Z8F0813SB, Z8F0813PB<br>Z8F0413SB, Z8F0413PB<br>Z8F0213SB, Z8F0213PB<br>Z8F0113SB, Z8F011vPB | 8-pin   | No         | [5:0]  | No     | No     | 6         |

| Z8F0823PH, Z8F0823HH<br>Z8F0423PH, Z8F0423HH<br>Z8F0223PH, Z8F0223HH<br>Z8F0123PH, Z8F0123HH | 20-pin  | Yes        | [7:0]  | [3:0]  | [3:0]  | 16        |

| Z8F0813PH, Z8F0813HH<br>Z8F0413PH, Z8F0413HH<br>Z8F0213PH, Z8F0213HH<br>Z8F0113PH, Z8F0113HH | 20-pin  | No         | [7:0]  | [3:0]  | [3:0]  | 16        |

| Z8F0823PJ, Z8F0823SJ<br>Z8F0423PJ, Z8F0423SJ<br>Z8F0223PJ, Z8F0223SJ<br>Z8F0123PJ, Z8F0123SJ | 28-pin  | Yes        | [7:0]  | [5:0]  | [7:0]  | 22        |

| Z8F0813PJ, Z8F0813SJ<br>Z8F0413PJ, Z8F0413SJ<br>Z8F0213PJ, Z8F0213SJ<br>Z8F0113PJ, Z8F0113SJ | 28-pin  | No         | [7:0]  | [7:0]  | [7:0]  | 24        |

Table 14. Port Availability by Device and Package Type

| Port   | Pin | Mnemonic          | Alternate Function<br>Description | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-----|-------------------|-----------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                     | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |     | Reserved          |                                   | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |     | Reserved          |                                   | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |     | TOOUT             | Timer 0 Output Complement         | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1 | TOOUT             | Timer 0 Output                    | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |     | Reserved          |                                   | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |     | CLKIN             | External Clock Input              | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input/VREF             | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

| PA2    | PA2 | DE0               | UART 0 Driver Enable              | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        |     | RESET             | External Reset                    | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|        |     | T1OUT             | Timer 1 Output                    | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |     | Reserved          |                                   | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3 | CTS0              | UART 0 Clear to Send              | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |     | COUT              | Comparator Output                 | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |     | T1IN              | Timer 1 Input                     | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input                  | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4 | RXD0              | UART 0 Receive Data               | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |     | Reserved          |                                   | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |     | Reserved          |                                   | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (N)          | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5 | TXD0              | UART 0 Transmit Data              | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |     | T1OUT             | Timer 1 Output Complement         | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |     | Reserved          |                                   | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (P)          | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

|        |     |                   |                                   |                                               |                                                     |

#### Table 16. Port Alternate Function Mapping (8-Pin Parts)

**Note:** \* Analog Functions include ADC inputs, ADC reference and comparator inputs. Also, alternate function selection as described in Port A–C Alternate Function Sub-Registers must be enabled.

| BITS  | 7        | 6                           | 5             | 4             | 3             | 2              | 1            | 0        |  |

|-------|----------|-----------------------------|---------------|---------------|---------------|----------------|--------------|----------|--|

| FIELD | PAFS17   | PAFS16                      | PAFS15        | PAFS14        | PAFS13        | PAFS12         | PAFS11       | PAFS10   |  |

| RESET |          | 00H (all                    | ports of 20/2 | 28 pin devic  | es); 04H (Pc  | ort A of 8-pin | device)      |          |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |               |               |               |                |              |          |  |

| ADDR  | lf 07H i | n Port A–C                  | Address Reg   | gister, acces | sible through | n the Port A-  | -C Control F | ≀egister |  |

Table 26. Port A–C Alternate Function Set 1 Sub-Registers (PxAFS1)

PAFS1[7:0]—Port Alternate Function Set to 1

0 = Port Alternate Function selected as defined in Table 14 (see GPIO Alternate Functions on page 36).

1 = Port Alternate Function selected as defined in Table 14 (see GPIO Alternate Functions on page 36).

#### Port A–C Alternate Function Set 2 Sub-Registers

The Port A–C Alternate Function Set 2 sub-register (Table 27) is accessed through the Port A–C Control register by writing 08H to the Port A–C Address register. The Alternate Function Set 2 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register is defined in Table 14 in the section GPIO Alternate Functions on page 36.

Table 27. Port A–C Alternate Function Set 2 Sub-Registers (PxAFS2)

| BITS  | 7        | 6                           | 5             | 4             | 3            | 2              | 1            | 0        |  |

|-------|----------|-----------------------------|---------------|---------------|--------------|----------------|--------------|----------|--|

| FIELD | PAFS27   | PAFS26                      | PAFS25        | PAFS24        | PAFS23       | PAFS22         | PAFS21       | PAFS20   |  |

| RESET |          | 00H (all                    | ports of 20/2 | 28 pin devic  | es); 04H (Pc | ort A of 8-pin | device)      |          |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |               |               |              |                |              |          |  |

| ADDR  | lf 08H i | n Port A–C /                | Address Reg   | gister, acces | sible throug | n the Port A-  | -C Control F | Register |  |

PAFS2[7:0]—Port Alternate Function Set 2

0 = Port Alternate Function selected as defined in Table 14 (see GPIO Alternate Functions on page 36).

1 = Port Alternate Function selected as defined in Table 14.

## Port A–C Input Data Registers

Reading from the Port A–C Input Data registers (Table 28) returns the sampled values from the corresponding port pins. The Port A–C Input Data registers are read-only. The value returned for any unused ports is 0. Unused ports include those missing on the 8- and 28-pin packages, as well as those missing on the ADC-enabled 28-pin packages.

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| BITS  | 7   | 6                           | 5 | 4     | 3    | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|-------|------|---|---|---|--|

| FIELD |     | PWML                        |   |       |      |   |   |   |  |

| RESET | 0   | 0                           | 0 | 0     | 0    | 0 | 0 | 0 |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |       |      |   |   |   |  |

| ADDR  |     |                             |   | F05H, | F0DH |   |   |   |  |

#### Table 54. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

### **Timer 0–1 Control Registers**

#### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input Capture event.

Table 55. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6    | 5    | 4        | 3    | 2   | 1   | 0      |

|-------|---------|------|------|----------|------|-----|-----|--------|

| FIELD | TMODEHI | TICO | NFIG | Reserved | PWMD |     |     | INPCAP |

| RESET | 0       | 0    | 0    | 0        | 0    | 0   | 0   | 0      |

| R/W   | R/W     | R/W  | R/W  | R/W      | R/W  | R/W | R/W | R/W    |

| ADDR  |         |      |      | F06H,    | F0EH |     |     |        |

#### TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value. See the TxCTL1 register description for more details.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7 | 6             | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|---------------|---|----|----|---|---|---|--|

| FIELD |   | TXD           |   |    |    |   |   |   |  |

| RESET | Х | Х             | Х | Х  | Х  | Х | Х | Х |  |

| R/W   | W | w w w w w w w |   |    |    |   |   |   |  |

| ADDR  |   |               |   | F4 | 0H |   |   |   |  |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 71 provides information about data rate errors for 5.5296 MHz System Clock.

| 5.5296 MHz Syste         | m Clock                  |                      |           |

|--------------------------|--------------------------|----------------------|-----------|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |

| 1250.0                   | N/A                      | N/A                  | N/A       |

| 625.0                    | N/A                      | N/A                  | N/A       |

| 250.0                    | 1                        | 345.6                | 38.24     |

| 115.2                    | 3                        | 115.2                | 0.00      |

| 57.6                     | 6                        | 57.6                 | 0.00      |

| 38.4                     | 9                        | 38.4                 | 0.00      |

| 19.2                     | 18                       | 19.2                 | 0.00      |

| 9.60                     | 36                       | 9.60                 | 0.00      |

| 4.80                     | 72                       | 4.80                 | 0.00      |

| 2.40                     | 144                      | 2.40                 | 0.00      |

| 1.20                     | 288                      | 1.20                 | 0.00      |

| 0.60                     | 576                      | 0.60                 | 0.00      |

| 0.30                     | 1152                     | 0.30                 | 0.00      |

#### Table 71. UART Baud Rates

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 93.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO port alternate function for the corresponding pin.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### 118

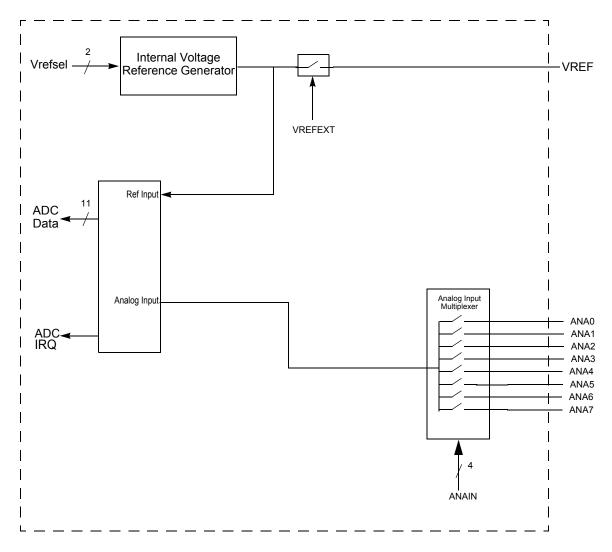

Figure 19. Analog-to-Digital Converter Block Diagram

## Operation

## **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

132

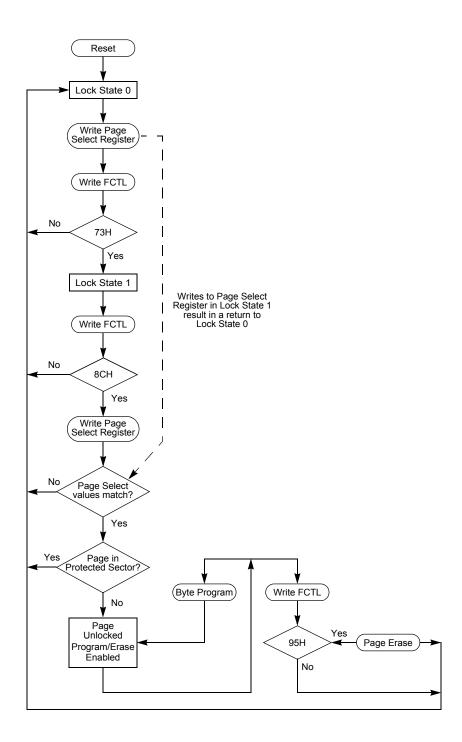

Figure 21. Flash Controller Operation Flowchart

Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

## Flash Program Memory Address 0001H

#### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6           | 5            | 4        | 3        | 2   | 1   | 0   |

|------------|----------------------|-------------|--------------|----------|----------|-----|-----|-----|

| FIELD      | Reserved             |             |              | XTLDIS   | Reserved |     |     |     |

| RESET      | U                    | U           | U            | U        | U        | U   | U   | U   |

| R/W        | R/W                  | R/W         | R/W          | R/W      | R/W      | R/W | R/W | R/W |

| ADDR       | Program Memory 0001H |             |              |          |          |     |     |     |

| Note:    = | Inchanged b          | V Reset R/M | = Read/Write | <b>`</b> |          |     |     |     |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

#### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|        |                     | T <sub>A</sub> = | V <sub>DD</sub> = 3.0 V to 3.6 V<br>T <sub>A</sub> = 0 °C to +70 °C<br>(unless otherwise stated) |                 |       |                                      |

|--------|---------------------|------------------|--------------------------------------------------------------------------------------------------|-----------------|-------|--------------------------------------|

| Symbol | Parameter           | Minimum          | Typical                                                                                          | Maximum         | Units | Conditions                           |

| Zin    | Input Impedance     | -                | 150                                                                                              |                 | kΩ    | In unbuffered mode at 20 $\rm MHz^5$ |

|        |                     |                  |                                                                                                  |                 |       |                                      |

| Vin    | Input Voltage Range | 0                |                                                                                                  | V <sub>DD</sub> | V     | Unbuffered Mode                      |

|        |                     |                  |                                                                                                  |                 |       |                                      |

Notes

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30 °C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| Table 126. | Comparator | Electrical | Characteristics |

|------------|------------|------------|-----------------|

|------------|------------|------------|-----------------|

|                   |                     |                 | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |                    |               |                    |  |

|-------------------|---------------------|-----------------|------------------------------------------------------------------------|--------------------|---------------|--------------------|--|

| Symbol            | Parameter           | Minimum         | Typical                                                                | Maximum            | Units         | Conditions         |  |

| V <sub>OS</sub>   | Input DC Offset     |                 | 5                                                                      |                    | mV            |                    |  |

| V <sub>CREF</sub> |                     |                 | <u>+</u> 5                                                             |                    | %             | 20-/28-pin devices |  |

| Reference Voltage |                     | <u>+</u> 3      |                                                                        | %                  | 8-pin devices |                    |  |

| T <sub>PROP</sub> | Propagation Delay   |                 | 200                                                                    |                    | ns            |                    |  |

| V <sub>HYS</sub>  | Input Hysteresis    |                 | 4                                                                      |                    | mV            |                    |  |

| V <sub>IN</sub>   | Input Voltage Range | V <sub>SS</sub> |                                                                        | V <sub>DD</sub> -1 | V             |                    |  |

## General Purpose I/O Port Input Data Sample Timing

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

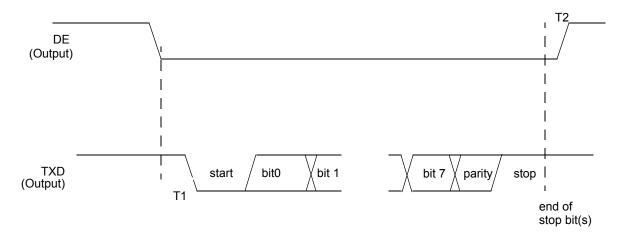

Figure 33 and Table 131 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 33. UART Timing Without CTS

| Table 131. UART | Timing Without CTS |  |

|-----------------|--------------------|--|

|                 |                    |  |

|                |                                                                        | Delay (ns)        |            |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |

| UART           |                                                                        |                   |            |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |