Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223sb005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Warning:** DO NOT USE IN LIFE SUPPORT

## LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

## As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| Flash Information Area                                        | . 130 |

|---------------------------------------------------------------|-------|

| Operation                                                     | . 131 |

| Flash Operation Timing Using the Flash Frequency Registers    |       |

| Flash Code Protection Against External Access                 |       |

| Flash Code Protection Against Accidental Program and Erasure  |       |

| Byte Programming                                              |       |

| Page Erase                                                    |       |

| Mass Erase                                                    |       |

| Flash Controller Bypass                                       |       |

| Flash Controller Behavior in DEBUG Mode                       |       |

| Flash Control Register Definitions                            |       |

| Flash Control Register                                        |       |

| Flash Status Register                                         |       |

| Flash Page Select Register      Flash Sector Protect Register |       |

| Flash Frequency High and Low Byte Registers                   |       |

|                                                               |       |

| Flash Option Bits                                             |       |

| Operation                                                     |       |

| Option Bit Configuration By Reset                             |       |

| Option Bit Types                                              |       |

| Reading the Flash Information Page                            |       |

| Flash Option Bit Control Register Definitions                 |       |

| Trim Bit Address Register                                     | -     |

| Trim Bit Data Register                                        |       |

| Flash Option Bit Address Space                                |       |

| Flash Program Memory Address 0000H                            |       |

| Flash Program Memory Address 0001H                            |       |

| Trim Bit Address Space                                        |       |

| Trim Bit Address 0000H—Reserved                               |       |

| Trim Bit Address 0001H—Reserved                               |       |

| Trim Bit Address 0002H                                        |       |

| Trim Bit Address 00031—Reserved                               |       |

|                                                               |       |

| Zilog Calibration Data                                        |       |

| Serialization Data                                            |       |

| Randomized Lot Identifier                                     |       |

|                                                               |       |

| On-Chip Debugger                                              |       |

| Architecture                                                  | . 151 |

|                                                               |       |

### viii

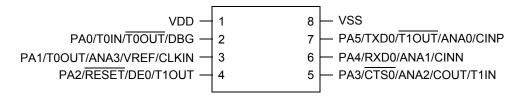

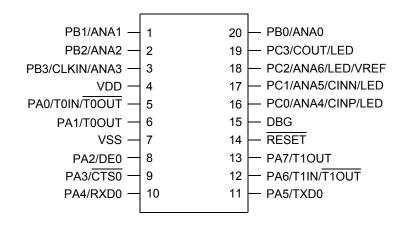

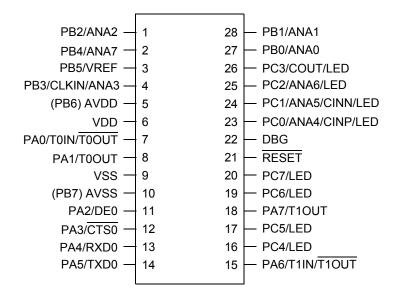

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

#### Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

## Figure 3. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package\*

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\text{(R)}}$  F0823 Series 8-pin devices.

**Note:** All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 4 below describes 5 V-tolerance for the 20- and 28-pin packages only.

|                    |           |                               | Active<br>Low or          |                    |                                  | Schmitt-         |                        |                  |

|--------------------|-----------|-------------------------------|---------------------------|--------------------|----------------------------------|------------------|------------------------|------------------|

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>High            | Tristate<br>Output | Internal Pull-up<br>or Pull-down | Trigger<br>Input | Open Drain<br>Output   | 5 V<br>Tolerance |

| AVDD               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | N/A              |

| AVSS               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | NA               |

| DBG                | I/O       | I                             | N/A                       | Yes                | No                               | Yes              | Yes                    | Yes              |

| PA[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PA[7:2]<br>only  |

| PB[7:0]            | I/O       | Ι                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PB[7:6]<br>only  |

| PC[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PC[7:3]<br>only  |

| RESET              | I/O       | I/O<br>(defaults<br>to RESET) | Low (in<br>Reset<br>mode) | Yes (PD0<br>only)  | Alw <u>ays on</u> for<br>RESET   | Yes              | Always on for<br>RESET | Yes              |

| VDD                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

| VSS                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

## Table 4. Pin Characteristics (20- and 28-pin Devices)

**Note:** *PB6 and PB7 are available only in the devices without ADC.*

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 151.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 167), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0], and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see Oscillator Control Register Definitions on page 167) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

| Port   | Pin | Mnemonic          | Alternate Function<br>Description | Alternate<br>Function Select<br>Register AFS1 | Alternate<br>Function<br>Select<br>Register<br>AFS2 |

|--------|-----|-------------------|-----------------------------------|-----------------------------------------------|-----------------------------------------------------|

| Port A | PA0 | TOIN              | Timer 0 Input                     | AFS1[0]: 0                                    | AFS2[0]: 0                                          |

|        |     | Reserved          |                                   | AFS1[0]: 0                                    | AFS2[0]: 1                                          |

|        |     | Reserved          |                                   | AFS1[0]: 1                                    | AFS2[0]: 0                                          |

|        |     | TOOUT             | Timer 0 Output Complement         | AFS1[0]: 1                                    | AFS2[0]: 1                                          |

|        | PA1 | TOOUT             | Timer 0 Output                    | AFS1[1]: 0                                    | AFS2[1]: 0                                          |

|        |     | Reserved          |                                   | AFS1[1]: 0                                    | AFS2[1]: 1                                          |

|        |     | CLKIN             | External Clock Input              | AFS1[1]: 1                                    | AFS2[1]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input/VREF             | AFS1[1]: 1                                    | AFS2[1]: 1                                          |

|        | PA2 | DE0               | UART 0 Driver Enable              | AFS1[2]: 0                                    | AFS2[2]: 0                                          |

|        |     | RESET             | External Reset                    | AFS1[2]: 0                                    | AFS2[2]: 1                                          |

|        |     | T1OUT             | Timer 1 Output                    | AFS1[2]: 1                                    | AFS2[2]: 0                                          |

|        |     | Reserved          |                                   | AFS1[2]: 1                                    | AFS2[2]: 1                                          |

|        | PA3 | CTS0              | UART 0 Clear to Send              | AFS1[3]: 0                                    | AFS2[3]: 0                                          |

|        |     | COUT              | Comparator Output                 | AFS1[3]: 0                                    | AFS2[3]: 1                                          |

|        |     | T1IN              | Timer 1 Input                     | AFS1[3]: 1                                    | AFS2[3]: 0                                          |

|        |     | Analog Functions* | ADC Analog Input                  | AFS1[3]: 1                                    | AFS2[3]: 1                                          |

|        | PA4 | RXD0              | UART 0 Receive Data               | AFS1[4]: 0                                    | AFS2[4]: 0                                          |

|        |     | Reserved          |                                   | AFS1[4]: 0                                    | AFS2[4]: 1                                          |

|        |     | Reserved          |                                   | AFS1[4]: 1                                    | AFS2[4]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (N)          | AFS1[4]: 1                                    | AFS2[4]: 1                                          |

|        | PA5 | TXD0              | UART 0 Transmit Data              | AFS1[5]: 0                                    | AFS2[5]: 0                                          |

|        |     | T1OUT             | Timer 1 Output Complement         | AFS1[5]: 0                                    | AFS2[5]: 1                                          |

|        |     | Reserved          |                                   | AFS1[5]: 1                                    | AFS2[5]: 0                                          |

|        |     | Analog Functions* | ADC/Comparator Input (P)          | AFS1[5]: 1                                    | AFS2[5]: 1                                          |

|        |     |                   |                                   |                                               |                                                     |

## Table 16. Port Alternate Function Mapping (8-Pin Parts)

**Note:** \* Analog Functions include ADC inputs, ADC reference and comparator inputs. Also, alternate function selection as described in Port A–C Alternate Function Sub-Registers must be enabled.

63

## Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | RQ2ENH[x] IRQ2ENL[x] |         | Description |  |  |

|------------|----------------------|---------|-------------|--|--|

| 1          | 1                    | Level 3 | High        |  |  |

where x indicates the register bits from 0–7.

### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |

|-------|-----|------|-------|-----|-------|-------|-------|-------|--|--|

| FIELD |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |  |  |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |

| ADDR  |     | FC7H |       |     |       |       |       |       |  |  |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |

|-------|-----|------|-------|-----|-------|-------|-------|-------|--|

| FIELD |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |  |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |

| ADDR  |     | FC8H |       |     |       |       |       |       |  |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$$

#### COMPARE Mode

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

# **External Driver Enable**

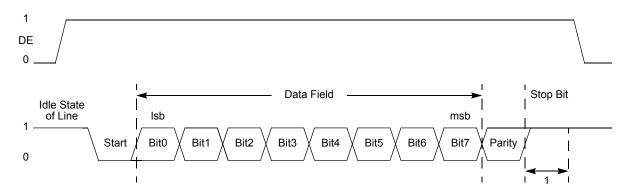

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

# **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

# **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data register (Table 63). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

# Table 63. UART Receive Data Register (U0RXD)

| BITS  | 7   | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|-----|------|---|---|---|---|---|---|--|--|

| FIELD | RXD |      |   |   |   |   |   |   |  |  |

| RESET | Х   | Х    | Х | Х | Х | Х | Х | Х |  |  |

| R/W   | R   | R    | R | R | R | R | R | R |  |  |

| ADDR  |     | F40H |   |   |   |   |   |   |  |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 64 and Table 65) identify the current UART operating configuration and status.

Table 64. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6    | 5  | 4  | 3    | 2    | 1   | 0   |  |  |

|-------|-----|------|----|----|------|------|-----|-----|--|--|

| FIELD | RDA | PE   | OE | FE | BRKD | TDRE | TXE | CTS |  |  |

| RESET | 0   | 0    | 0  | 0  | 0    | 1    | 1   | Х   |  |  |

| R/W   | R   | R    | R  | R  | R    | R    | R   | R   |  |  |

| ADDR  |     | F41H |    |    |      |      |     |     |  |  |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty

1 = There is a byte in the UART Receive Data register

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred

1 = A parity error has occurred

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is

| BITS  | 7         | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD | COMP_ADDR |     |     |     |     |     |     |     |  |

| RESET | 0         | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W       | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  | F45H      |     |     |     |     |     |     |     |  |

## Table 68. UART Address Compare Register (U0ADDR)

COMP ADDR—Compare Address

This 8-bit value is compared to incoming address bytes.

# UART Baud Rate High and Low Byte Registers

The UART Baud Rate High and Low Byte registers (Table 69 and Table 70) combine to create a 16-bit baud rate divisor value (BRG[15:0]) that sets the data transmission rate (baud rate) of the UART.

## Table 69. UART Baud Rate High Byte Register (U0BRH)

| BITS  | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD |     | BRH  |     |     |     |     |     |     |  |  |

| RESET | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | F46H |     |     |     |     |     |     |  |  |

## Table 70. UART Baud Rate Low Byte Register (U0BRL)

| BITS  | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-------|-----|------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD |     | BRL  |     |     |     |     |     |     |  |  |

| RESET | 1   | 1    | 1   | 1   | 1   | 1   | 1   | 1   |  |  |

| R/W   | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR  |     | F47H |     |     |     |     |     |     |  |  |

The UART data rate is calculated using the following equation:

UART Baud Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

For a given UART data rate, calculate the integer baud rate divisor value using the following equation:

UART Baud Rate Divisor Value (BRG) = Round  $\left(\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Data Rate (bits/s)}}\right)$

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

138

Reserved—0 when read

FSTAT—Flash Controller Status 000000 = Flash Controller locked 000001 = First unlock command received (73H written) 000010 = Second unlock command received (8CH written) 000011 = Flash Controller unlocked 000100 = Sector protect register selected 001xxx = Program operation in progress 010xxx = Page erase operation in progress 100xxx = Mass erase operation in progress

# Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|------|-----|-----|-----|-----|-----|-----|

| FIELD | INFO_EN | PAGE |     |     |     |     |     |     |

| RESET | 0       | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |         | FF9H |     |     |     |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0. A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a run function can be implemented by writing 40H to this register.

Table 99. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3    | 2     | 1 | 0   |

|-------|---------|-------|--------|---|------|-------|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | Rese | erved |   | RST |

| RESET | 0       | 0     | 0      | 0 | 0    | 0     | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R    | R     | R | R/W |

#### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = Z8 Encore! XP F0823 Series device is operating in NORMAL mode

1 = Z8 Encore! XP F0823 Series device is in DEBUG mode

#### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

- 0 = Breakpoints are disabled

- 1 = Breakpoints are enabled

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled

1 = Debug Acknowledge is enabled

#### Reserved—0 when read

#### RST—Reset

Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the OCD is not reset. This bit is automatically cleared to 0 at the end of reset.

0 = No effect

1 = Reset the Flash Read Protect Option Bit device

177

# Table 110. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SCF      | —        | Set Carry Flag         |

| SRP      | SrC      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

# Table 111. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                    |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | SrC         | Push                                                                   |

| PUSHX    | SrC         | Push using Extended Addressing                                         |

# Table 112. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| СОМ      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

# Table 119. Power Consumption

|                           |                                                    | V <sub>DI</sub>      | <sub>o</sub> = 2.7 V to 3 | 3.6 V                |       |                                                                   |

|---------------------------|----------------------------------------------------|----------------------|---------------------------|----------------------|-------|-------------------------------------------------------------------|

|                           |                                                    |                      | Maximum <sup>2</sup>      | Maximum <sup>3</sup> | -     |                                                                   |

| Symbol                    | Parameter                                          | Typical <sup>1</sup> | Std Temp                  | Ext Temp             | Units | Conditions                                                        |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                     | 0.1                  | 2                         | 7.5                  | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |

| I <sub>DD</sub> Halt      | Supply Current in HALT                             | 35                   | 55                        | 65                   | μA    | 32 kHz                                                            |

|                           | Mode (with all peripherals disabled)               | 520                  | 630                       | 700                  | μA    | 5.5 MHz                                                           |

| I <sub>DD</sub>           | Supply Current in                                  | 2.8                  | 4.5                       | 4.8                  | mA    | 32 kHz                                                            |

|                           | ACTIVE Mode (with all peripherals disabled)        | 4.5                  | 5.2                       | 5.2                  | mA    | 5.5 MHz                                                           |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                   | 0.9                  | 1.0                       | 1.1                  | μA    |                                                                   |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current | 350                  | 500                       | 550                  | μA    |                                                                   |

| I <sub>DD</sub> VBO       | Voltage Brownout<br>Supply Current                 | 50                   |                           |                      | μA    | For 20-/28-pin devices (VBO only); see Note 4                     |

|                           |                                                    |                      |                           |                      |       | For 8-pin devices; See<br>Note 4                                  |

| I <sub>DD</sub> ADC       | Analog-to-Digital                                  | 2.8                  | 3.1                       | 3.2                  | mA    | 32 kHz                                                            |

|                           | Converter Supply<br>Current (with External         | 3.1                  | 3.6                       | 3.7                  | mA    | 5.5 MHz                                                           |

|                           | Reference)                                         | 3.3                  | 3.7                       | 3.8                  | mA    | 10 MHz                                                            |

|                           |                                                    | 3.7                  | 4.2                       | 4.3                  | mA    | 20 MHz                                                            |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current           | 0                    |                           |                      | μA    | See Note 4                                                        |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                       | 150                  | 180                       | 190                  | μA    | See Note 4                                                        |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# **Ordering Information**

| Part Number                              | Flash     | RAM       | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|------------------------------------------|-----------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP with 8                     |           |           | Analog    | j-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature                     |           |           |           | 40         | 0                      | 4                   | 4              |                     |

| Z8F0823PB005SC                           | 8 KB      | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005SC                           | 8 KB      | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005SC                           | 8 KB      | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005SC                           | 8 KB      | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005SC                           | 8 KB      | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005SC                           | 8 KB      | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005SC                           | 8 KB      | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005SC                           | 8 KB      | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005SC                           | 8 KB      | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur                      | e: -40 °C | to 105 °( | C         |            |                        |                     |                |                     |

| Z8F0823PB005EC                           | 8 KB      | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0823QB005EC                           | 8 KB      | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0823SB005EC                           | 8 KB      | 1 KB      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0823SH005EC                           | 8 KB      | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0823HH005EC                           | 8 KB      | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0823PH005EC                           | 8 KB      | 1 KB      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0823SJ005EC                           | 8 KB      | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0823HJ005EC                           | 8 KB      | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0823PJ005EC                           | 8 KB      | 1 KB      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |           |           |           |            |                        |                     |                |                     |