# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 2KB (2K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 512 x 8                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0223sh005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

# 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

# **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

# **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

# Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

# Interrupt Controller

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

| Port   | Pin                 | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|---------------------|-------------|-----------------------------------------|-----------------------------------------|

| Port A | t A PA0 T0IN/T0OUT* |             | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |                     | Reserved    |                                         | -                                       |

|        | PA1                 | TOOUT       | Timer 0 Output                          | -                                       |

|        |                     | Reserved    |                                         | -                                       |

|        | PA2                 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |                     | Reserved    |                                         | -                                       |

|        | PA3                 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |                     | Reserved    |                                         | -                                       |

|        | PA4                 | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | -                                       |

|        |                     | Reserved    |                                         |                                         |

|        | PA5                 | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | -                                       |

|        |                     | Reserved    |                                         |                                         |

|        | PA6                 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |                     | Reserved    |                                         |                                         |

|        | PA7                 | T1OUT       | Timer 1 Output                          | -                                       |

|        |                     | Reserved    |                                         |                                         |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

0 = The drains are enabled for any output mode (unless overridden by the alternate function).

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A–C High Drive Enable Sub-Registers

The Port A–C High Drive Enable sub-register (Table 23) is accessed through the Port A–C Control register by writing 04H to the Port A–C Address register. Setting the bits in the Port A–C High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–C High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 23. Port A–C High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6 5 4 3                                                                               |       |       |       |       | 1     | 0     |  |  |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|

| FIELD | PHDE7    | PHDE6                                                                                 | PHDE5 | PHDE4 | PHDE3 | PHDE2 | PHDE1 | PHDE0 |  |  |

| RESET | 0        | 0                                                                                     | 0     | 0     |       |       |       |       |  |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W R/W                                                       |       |       |       |       |       |       |  |  |

| ADDR  | lf 04H i | If 04H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |  |  |

PHDE[7:0]—Port High Drive Enabled.

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

#### Port A–C Stop Mode Recovery Source Enable Sub-Registers

The Port A–C Stop Mode Recovery Source Enable sub-register (Table 24) is accessed through the Port A–C Control register by writing 05H to the Port A–C Address register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6 5 4 3                                                                               |        |        |        | 2      | 1      | 0      |  |

|-------|----------|---------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|--|

| FIELD | PSMRE7   | PSMRE6                                                                                | PSMRE5 | PSMRE4 | PSMRE3 | PSMRE2 | PSMRE1 | PSMRE0 |  |

| RESET | 0        | 0                                                                                     | 0      | 0      | 0      | 0      | 0      |        |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                                           |        |        |        |        |        |        |  |

| ADDR  | lf 05H i | If 05H in Port A–C Address Register, accessible through the Port A–C Control Register |        |        |        |        |        |        |  |

50

0 PIN0 X R

| 10.010 201 |      |      |      | (1, , , , , , , , , , , , , , , , , , , |      |      |      |

|------------|------|------|------|-----------------------------------------|------|------|------|

| BITS       | 7    | 6    | 5    | 4                                       | 3    | 2    | 1    |

| FIELD      | PIN7 | PIN6 | PIN5 | PIN4                                    | PIN3 | PIN2 | PIN1 |

| RESET      | Х    | Х    | Х    | Х                                       | Х    | Х    | Х    |

| R/W        | R    | R    | R    | R                                       | R    | R    | R    |

# Table 28. Port A–C Input Data Registers (PxIN)

PIN[7:0]—Port Input Data

Sampled data from the corresponding port pin input.

0 = Input data is logical 0 (Low)

1 = Input data is logical 1 (High)

# Port A–C Output Data Register

The Port A–C Output Data register (Table 29) controls the output data to the pins.

FD2H, FD6H, FDAH

#### Table 29. Port A–C Output Data Register (PxOUT)

| BITS  | 7                | 6 5 4 3 |       | 2     | 1     | 0     |       |       |

|-------|------------------|---------|-------|-------|-------|-------|-------|-------|

| FIELD | POUT7            | POUT6   | POUT5 | POUT4 | POUT3 | POUT2 | POUT1 | POUT0 |

| RESET | 0                | 0       | 0     | 0     | 0     | 0     | 0     | 0     |

| R/W   | R/W              | R/W     | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |

| ADDR  | FD3H, FD7H, FDBH |         |       |       |       |       |       |       |

#### POUT[7:0]—Port Output Data

These bits contain the data to be driven to the port pins. The values are only driven if the corresponding pin is configured as an output and the pin is not configured for alternate function operation.

0 =Drive a logical 0 (Low).

1 = Drive a logical 1 (High). High value is not driven if the drain has been disabled by setting the corresponding Port Output Control register bit to 1.

# LED Drive Enable Register

The LED Drive Enable register (Table 30) activates the controlled current drive. The Port C pin must first be enabled by setting the Alternate Function register to select the LED function.

ADDR

# Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP<sup>®</sup> F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

# Operation

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! XP F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 57 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

#### Table 57. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value |            | e Time-Out Delay<br>VDT oscillator frequency) |

|------------------|------------------|------------|-----------------------------------------------|

| (Hex)            | (Decimal)        | Typical    | Description                                   |

| 000004           | 4                | 400 μs     | Minimum time-out delay                        |

| FFFFF            | 16,777,215       | 28 minutes | Maximum time-out delay                        |

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte)

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte)

DEPOL—Driver Enable Polarity

0 = DE signal is Active High

1 = DE signal is Active Low

BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value. 1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRQ—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 = Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

### **UART Address Compare Register**

The UART Address Compare register stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match. baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

# Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 93.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO port alternate function for the corresponding pin.

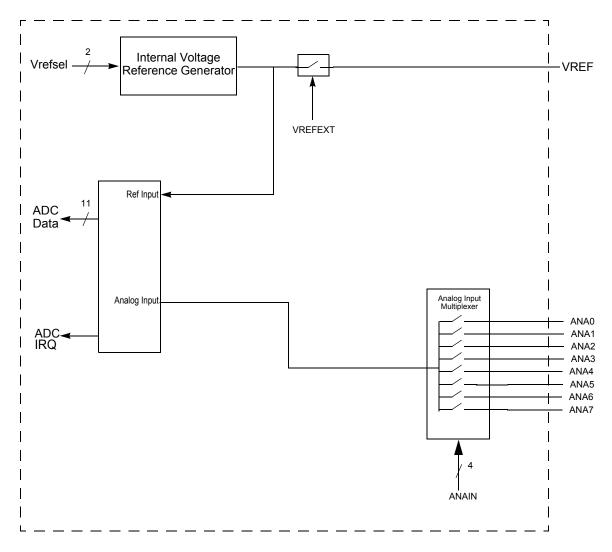

# **Analog-to-Digital Converter**

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

#### 118

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

### **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

#### **Software Compensation Procedure**

The value read from the ADC high and low byte registers are uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following formula yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) * GAINCAL)/2^{16}$

where GAINCAL is the gain calibration byte, OFFCAL is the offset calibration byte and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. The OFFCAL value is in two's complement format, as are the compensated and uncompensated ADC values.

- **Note:** The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits. Also note that in the second term, the multiplication must be performed before the division by 2<sup>16</sup>. Otherwise, the second term evaluates to zero incorrectly.

- **Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

# **ADC Control Register Definitions**

The following sections define the ADC control registers.

# **ADC Control Register 0**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6       | 5      | 4    | 3 2            |  | 2 1 |  |  |  |

|-------|-----|---------|--------|------|----------------|--|-----|--|--|--|

| FIELD | CEN | REFSELL | REFEXT | CONT | ANAIN[3:0]     |  |     |  |  |  |

| RESET | 0   | 0       | 0      | 0    | 0 0 0 0        |  |     |  |  |  |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W R/W R/W R/ |  |     |  |  |  |

| ADDR  |     | F70H    |        |      |                |  |     |  |  |  |

Table 72. ADC Control Register 0 (ADCCTL0)

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP<sup>®</sup> F0823 Series products. When this option is enabled, several of the OCD commands are disabled. Table 99 on page 162 is a summary of the OCD commands. Each OCD command is described in further detail in the bulleted list following this table. Table 99 on page 162 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|----------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                                                                                                                                                         |

| Reserved                   | 01H             | _                                     | _                                                                                                                                                                         |

| Read OCD Status Register   | 02H             | Yes                                   | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H             | _                                     | -                                                                                                                                                                         |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                                                                                                                                                 |

| Read OCD Control Register  | 05H             | Yes                                   | -                                                                                                                                                                         |

| Write Program Counter      | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter       | 07H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Register             | 08H             | _                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register              | 09H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory       | 0AH             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory        | 0BH             | _                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory          | 0CH             | _                                     | Yes.                                                                                                                                                                      |

| Read Data Memory           | 0DH             | -                                     | -                                                                                                                                                                         |

| Read Program Memory CRC    | 0EH             | -                                     | -                                                                                                                                                                         |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                         |

| Step Instruction           | 10H             | _                                     | Disabled.                                                                                                                                                                 |

186

| Assembly        |                                                                                             | Addre      | ss Mode     | Opcode(s) | Fla | igs          |   |   |   |   | – Fetch<br>Cycles | Inetr |

|-----------------|---------------------------------------------------------------------------------------------|------------|-------------|-----------|-----|--------------|---|---|---|---|-------------------|-------|

| Mnemonic        | Symbolic Operation                                                                          | dst        | src         | (Hex)     | С   | Ζ            | S | v | D | Н |                   |       |

| SUBX dst, src   | $dst \gets dst - src$                                                                       | ER         | ER          | 28        | *   | *            | * | * | 1 | * | 4                 | 3     |

|                 |                                                                                             | ER         | IM          | 29        | -   |              |   |   |   |   | 4                 | 3     |

| SWAP dst        | $dst[7:4] \leftrightarrow dst[3:0]$                                                         | R          |             | F0        | Х   | *            | * | Х | _ | _ | 2                 | 2     |

|                 |                                                                                             | IR         |             | F1        | -   |              |   |   |   |   | 2                 | 3     |

| TCM dst, src    | (NOT dst) AND src                                                                           | r          | r           | 62        | _   | *            | * | 0 | _ | _ | 2                 | 3     |

|                 |                                                                                             | r          | lr          | 63        | _   |              |   |   |   |   | 2                 | 4     |

|                 |                                                                                             | R          | R           | 64        | -   |              |   |   |   |   | 3                 | 3     |

|                 |                                                                                             | R          | IR          | 65        | _   |              |   |   |   |   | 3                 | 4     |

|                 |                                                                                             | R          | IM          | 66        |     |              |   |   |   |   | 3                 | 3     |

|                 |                                                                                             | IR         | IM          | 67        | -   |              |   |   |   |   | 3                 | 4     |

| TCMX dst, src   | (NOT dst) AND src                                                                           | ER         | ER          | 68        | _   | *            | * | 0 | _ | _ | 4                 | 3     |

|                 |                                                                                             | ER         | IM          | 69        |     |              |   |   |   |   | 4                 | 3     |

| TM dst, src     | dst AND src                                                                                 | r          | r           | 72        | _   | *            | * | 0 | - | - | 2                 | 3     |

|                 |                                                                                             | r          | lr          | 73        | _   |              |   |   |   |   | 2                 | 4     |

|                 |                                                                                             | R          | R           | 74        | _   |              |   |   |   |   | 3                 | 3     |

|                 |                                                                                             | R          | IR          | 75        | _   |              |   |   |   |   | 3                 | 4     |

|                 |                                                                                             | R          | IM          | 76        | _   |              |   |   |   |   | 3                 | 3     |

|                 |                                                                                             | IR         | IM          | 77        | _   |              |   |   |   |   | 3                 | 4     |

| TMX dst, src    | dst AND src                                                                                 | ER         | ER          | 78        | _   | *            | * | 0 | - | - | 4                 | 3     |

|                 |                                                                                             | ER         | IM          | 79        | _   |              |   |   |   |   | 4                 | 3     |

| TRAP Vector     | $SP \leftarrow SP - 2$<br>@SP ← PC<br>$SP \leftarrow SP - 1$<br>@SP ← FLAGS<br>PC ← @Vector |            | Vector      | F2        | _   | -            | - | - | _ | _ | 2                 | 6     |

| WDT             |                                                                                             |            |             | 5F        | _   | _            | - | - | - | - | 1                 | 2     |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                | f the resu | It of the o | peration. |     | = Re<br>= Se |   |   | 0 |   |                   |       |

### Table 115. eZ8 CPU Instruction Summary (Continued)

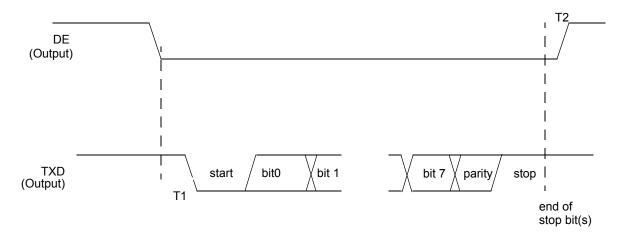

Figure 33 and Table 131 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 33. UART Timing Without CTS

| Table 131. UART | Timing Without CTS |  |

|-----------------|--------------------|--|

|                 |                    |  |

|                |                                                                        | Delay (ns)        |            |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |

| UART           |                                                                        |                   |            |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |

|                                                                   |             |       |           |            |                        | annels              | ۷              |                     |

|-------------------------------------------------------------------|-------------|-------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                                       | Flash       | RAM   | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP with 4 KB Flash, 10-Bit Analog-to-Digital Converter |             |       |           |            |                        |                     |                |                     |

| Standard Temperatur                                               | re: 0 °C to | 70 °C |           |            |                        |                     |                |                     |

| Z8F0423PB005SC                                                    | 4 KB        | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SC                                                    | 4 KB        | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SC                                                    | 4 KB        | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SC                                                    | 4 KB        | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SC                                                    | 4 KB        | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SC                                                    | 4 KB        | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SC                                                    | 4 KB        | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SC                                                    | 4 KB        | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SC                                                    | 4 KB        | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                            |             |       |           |            |                        |                     |                |                     |

| Z8F0423PB005EC                                                    | 4 KB        | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EC                                                    | 4 KB        | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EC                                                    | 4 KB        | 1 KB  | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EC                                                    | 4 KB        | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EC                                                    | 4 KB        | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EC                                                    | 4 KB        | 1 KB  | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EC                                                    | 4 KB        | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EC                                                    | 4 KB        | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EC                                                    | 4 KB        | 1 KB  | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                          |             |       |           |            |                        |                     |                |                     |

| mber                                                              |            |       | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |

|-------------------------------------------------------------------|------------|-------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                                                       | Flash      | RAM   | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |

| Z8 Encore! XP with 2 KB Flash, 10-Bit Analog-to-Digital Converter |            |       |           |            |                        |                     |                |                     |

| Standard Temperature                                              | e: 0 °C to | 70 °C |           |            |                        |                     |                |                     |

| Z8F0223PB005SC                                                    | 2 KB       | 512 B | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SC                                                    | 2 KB       | 512 B | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SC                                                    | 2 KB       | 512 B | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SC                                                    | 2 KB       | 512 B | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SC                                                    | 2 KB       | 512 B | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SC                                                    | 2 KB       | 512 B | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SC                                                    | 2 KB       | 512 B | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SC                                                    | 2 KB       | 512 B | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SC                                                    | 2 KB       | 512 B | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C                            |            |       |           |            |                        |                     |                |                     |

| Z8F0223PB005EC                                                    | 2 KB       | 512 B | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EC                                                    | 2 KB       | 512 B | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EC                                                    | 2 KB       | 512 B | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EC                                                    | 2 KB       | 512 B | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EC                                                    | 2 KB       | 512 B | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EC                                                    | 2 KB       | 512 B | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EC                                                    | 2 KB       | 512 B | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EC                                                    | 2 KB       | 512 B | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EC                                                    | 2 KB       | 512 B | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging                          |            |       |           |            |                        |                     |                |                     |

page erase 135 page select register 138, 139 FPS register 138, 139 FSTAT register 137

# G

GATED mode 84 general-purpose I/O 35 GPIO 4.35 alternate functions 36 architecture 36 control register definitions 43 input data sample timing 202 interrupts 43 port A-C pull-up enable sub-registers 48, 49 port A-H address registers 44 port A-H alternate function sub-registers 45 port A-H control registers 44 port A-H data direction sub-registers 45 port A-H high drive enable sub-registers 47 port A-H input data registers 49 port A-H output control sub-registers 46 port A-H output data registers 50 port A-H stop mode recovery sub-registers 47 port availability by device 35 port input timing 203 port output timing 204

# Η

H 174 HALT 176 halt mode 32, 176 hexadecimal number prefix/suffix 174

#

I2C 4 IM 173 immediate data 173 immediate operand prefix 174 **INC 175** increment 175 increment word 175 **INCW 175** indexed 173 indirect address prefix 174 indirect register 173 indirect register pair 173 indirect working register 173 indirect working register pair 173 infrared encoder/decoder (IrDA) 113 Instruction Set 171 instruction set. eZ8 CPU 171 instructions ADC 175 **ADCX 175** ADD 175 **ADDX 175** AND 177 **ANDX 177** arithmetic 175 **BCLR 176 BIT 176** bit manipulation 176 block transfer 176 **BRK 178 BSET 176** BSWAP 176, 178 **BTJ 178 BTJNZ 178 BTJZ 178 CALL 178** CCF 176 CLR 177 COM 177 CP 175 **CPC 175 CPCX 175** CPU control 176 **CPX 175** DA 175 **DEC 175 DECW 175**

DI 176