Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Discontinued at Digi-Key                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.173", 4.40mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413hj005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Table 19. Port A–C Control Registers (PxCTL)

| BITS  | 7   | 6                           | 5 | 4        | 3        | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|----------|----------|---|---|---|--|

| FIELD |     | PCTL                        |   |          |          |   |   |   |  |

| RESET |     | 00H                         |   |          |          |   |   |   |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |          |          |   |   |   |  |

| ADDR  |     |                             |   | FD1H, FD | 5H, FD9H |   |   |   |  |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

# Port A-C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address register (Table 20).

| BITS  | 7        | 6          | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|----------|------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | DD7      | DD6        | DD5         | DD4           | DD3          | DD2           | DD1          | DD0      |

| RESET | 1        | 1          | 1           | 1             | 1            | 1             | 1            | 1        |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W          | R/W           | R/W          | R/W      |

| ADDR  | lf 01H i | n Port A–C | Address Reg | gister, acces | sible throug | n the Port A- | -C Control F | Register |

## Table 20. Port A–C Data Direction Sub-Registers (PxDD)

DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–C Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tristated.

# Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 21) is accessed through the Port A–C Control register by writing 02H to the Port A–C Address register. The Port A–C Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–C Alternate Function Set 1 Sub-Registers on page 48 and Port A–C Alternate Function Set 2 Sub-Registers on

## Table 32. LED Drive Level Low Register (LEDLVLL)

| BITS  | 7   | 6            | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----|--------------|-----|-----|-----|-----|-----|-----|--|

| FIELD |     | LEDLVLL[7:0] |     |     |     |     |     |     |  |

| RESET | 0   | 0            | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W | R/W          | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |     |              |     | F8  | 4H  |     |     |     |  |

LEDLVLH[7:0]—LED Level High Bit

{LEDLVLH, LEDLVLL} select one of four programmable current drive levels for each Port C pin.

00 = 3 mA01 = 7 mA10 = 13 mA

10 = 13 mA11 = 20 mA generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$$

#### COMPARE Mode

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the

- 0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

- 10 = Timer Interrupt only on defined Input Capture/Deassertion Events

- 11 = Timer Interrupt only on defined Reload/Compare Events

Reserved-Must be 0

#### PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

000 = No delay 001 = 2 cycles delay 010 = 4 cycles delay 011 = 8 cycles delay 100 = 16 cycles delay 101 = 32 cycles delay 110 = 64 cycles delay111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| BITS  | 7   | 6    | 5          | 4     | 3    | 2   | 1   | 0   |

|-------|-----|------|------------|-------|------|-----|-----|-----|

| FIELD | TEN | TPOL | PRES TMODE |       |      |     |     |     |

| RESET | 0   | 0    | 0          | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W  | R/W        | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |      |            | F07H, | F0FH |     |     |     |

Table 56. Timer 0–1 Control Register 1 (TxCTL1)

TEN—Timer Enable

0 = Timer is disabled

1 = Timer enabled to count

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7 | 6             | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|---------------|---|----|----|---|---|---|--|

| FIELD |   | TXD           |   |    |    |   |   |   |  |

| RESET | Х | Х             | Х | Х  | Х  | Х | Х | Х |  |

| R/W   | W | W W W W W W W |   |    |    |   |   |   |  |

| ADDR  |   |               |   | F4 | 0H |   |   |   |  |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

bits of resolution are lost because of a rounding error. As a result, the final value is an 11- bit number.

## Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F0823 Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Factory trimming information for the internal precision oscillator

- Factory calibration values for ADC

- Factory serialization and randomized lot identifier (optional)

# Operation

## **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0823 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Types**

## **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device

142

configurations. The information contained here is lost when page 0 of the Program Memory is erased.

## **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

## **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in Flash Information Area on page 15

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (for more details, see Reading the Flash Information Page on page 143 and Serialization Data on page 148) and are unaffected by mass erasure of the device's Flash memory.

## **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

Note:

## Table 95. Serialization Data Locations

| Info Page<br>Address | Memory Address | Usage                                    |

|----------------------|----------------|------------------------------------------|

| 1C                   | FE1C           | Serial Number Byte 3 (most significant)  |

| 1D                   | FE1D           | Serial Number Byte 2                     |

| 1E                   | FE1E           | Serial Number Byte 1                     |

| 1F                   | FE1F           | Serial Number Byte 0 (least significant) |

## **Randomized Lot Identifier**

## Table 96. Lot Identification Number (RAND\_LOT)

| BITS      | 7                                               | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|----------|-----|-----|-----|-----|-----|-----|--|--|

| FIELD     |                                                 | RAND_LOT |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U        | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Interspersed throughout Information Page Memory |          |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |          |     |     |     |     |     |     |  |  |

RAND LOT-Randomized Lot ID

The randomized lot ID is a 32 byte binary value that changes for each production lot.

## Table 97. Randomized Lot ID Locations

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

| 150 |

|-----|

|-----|

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

Table 97. Randomized Lot ID Locations (Continued)

## OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 157).

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

## **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

A reset and stop function can be achieved by writing 81H to this register. A reset and go function can be achieved by writing 41H to this register. If the device is in DEBUG mode, a run function can be implemented by writing 40H to this register.

Table 99. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4 | 3    | 2     | 1 | 0   |

|-------|---------|-------|--------|---|------|-------|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK |   | Rese | erved |   | RST |

| RESET | 0       | 0     | 0      | 0 | 0    | 0     | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R | R    | R     | R | R/W |

#### DBGMODE—DEBUG Mode

The device enters DEBUG mode when this bit is 1. When in DEBUG mode, the eZ8 CPU stops fetching new instructions. Clearing this bit causes the eZ8 CPU to restart. This bit is automatically set when a BRK instruction is decoded and breakpoints are enabled. If the Flash Read Protect Option Bit is enabled, this bit can only be cleared by resetting the device. It cannot be written to 0.

0 = Z8 Encore! XP F0823 Series device is operating in NORMAL mode

1 = Z8 Encore! XP F0823 Series device is in DEBUG mode

#### BRKEN—Breakpoint Enable

This bit controls the behavior of the BRK instruction (opcode 00H). By default, breakpoints are disabled and the BRK instruction behaves similar to an NOP instruction. If this bit is 1, when a BRK instruction is decoded, the DBGMODE bit of the OCDCTL register is automatically set to 1.

- 0 = Breakpoints are disabled

- 1 = Breakpoints are enabled

#### DBGACK—Debug Acknowledge

This bit enables the debug acknowledge feature. If this bit is set to 1, the OCD sends a Debug Acknowledge character (FFH) to the host when a Breakpoint occurs.

0 = Debug Acknowledge is disabled

1 = Debug Acknowledge is enabled

#### Reserved—0 when read

#### RST—Reset

Setting this bit to 1 resets the Z8F04xA family device. The device goes through a normal Power-On Reset sequence with the exception that the OCD is not reset. This bit is automatically cleared to 0 at the end of reset.

0 = No effect

1 = Reset the Flash Read Protect Option Bit device

• Rotate and Shift

Tables 107 through Table 114 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

|          | •        |                                               |

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| CP       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| СРХ      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

|          |          |                                               |

## **Table 107. Arithmetic Instructions**

| Table 1 | 08. Bit | Manir | oulation | Instructions |  |

|---------|---------|-------|----------|--------------|--|

|         | 00. Dit | mann  | Julution | monuciono    |  |

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 109. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                         |

|----------|----------|---------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment Addresses |

## Table 110. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | HALT Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

182

| Assembly        |                                                                                                                       | Addre       | ss Mode    | - Opcode(s) | Flags |   |               |   |   |   | - Fetch | Instr  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-------|---|---------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                                                                    | dst         | src        | (Hex)       | С     | z | S             | v | D | Н |         | Cycles |

| HALT            | HALT Mode                                                                                                             |             |            | 7F          | -     | _ | -             | _ | - | - | 1       | 2      |

| INC dst         | $dst \leftarrow dst + 1$                                                                                              | R           |            | 20          | -     | * | *             | _ | - | - | 2       | 2      |

|                 |                                                                                                                       | IR          |            | 21          | -     |   |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | r           |            | 0E-FE       | -     |   |               |   |   |   | 1       | 2      |

| INCW dst        | $dst \leftarrow dst + 1$                                                                                              | RR          |            | A0          | -     | * | *             | * | - | - | 2       | 5      |

|                 |                                                                                                                       | IRR         |            | A1          | -     |   |               |   |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP \\ SP \leftarrow SP + 1 \\ PC \leftarrow @SP \\ SP \leftarrow SP + 2 \\ IRQCTL[7] \leftarrow 1$ |             |            | BF          | *     | * | *             | * | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                        | DA          |            | 8D          | _     | _ | _             | _ | _ | _ | 3       | 2      |

|                 |                                                                                                                       | IRR         |            | C4          | -     |   |               |   |   |   | 2       | 3      |

| JP cc, dst      | if cc is true<br>PC $\leftarrow$ dst                                                                                  | DA          |            | 0D-FD       | -     | _ | -             | _ | _ | - | 3       | 2      |

| JR dst          | $PC \gets PC + X$                                                                                                     | DA          |            | 8B          | -     | _ | _             | _ | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                               | DA          |            | 0B-FB       | -     | _ | _             | _ | _ | - | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                       | r           | IM         | 0C-FC       | -     | _ | -             | _ | - | - | 2       | 2      |

|                 |                                                                                                                       | r           | X(r)       | C7          | -     |   |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | X(r)        | r          | D7          |       |   |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | r           | lr         | E3          | _     |   |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | R           | R          | E4          | _     |   |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | R           | IR         | E5          | _     |   |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | R           | IM         | E6          |       |   |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | IR          | IM         | E7          | _     |   |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | lr          | r          | F3          | _     |   |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | IR          | R          | F5          |       |   |               |   |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                          | f the resul | t of the o | peration.   |       |   | eset<br>et to |   | 0 |   |         |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly<br>Mnemonic |                                                                  | Addre   | ss Mode     | - Opcode(s) | Fla | gs |              |   | - Fetch | Instr. |          |   |

|----------------------|------------------------------------------------------------------|---------|-------------|-------------|-----|----|--------------|---|---------|--------|----------|---|

|                      | Symbolic Operation                                               | dst     | src         |             | С   | Ζ  | S            | v | D       | Н      | Cycles C |   |

| RR dst               |                                                                  | R       |             | E0          | *   | *  | *            | * | _       | -      | 2        | 2 |

|                      | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                    | IR      |             | E1          | _   |    |              |   |         |        | 2        | 3 |

| RRC dst              |                                                                  | R       |             | C0          | *   | *  | *            | * | _       | -      | 2        | 2 |

|                      | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR      |             | C1          | _   |    |              |   |         |        | 2        | 3 |

| SBC dst, src         | $dst \gets dst - src - C$                                        | r       | r           | 32          | *   | *  | *            | * | 1       | *      | 2        | 3 |

|                      |                                                                  | r       | lr          | 33          | _   |    |              |   |         |        | 2        | 4 |

|                      |                                                                  | R       | R           | 34          | _   |    |              |   |         |        | 3        | 3 |

|                      |                                                                  | R       | IR          | 35          | _   |    |              |   |         |        | 3        | 4 |

|                      |                                                                  | R       | IM          | 36          | _   |    |              |   |         |        | 3        | 3 |

|                      |                                                                  | IR      | IM          | 37          | _   |    |              |   |         |        | 3        | 4 |

| SBCX dst, src        | $dst \gets dst - src - C$                                        | ER      | ER          | 38          | *   | *  | *            | * | 1       | *      | 4        | 3 |

|                      |                                                                  | ER      | IM          | 39          | _   |    |              |   |         |        | 4        | 3 |

| SCF                  | C ← 1                                                            |         |             | DF          | 1   | -  | _            | _ | _       | -      | 1        | 2 |

| SRA dst              | <b>*</b> *                                                       | R       |             | D0          | *   | *  | *            | 0 | _       | -      | 2        | 2 |

|                      | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR      |             | D1          |     |    |              |   |         |        | 2        | 3 |

| SRL dst              | 0 - D7 D6 D5 D4 D3 D2 D1 D0 - C                                  | R       |             | 1F C0       | *   | *  | 0            | * | _       | -      | 3        | 2 |

|                      | dst                                                              | IR      |             | 1F C1       |     |    |              |   |         |        | 3        | 3 |

| SRP src              | $RP \leftarrow src$                                              |         | IM          | 01          | -   | _  | _            | _ | _       | -      | 2        | 2 |

| STOP                 | STOP Mode                                                        |         |             | 6F          | _   | _  | _            | _ | _       | _      | 1        | 2 |

| SUB dst, src         | $dst \gets dst - src$                                            | r       | r           | 22          | *   | *  | *            | * | 1       | *      | 2        | 3 |

|                      |                                                                  | r       | lr          | 23          | -   |    |              |   |         |        | 2        | 4 |

|                      |                                                                  | R       | R           | 24          | -   |    |              |   |         |        | 3        | 3 |

|                      |                                                                  | R       | IR          | 25          | _   |    |              |   |         |        | 3        | 4 |

|                      |                                                                  | R       | IM          | 26          | -   |    |              |   |         |        | 3        | 3 |

|                      |                                                                  | IR      | IM          | 27          | -   |    |              |   |         |        | 3        | 4 |

| Flags Notation:      | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu | It of the o | peration.   |     |    | ese<br>et to |   | 0       |        |          |   |

## Table 115. eZ8 CPU Instruction Summary (Continued)

## Table 117. Absolute Maximum Ratings (Continued)

| Parameter                                                      | Minimum Maximum | Units | Notes |

|----------------------------------------------------------------|-----------------|-------|-------|

| Maximum current into $V_{\text{DD}}$ or out of $V_{\text{SS}}$ | 125             | mA    |       |

|                                                                |                 |       |       |

Operating temperature is specified in DC Characteristics.

- This voltage applies to all pins except the following: V<sub>DD</sub>, AV<sub>DD</sub>, pins supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1). On the 8-pin packages, this applies to all pins but V<sub>DD</sub>.

- This voltage applies to pins on the 20/28 pin packages supporting analog input (Port B[5:0], Port C[2:0]) and pins supporting the crystal oscillator (PA0 and PA1).

# **DC Characteristics**

Table 118 lists the DC characteristics of the Z8 Encore!  $XP^{\ensuremath{\mathbb{R}}}$  F0823 Series products. All voltages are referenced to V<sub>SS</sub>, the primary system ground.

## Table 118. DC Characteristics

|                  |                              |                     | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                                                                                              |

|------------------|------------------------------|---------------------|------------------------|----------------------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Symbol           | Parameter                    | Minimum             | Typical                | Maximum              | Units | Conditions                                                                                                                                                   |

| V <sub>DD</sub>  | Supply Voltage               | 2.7                 | _                      | 3.6                  | V     |                                                                                                                                                              |

| V <sub>IL1</sub> | Low Level Input<br>Voltage   | -0.3                | -                      | 0.3*V <sub>DD</sub>  | V     |                                                                                                                                                              |

| V <sub>IH1</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | 5.5                  | V     | For all input pins without analog<br>or oscillator function. For all<br>signal pins on the 8-pin devices.<br>Programmable pull-ups must<br>also be disabled. |

| V <sub>IH2</sub> | High Level Input<br>Voltage  | 0.7*V <sub>DD</sub> | -                      | V <sub>DD</sub> +0.3 | V     | For those pins with analog or<br>oscillator function (20-/28-pin<br>devices only), or when<br>programmable pull-ups are<br>enabled.                          |

| V <sub>OL1</sub> | Low Level Output<br>Voltage  | -                   | _                      | 0.4                  | V     | I <sub>OL</sub> = 2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                               |

| V <sub>OH1</sub> | High Level Output<br>Voltage | 2.4                 | _                      | -                    | V     | I <sub>OH</sub> = -2 mA; V <sub>DD</sub> = 3.0 V<br>High Output Drive disabled.                                                                              |

| V <sub>OL2</sub> | Low Level Output<br>Voltage  | -                   | -                      | 0.6                  | V     | I <sub>OL</sub> = 20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled.                                                                               |

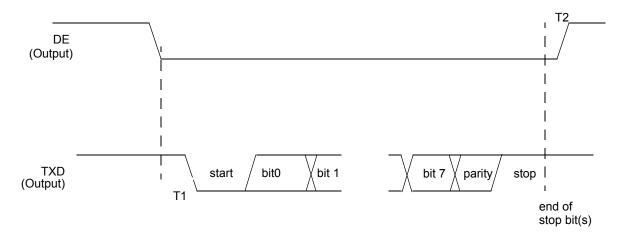

Figure 33 and Table 131 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 33. UART Timing Without CTS

| Table 131. UART | Timing Without CTS |  |

|-----------------|--------------------|--|

|                 |                    |  |

|                |                                                                        | Delay (ns)        |            |  |  |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|--|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |  |  |

| UART           |                                                                        |                   |            |  |  |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |  |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |  |  |

### 209

# Packaging

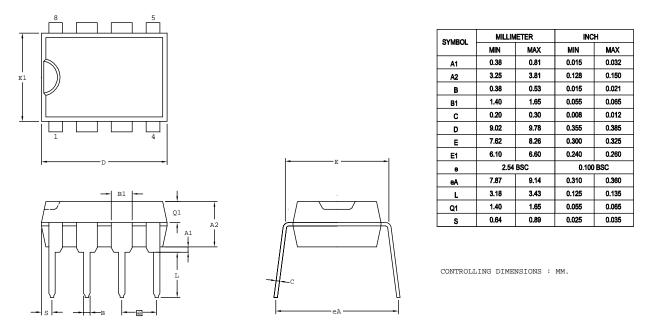

Figure 34 displays the 8-pin Plastic Dual Inline Package (PDIP) available for the Z8 Encore!  $XP^{\textcircled{R}}$  F0823 Series devices.

Figure 34. 8-Pin Plastic Dual Inline Package (PDIP)

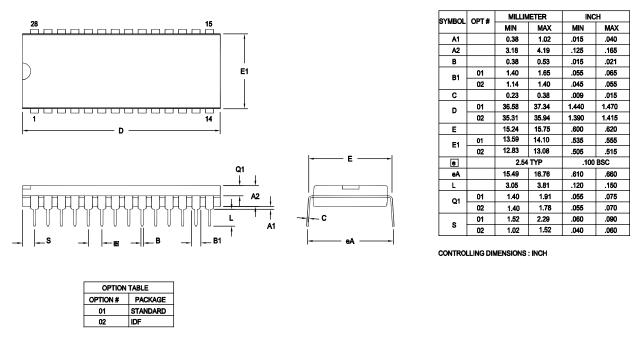

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

## Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)