Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413pb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **CPU and Peripheral Overview**

# eZ8 CPU Features

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{\text{(R)}}$  instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory.

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks.

- Compatible with existing Z8 code.

- Expanded internal Register File allows access of up to 4 KB.

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C.

- Pipelined instruction fetch and execution.

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL.

- New instructions support 12-bit linear addressing of the Register file.

- Up to 10 MIPS operation.

- C-Compiler friendly.

- 2 to 9 clock cycles per instruction.

For more information on eZ8 CPU, refer to eZ8 CPU Core User Manual (UM0128) available for download at <u>www.zilog.com</u>.

# General-Purpose I/O

Z8 Encore! XP F0823 Series features 6 to 24 port pins (Ports A–C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

# Flash Controller

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active Low<br>or Active<br>High | Tristate<br>Output | Internal Pull-up<br>or Pull-down                        | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                    | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------|--------------------|---------------------------------------------------------|------------------------------|---------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if key<br>sequence<br>detected) | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| RESET/<br>PA2      | I/O       | I/O<br>(defaults<br>to RESET)                                           | N/A                             | Yes                | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes                          | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

| VSS                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

# Table 5. Pin Characteristics (8-Pin Devices)

| Address (Hex)   | Register Description      | Mnemonic | Reset (Hex) | Page No |

|-----------------|---------------------------|----------|-------------|---------|

| F0C             | Timer 1 PWM High Byte     | T1PWMH   | 00          | 81      |

| F0D             | Timer 1 PWM Low Byte      | T1PWML   | 00          | 82      |

| F0E             | Timer 1 Control 0         | T1CTL0   | 00          | 82      |

| F0F             | Timer 1 Control 1         | T1CTL1   | 00          | 80      |

| F10–F3F         | Reserved                  | —        | XX          |         |

| UART            |                           |          |             |         |

| F40             | UART0 Transmit Data       | U0TXD    | XX          | 104     |

|                 | UART0 Receive Data        | U0RXD    | XX          | 105     |

| F41             | UART0 Status 0            | U0STAT0  | 0000011Xb   | 105     |

| F42             | UART0 Control 0           | U0CTL0   | 00          | 107     |

| F43             | UART0 Control 1           | U0CTL1   | 00          | 107     |

| F44             | UART0 Status 1            | U0STAT1  | 00          | 106     |

| F45             | UART0 Address Compare     | U0ADDR   | 00          | 109     |

| F46             | UART0 Baud Rate High Byte | U0BRH    | FF          | 110     |

| F47             | UART0 Baud Rate Low Byte  | U0BRL    | FF          | 110     |

| F48–F6F         | Reserved                  | _        | XX          |         |

| Analog-to-Digit | al Converter (ADC)        |          |             |         |

| F70             | ADC Control 0             | ADCCTL0  | 00          | 122     |

| F71             | ADC Control 1             | ADCCTL1  | 80          | 122     |

| F72             | ADC Data High Byte        | ADCD_H   | XX          | 124     |

| F73             | ADC Data Low Bits         | ADCD_L   | XX          | 124     |

| F74–F7F         | Reserved                  | _        | XX          |         |

| Low Power Cor   | ntrol                     |          |             |         |

| F80             | Power Control 0           | PWRCTL0  | 80          | 33      |

| F81             | Reserved                  |          | XX          |         |

| LED Controller  |                           |          |             |         |

| F82             | LED Drive Enable          | LEDEN    | 00          | 51      |

| F83             | LED Drive Level High Byte | LEDLVLH  | 00          | 51      |

| F84             | LED Drive Level Low Byte  | LEDLVLL  | 00          | 52      |

| F85             | Reserved                  | _        | XX          |         |

| Oscillator Cont | rol                       |          |             |         |

| F86             | Oscillator Control        | OSCCTL   | A0          | 167     |

| F87–F8F         | Reserved                  | _        | XX          |         |

| Comparator 0    |                           |          |             |         |

| F90             | Comparator 0 Control      | CMP0     | 14          | 128     |

|                 |                           |          |             |         |

| Port   | Pin             | Mnemonic                                                   | Alternate Function Description                         | Alternate Function<br>Set Register AFS1 |

|--------|-----------------|------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|

| Port C | PC0             | Reserved                                                   |                                                        | AFS1[0]: 0                              |

|        |                 | ANA4/CINP/LED<br>Drive                                     | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1                              |

|        | PC1             | Reserved                                                   |                                                        | AFS1[1]: 0                              |

|        |                 | ANA5/CINN/ LED ADC or Comparator Input, or LED drive Drive |                                                        | AFS1[1]: 1                              |

|        | PC2             | Reserved                                                   | AFS1[2]: 0                                             |                                         |

|        | ANA6/L<br>VREF* | ANA6/LED/<br>VREF*                                         | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1                              |

|        | PC3             | COUT                                                       | Comparator Output                                      | AFS1[3]: 0                              |

|        |                 | LED                                                        | LED drive                                              | AFS1[3]: 1                              |

|        | PC4             | Reserved                                                   |                                                        | AFS1[4]: 0                              |

|        |                 | LED                                                        | LED Drive                                              | AFS1[4]: 1                              |

|        | PC5             | Reserved                                                   |                                                        | AFS1[5]: 0                              |

|        |                 | LED                                                        | LED Drive                                              | AFS1[5]: 1                              |

|        | PC6             | Reserved                                                   |                                                        | AFS1[6]: 0                              |

|        |                 | LED LED Drive                                              |                                                        | AFS1[6]: 1                              |

|        | PC7             | Reserved                                                   |                                                        | AFS1[7]: 0                              |

|        |                 | LED                                                        | LED Drive                                              | AFS1[7]: 1                              |

### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

**Note:** Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in Port A–C Alternate Function Sub-Registers must also be enabled. \*VREF is available on PC2 in 20-pin parts only.

# Port A–C Address Registers

The Port A–C Address registers select the GPIO Port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO Port controls (Table 18).

# Table 18. Port A–C GPIO Address Registers (PxADDR)

| BITS  | 7   | 6                           | 5 | 4        | 3        | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|----------|----------|---|---|---|--|

| FIELD |     | PADDR[7:0]                  |   |          |          |   |   |   |  |

| RESET |     | 00H                         |   |          |          |   |   |   |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |          |          |   |   |   |  |

| ADDR  |     |                             |   | FD0H, FD | 4H, FD8H |   |   |   |  |

PADDR[7:0]—Port Address

The Port Address selects one of the sub-registers accessible through the Port Control register.

| PADDR[7:0] | Port Control Sub-register Accessible Using the Port A–C Control Registers      |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H–FFH    | No function.                                                                   |

# Port A–C Control Registers

The Port A–C Control registers set the GPIO port operation. The value in the corresponding Port A–C Address register determines which sub-register is read from or written to by a Port A–C Control register transaction (Table 19).

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

| BITS  | 7   | 6    | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|------|-----|-------|------|-----|-----|-----|

| FIELD |     | PWML |     |       |      |     |     |     |

| RESET | 0   | 0    | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W  | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |      |     | F05H, | F0DH |     |     |     |

#### Table 54. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

# **Timer 0–1 Control Registers**

## Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input Capture event.

Table 55. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6    | 5    | 4        | 3    | 2   | 1   | 0      |

|-------|---------|------|------|----------|------|-----|-----|--------|

| FIELD | TMODEHI | TICO | NFIG | Reserved | PWMD |     |     | INPCAP |

| RESET | 0       | 0    | 0    | 0        | 0    | 0   | 0   | 0      |

| R/W   | R/W     | R/W  | R/W  | R/W      | R/W  | R/W | R/W | R/W    |

| ADDR  |         |      |      | F06H,    | F0EH |     |     |        |

#### TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value. See the TxCTL1 register description for more details.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

#### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1001 = Divide by 2

# Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

# Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Flash Option Bit, see Flash Option Bits on page 141.

## WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see Reset Status Register on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

## WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and Z8 Encore! XP F0823 Series are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

# Table 59. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS     | 7              | 6            | 5             | 4              | 3             | 2            | 1    | 0    |  |

|----------|----------------|--------------|---------------|----------------|---------------|--------------|------|------|--|

| FIELD    |                | WDTU         |               |                |               |              |      |      |  |

| RESET    |                |              |               | 00             | )H            |              |      |      |  |

| R/W      | R/W*           | R/W*         | R/W*          | R/W*           | R/W*          | R/W*         | R/W* | R/W* |  |

| ADDR     |                |              |               | FF             | 1H            |              |      |      |  |

| R/W*—Rea | ad returns the | e current WD | T count value | . Write sets t | ne appropriat | e Reload Val | ue.  |      |  |

WDTU—WDT Reload Upper Byte Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

# Table 60. Watchdog Timer Reload High Byte Register (WDTH)

| BITS     | 7                                                                                       | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|----------|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| FIELD    |                                                                                         | WDTH |      |      |      |      |      |      |  |  |

| RESET    |                                                                                         | 04H  |      |      |      |      |      |      |  |  |

| R/W      | R/W*                                                                                    | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| ADDR     | FF2H                                                                                    |      |      |      |      |      |      |      |  |  |

| R/W*—Rea | R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

## Table 61. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS     | 7                                                                                       | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|----------|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|

| FIELD    |                                                                                         | WDTL |      |      |      |      |      |      |  |  |

| RESET    |                                                                                         | 00H  |      |      |      |      |      |      |  |  |

| R/W      | R/W*                                                                                    | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |

| ADDR     | FF3H                                                                                    |      |      |      |      |      |      |      |  |  |

| R/W*—Rea | R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

## **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

## **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte cannot contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

## **UART Data and Error Handling Procedure**

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

108

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |

|-------|---------|------|---------|------|-------|--------|--------|------|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |

| ADDR  | F43H    |      |         |      |       |        |        |      |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

# Comparator

Z8 Encore! XP<sup>®</sup> F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The features of Comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see Power Control Register 0 on page 32.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts after comparator enabling. The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definitions**

## **Comparator Control Register**

The Comparator Control register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

132

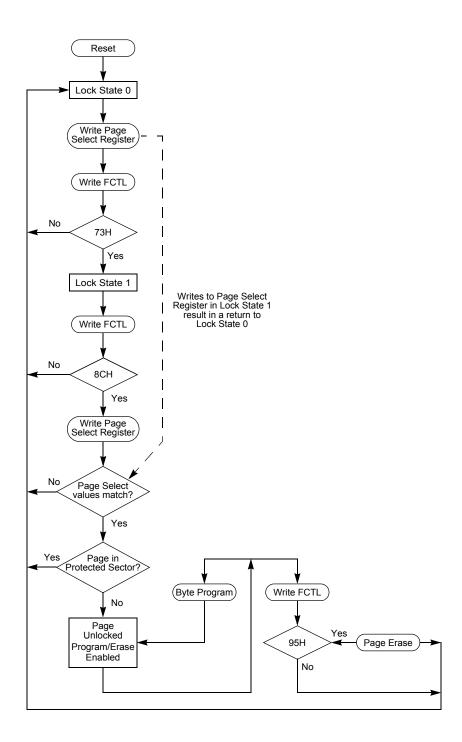

Figure 21. Flash Controller Operation Flowchart

| Table 78. Flash Code Pr | rotection Using  | the Flash O | ntion Bits |

|-------------------------|------------------|-------------|------------|

|                         | olection bailing | the mash o  |            |

| FWP | Flash Code Protection Description                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code programming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                           |

#### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

#### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total size of the Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal.

The Sector Protect Register controls the protection state of each Flash sector. This register is shared with the Page Select Register. It is accessed by writing 73H followed by 5EH to the Flash controller. The next write to the Flash Control Register targets the Sector Protect Register.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After

Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

# Flash Program Memory Address 0001H

#### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS                                          | 7                    | 6   | 5   | 4      | 3        | 2   | 1   | 0   |

|-----------------------------------------------|----------------------|-----|-----|--------|----------|-----|-----|-----|

| FIELD                                         | Reserved             |     |     | XTLDIS | Reserved |     |     |     |

| RESET                                         | U                    | U   | U   | U      | U U U U  |     |     |     |

| R/W                                           | R/W                  | R/W | R/W | R/W    | R/W      | R/W | R/W | R/W |

| ADDR                                          | Program Memory 0001H |     |     |        |          |     |     |     |

| Note: U = Unchanged by Reset R/W = Read/Write |                      |     |     |        |          |     |     |     |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. The features of IPO include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

Power down this block for minimum system power. By default, the oscillator is configured through the Flash Option bits. However, the user code can override these trim values as described in Trim Bit Address Space on page 146.

Select one of the two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 165.

#### 197

## Table 119. Power Consumption (Continued)

|                    |                             | V <sub>DE</sub>      | <sub>0</sub> = 2.7 V to 3 | 3.6 V                |       |                        |  |

|--------------------|-----------------------------|----------------------|---------------------------|----------------------|-------|------------------------|--|

|                    |                             |                      | Maximum <sup>2</sup>      | Maximum <sup>3</sup> |       |                        |  |

| Symbol             | Parameter                   | Typical <sup>1</sup> | Std Temp                  | Ext Temp             | Units | Conditions             |  |

| I <sub>DD</sub> BG | Band Gap Supply             | 320                  | 480                       | 500                  | μA    | For 20-/28-pin devices |  |

|                    | Current                     |                      |                           |                      |       | For 8-pin devices      |  |

| Notes              | conditions are defined as \ | /pp = 3.3 V and      | 1 +30 °C                  |                      |       |                        |  |

Typical conditions are defined as V<sub>DD</sub> = 3.3 V and +30 °C.

Standard temperature is defined as T<sub>A</sub> = 0 °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                                                                                                                                                                |                        | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise<br>stated) |                   |       |                                           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|--------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------------------------------|--|

| Symbol                                                                                                                                                         | Parameter              | Minimum                                                                                                | Maximum           | Units | Conditions                                |  |

| F <sub>SYSCLK</sub>                                                                                                                                            | System Clock Frequency | _                                                                                                      | 20.0 <sup>1</sup> | MHz   | Read-only from Flash memory               |  |

|                                                                                                                                                                |                        |                                                                                                        | 20.0 <sup>1</sup> | MHz   | Program or erasure of the<br>Flash memory |  |

| T <sub>XIN</sub>                                                                                                                                               | System Clock Period    | 50                                                                                                     | _                 | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>  |  |

| T <sub>XINH</sub>                                                                                                                                              | System Clock High Time | 20                                                                                                     | 30                | ns    | T <sub>CLK</sub> = 50 ns                  |  |

| T <sub>XINL</sub>                                                                                                                                              | System Clock Low Time  | 20                                                                                                     | 30                | ns    | T <sub>CLK</sub> = 50 ns                  |  |

| T <sub>XINR</sub>                                                                                                                                              | System Clock Rise Time | -                                                                                                      | 3                 | ns    | T <sub>CLK</sub> = 50 ns                  |  |

| T <sub>XINF</sub>                                                                                                                                              | System Clock Fall Time | -                                                                                                      | 3                 | ns    | T <sub>CLK</sub> = 50 ns                  |  |

| <sup>1</sup> System Clock Frequency is limited by the Internal Precision Oscillator on the Z8 Encore! XP <sup>®</sup> F0823 Series. See Table 121 on page 198. |                        |                                                                                                        |                   |       |                                           |  |

#### Table 120. AC Characteristics

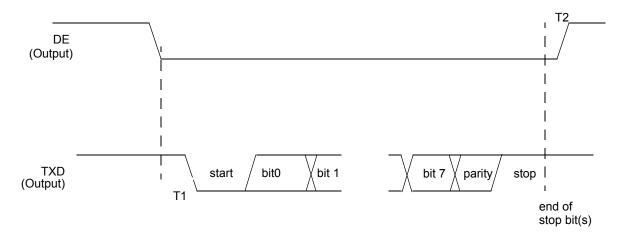

Figure 33 and Table 131 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 33. UART Timing Without CTS

| Table 131. UART | Timing Without CTS |  |

|-----------------|--------------------|--|

|                 |                    |  |

|                |                                                                        | Delay (ns)        |            |  |

|----------------|------------------------------------------------------------------------|-------------------|------------|--|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |  |

| UART           |                                                                        |                   |            |  |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |  |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |  |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

231

L LD 177 LDC 177 LDCI 176, 177 LDE 177 LDEI 176, 177 LDX 177 LEA 177 load 177 load constant 176 load constant to/from program memory 177 load constant with auto-increment addresses 177 load effective address 177 load external data 177 load external data to/from data memory and auto-increment addresses 176 load external to/from data memory and auto-increment addresses 177 load instructions 177 load using extended addressing 177 logical AND 177 logical AND/extended addressing 177 logical exclusive OR 178 logical exclusive OR/extended addressing 178 logical instructions 177 logical OR 177 logical OR/extended addressing 178 low power modes 31

# Μ

master interrupt enable 55 memory data 15 program 13 mode CAPTURE 84, 85 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 84 ONE-SHOT 84 PWM 84, 85 modes 84 MULT 175 multiply 175 MULTIPROCESSOR mode, UART 99

# Ν

NOP (no operation) 176 notation b 173 cc 173 DA 173 ER 173 IM 173 IR 173 Ir 173 **IRR 173** Irr 173 p 173 R 173 r 173 RA 173 RR 173 rr 173 vector 173 X 173 notational shorthand 173

### O OCD

architecture 151 auto-baud detector/generator 154 baud rate limits 155 block diagram 151 breakpoints 156 commands 157 control register 161 data format 154 DBG pin to RS-232 Interface 152 DEBUG mode 153 debugger break 178 interface 152 serial errors 155