Welcome to **E-XFL.COM**

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413ph005sc |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

viii

| Flash Information Area                                       | 130 |

|--------------------------------------------------------------|-----|

| Operation                                                    | 131 |

| Flash Operation Timing Using the Flash Frequency Registers   | 133 |

| Flash Code Protection Against External Access                |     |

| Flash Code Protection Against Accidental Program and Erasure |     |

| Byte Programming                                             |     |

| Page Erase                                                   |     |

| Mass Erase                                                   |     |

| Flash Controller Bypass                                      |     |

| Flash Controller Behavior in DEBUG Mode                      | 136 |

| Flash Control Register Definitions                           |     |

| Flash Control Register                                       |     |

| Flash Status Register                                        |     |

| Flash Page Select Register                                   |     |

| Flash Sector Protect Register                                |     |

| Flash Frequency High and Low Byte Registers                  | 139 |

| Flash Option Bits                                            | 141 |

| Operation                                                    | 141 |

| Option Bit Configuration By Reset                            | 141 |

| Option Bit Types                                             | 141 |

| Reading the Flash Information Page                           | 143 |

| Flash Option Bit Control Register Definitions                | 143 |

| Trim Bit Address Register                                    | 143 |

| Trim Bit Data Register                                       | 144 |

| Flash Option Bit Address Space                               | 144 |

| Flash Program Memory Address 0000H                           | 144 |

| Flash Program Memory Address 0001H                           | 145 |

| Trim Bit Address Space                                       | 146 |

| Trim Bit Address 0000H—Reserved                              | 146 |

| Trim Bit Address 0001H—Reserved                              | 146 |

| Trim Bit Address 0002H                                       |     |

| Trim Bit Address 0003H—Reserved                              | 147 |

| Trim Bit Address 0004H—Reserved                              | 147 |

| Zilog Calibration Data                                       | 147 |

| ADC Calibration Data                                         | 147 |

| Serialization Data                                           | 148 |

| Randomized Lot Identifier                                    | 149 |

| On-Chip Debugger                                             | 151 |

| Architecture                                                 |     |

PS024314-0308 Table of Contents

## Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F0823 Series device is in STOP mode and the external  $\overline{RESET}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{RESET}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see Electrical Characteristics on page 193.

## **Reset Register Definitions**

### **Reset Status Register**

The Reset Status (RSTSTAT) register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer control register, which is write-only (Table 12).

Table 12. Reset Status Register (RSTSTAT)

| BITS  | 7                | 6            | 5     | 4 | 3        | 2 | 1 | 0 |  |  |

|-------|------------------|--------------|-------|---|----------|---|---|---|--|--|

| FIELD | POR STOP WDT EXT |              |       |   | Reserved |   |   |   |  |  |

| RESET | See d            | lescriptions | below | 0 | 0        | 0 | 0 | 0 |  |  |

| R/W   | R                | R            | R     | R | R        | R | R | R |  |  |

| ADDR  |                  | FF0H         |       |   |          |   |   |   |  |  |

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event is occurred. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

### **Architecture**

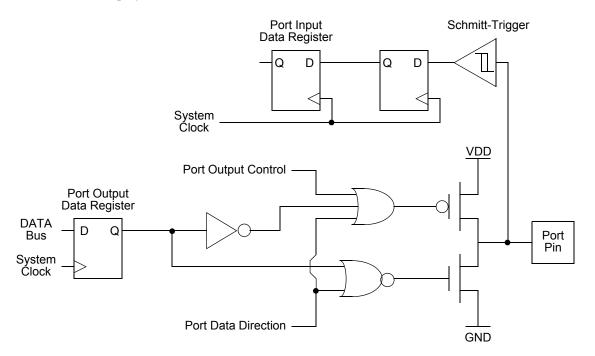

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 7. GPIO Port Pin Block Diagram

### **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function sub-registers configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 15 on page 39 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PAO and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

page 49. See GPIO Alternate Functions on page 36 to determine the alternate function associated with each port pin.

## **Caution:** Do not enable alternate functions for GPIO port pins for which there is no

associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 21. Port A–C Alternate Function Sub-Registers (PxAF)

| BITS  | 7                                                                                     | 6          | 5           | 4             | 3             | 2             | 1            | 0        |  |  |

|-------|---------------------------------------------------------------------------------------|------------|-------------|---------------|---------------|---------------|--------------|----------|--|--|

| FIELD | AF7         AF6         AF5         AF4         AF3         AF2         AF1         A |            |             |               |               |               |              |          |  |  |

| RESET | 00H (Ports A–C); 04H (Port A of 8-pin device)                                         |            |             |               |               |               |              |          |  |  |

| R/W   |                                                                                       | R/W        |             |               |               |               |              |          |  |  |

| ADDR  | If 02H i                                                                              | n Port A–C | Address Reg | gister, acces | sible througl | n the Port A- | -C Control F | Register |  |  |

AF[7:0]—Port Alternate Function enabled

0 =The port pin is in normal mode and the DDx bit in the Port A–C Data Direction subregister determines the direction of the pin.

1 = The alternate function selected through Alternate Function Set sub-registers is enabled. Port pin operation is controlled by the alternate function.

### Port A-C Output Control Sub-Registers

The Port A–C Output Control sub-register (Table 22) is accessed through the Port A–C Control register by writing 03H to the Port A–C Address register. Setting the bits in the Port A–C Output Control sub-registers to 1 configures the specified port pins for opendrain operation. These sub-registers affect the pins directly and, as a result, alternate functions are also affected.

Table 22. Port A–C Output Control Sub-Registers (PxOC)

| BITS  | 7        | 6                                                                                     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |

|-------|----------|---------------------------------------------------------------------------------------|------|------|------|------|------|------|--|--|--|

| FIELD | POC7     | POC6                                                                                  | POC5 | POC4 | POC3 | POC2 | POC1 | POC0 |  |  |  |

| RESET | 0        | 0                                                                                     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |  |

| R/W   | R/W      | R/W                                                                                   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |  |

| ADDR  | If 03H i | If 03H in Port A–C Address Register, accessible through the Port A–C Control Register |      |      |      |      |      |      |  |  |  |

POC[7:0]—Port Output Control

These bits function independently of the alternate function bit and always disable the drains if set to 1.

Table 41. IRQ1 Enable High Bit Register (IRQ1ENH)

| BITS  | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|---------|---------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PA7VENH | PA6CENH | PA5ENH | PA4ENH | PA3ENH | PA2ENH | PA1ENH | PA0ENH |  |  |  |

| RESET | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |         | FC4H    |        |        |        |        |        |        |  |  |  |

PA7VENH—Port A Bit[7] Interrupt Request Enable High Bit

PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit

PAxENH—Port A Bit[x] Interrupt Request Enable High Bit

For selection of Port A as the interrupt source, see Shared Interrupt Select Register on page 64.

Table 42. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5      | 4      | 3      | 2      | 1      | 0      |  |  |  |

|-------|---------|---------|--------|--------|--------|--------|--------|--------|--|--|--|

| FIELD | PA7VENL | PA6CENL | PA5ENL | PA4ENL | PA3ENL | PA2ENL | PA1ENL | PA0ENL |  |  |  |

| RESET | 0       | 0       | 0      | 0      | 0      | 0      | 0      | 0      |  |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |  |  |  |

| ADDR  |         | FC5H    |        |        |        |        |        |        |  |  |  |

PA7VENH—Port A Bit[7] Interrupt Request Enable Low Bit PA6CENH—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

## IRQ2 Enable High and Low Bit Registers

Table 43 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers (Table 44 and Table 45) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register.

Table 43. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

PS024314-0308 Interrupt Controller

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the PWM Control register to set the PWM dead band delay value. The deadband delay must be less than the duration of the positive phase of the PWM signal (as defined by the PWM high and low byte registers). It must also be less than the duration of the negative phase of the PWM signal (as defined by the difference between the PWM registers and the Timer Reload registers).

- 5. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 6. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 7. Configure the associated GPIO port pin for the Timer Output and Timer Output Complement alternate functions. The Timer Output Complement function is shared with the Timer Input function for both timers. Setting the timer mode to Dual PWM automatically switches the function from Timer In to Timer Out Complement.

- 8. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$$PWM \ Period \ (s) = \frac{Reload \ Value \times Prescale}{System \ Clock \ Frequency \ (Hz)}$$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, the ONE-SHOT mode equation determines the first PWM time-out period.

If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by:

PWM Output High Time Ratio (%) =

$$\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$$

### **CAPTURE Mode**

In CAPTURE mode, the current timer count value is recorded when the appropriate external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge

PS024314-0308 **Timers**

Table 59. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS     | 7              | 6                                  | 5             | 4               | 3             | 2            | 1   | 0 |  |  |

|----------|----------------|------------------------------------|---------------|-----------------|---------------|--------------|-----|---|--|--|

| FIELD    | WDTU           |                                    |               |                 |               |              |     |   |  |  |

| RESET    | 00H            |                                    |               |                 |               |              |     |   |  |  |

| R/W      | R/W*           | R/W* R/W* R/W* R/W* R/W* R/W* R/W* |               |                 |               |              |     |   |  |  |

| ADDR     | FF1H           |                                    |               |                 |               |              |     |   |  |  |

| R/W*—Rea | ad returns the | current WD                         | Γ count value | . Write sets tl | ne appropriat | e Reload Val | ue. |   |  |  |

WDTU—WDT Reload Upper Byte

Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

Table 60. Watchdog Timer Reload High Byte Register (WDTH)

| BITS     | 7              | 6           | 5            | 4              | 3             | 2            | 1    | 0    |  |  |

|----------|----------------|-------------|--------------|----------------|---------------|--------------|------|------|--|--|

| FIELD    | WDTH           |             |              |                |               |              |      |      |  |  |

| RESET    |                | 04H         |              |                |               |              |      |      |  |  |

| R/W      | R/W*           | R/W*        | R/W*         | R/W*           | R/W*          | R/W*         | R/W* | R/W* |  |  |

| ADDR     | FF2H           |             |              |                |               |              |      |      |  |  |

| R/W*—Rea | ad returns the | current WDT | count value. | Write sets the | e appropriate | Reload Value | ).   |      |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

Table 61. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS     | 7                                                                                       | 6                                  | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|----------|-----------------------------------------------------------------------------------------|------------------------------------|---|---|---|---|---|---|--|--|

| FIELD    | WDTL                                                                                    |                                    |   |   |   |   |   |   |  |  |

| RESET    | 00H                                                                                     |                                    |   |   |   |   |   |   |  |  |

| R/W      | R/W*                                                                                    | R/W* R/W* R/W* R/W* R/W* R/W* R/W* |   |   |   |   |   |   |  |  |

| ADDR     | FF3H                                                                                    |                                    |   |   |   |   |   |   |  |  |

| R/W*—Rea | R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |                                    |   |   |   |   |   |   |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

PS024314-0308 Watchdog Timer

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send  $(\overline{CTS})$  input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{CTS}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{CTS}$  deasserts in the middle of a character transmission, the current character is sent completely.

### **MULTIPROCESSOR (9-Bit) Mode**

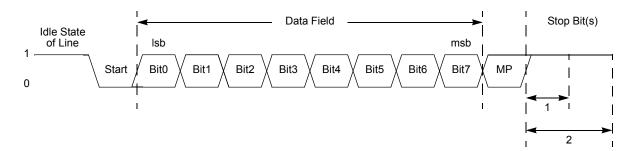

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made

126

## Flash Memory

The products in Z8 Encore! XP<sup>®</sup> F0823 Series features either 8 KB (8192), 4 KB (4096), 2 KB (2048) or 1 KB (1024) of non-volatile Flash memory with read/write/erase capability. Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash Memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program/data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F0823 Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes in size (all other memory sizes); each sector maps to a page. Page and sector sizes are not generally equal.

The first two bytes of the Flash Program memory are used as Flash Option Bits. For more information on their operation, see Flash Option Bits on page 141.

Table 77 describes the Flash memory configuration for each device in the Z8 Encore! XP F0823 Series. Figure 20 displays the Flash memory arrangement.

Table 77. Z8 Encore! XP F0823 Series Flash Memory Configurations

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08x3     | 8 (8192)                 | 16             | 0000H-1FFFH                 | 1024                         |

| Z8F04x3     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02x3     | 2 (2048)                 | 4              | 0000H-07FFH                 | 512                          |

| Z8F01x3     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

PS024314-0308 Flash Memory

## **Flash Control Register Definitions**

### Flash Control Register

The Flash Controller must be unlocked using the Flash Control (FTCTL) register before programming or erasing the Flash memory. Writing the sequence 73H 8CH, sequentially, to the Flash Control register unlocks the Flash Controller. When the Flash Controller is unlocked, the Flash memory can be enabled for Mass Erase or Page Erase by writing the appropriate enable command to the FCTL. Page Erase applies only to the active page selected in Flash Page Select register. Mass Erase is enabled only through the On-Chip Debugger. Writing an invalid value or an invalid sequence returns the Flash Controller to its locked state. The Write-only Flash Control Register shares its Register File address with the read-only Flash Status Register.

Table 79. Flash Control Register (FCTL)

| BITS  | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---|---|----|----|---|---|---|

| FIELD |   |   |   | FC | MD |   |   |   |

| RESET | 0 | 0 | 0 | 0  | 0  | 0 | 0 | 0 |

| R/W   | W | W | W | W  | W  | W | W | W |

| ADDR  |   |   |   | FF | 8H |   |   |   |

FCMD—Flash Command

73H = First unlock command

8CH = Second unlock command

95H = Page Erase command (must be third command in sequence to initiate Page Erase)

63H = Mass Erase command (must be third command in sequence to initiate Mass Erase)

5EH = Enable Flash Sector Protect Register Access

## Flash Status Register

The Flash Status register indicates the current state of the Flash Controller. This register can be read at any time. The read-only Flash Status Register shares its Register File address with the write-only Flash Control Register.

Table 80. Flash Status Register (FSTAT)

| BITS  | 7    | 6     | 5    | 4     | 3 | 2 | 1 | 0 |  |  |  |  |

|-------|------|-------|------|-------|---|---|---|---|--|--|--|--|

| FIELD | Rese | erved |      | FSTAT |   |   |   |   |  |  |  |  |

| RESET | 0    | 0     | 0    | 0     | 0 | 0 | 0 | 0 |  |  |  |  |

| R/W   | R    | R     | R    | R     | R | R | R | R |  |  |  |  |

| ADDR  |      |       | FF8H |       |   |   |   |   |  |  |  |  |

PS024314-0308 Flash Memory

## Flash Option Bits

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP® F0823 Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection—interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Factory trimming information for the internal precision oscillator

- Factory calibration values for ADC

- Factory serialization and randomized lot identifier (optional)

## **Operation**

## Option Bit Configuration By Reset

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0823 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device

PS024314-0308 Flash Option Bits

Reserved— Altering this register may result in incorrect device operation.

### **Trim Bit Address 0002H**

Table 91. Trim Option Bits at 0002H (TIPO)

| BITS      | 7                                               | 6                             | 5 | 4  | 3   | 2 | 0 |  |  |  |  |  |  |

|-----------|-------------------------------------------------|-------------------------------|---|----|-----|---|---|--|--|--|--|--|--|

| FIELD     |                                                 | IPO_TRIM                      |   |    |     |   |   |  |  |  |  |  |  |

| RESET     |                                                 | U                             |   |    |     |   |   |  |  |  |  |  |  |

| R/W       |                                                 |                               |   | R/ | W . |   |   |  |  |  |  |  |  |

| ADDR      |                                                 | Information Page Memory 0022H |   |    |     |   |   |  |  |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |                               |   |    |     |   |   |  |  |  |  |  |  |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

### Trim Bit Address 0003H—Reserved

### Trim Bit Address 0004H—Reserved

## **Zilog Calibration Data**

### **ADC Calibration Data**

**Table 92. ADC Calibration Bits**

| BITS                                            | 7                                   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD                                           | ADC_CAL                             |     |     |     |     |     |     |     |  |  |  |  |

| RESET                                           | U                                   | U   | U   | U   | U   | U   | U   | U   |  |  |  |  |

| R/W                                             | R/W                                 | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR                                            | Information Page Memory 0060H–007DH |     |     |     |     |     |     |     |  |  |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                                     |     |     |     |     |     |     |     |  |  |  |  |

ADC\_CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in

.

PS024314-0308 Flash Option Bits

Software Compensation Procedure on page 122. The location of each calibration byte is provided in Table 93 on page 148.

**Table 93. ADC Calibration Data Location**

| Info Page<br>Address | Memory<br>Address | Compensation<br>Usage | ADC Mode                | Reference<br>Type |

|----------------------|-------------------|-----------------------|-------------------------|-------------------|

| 60                   | FE60              | Offset                | Single-Ended Unbuffered | Internal 2.0 V    |

| 08                   | FE08              | Gain High Byte        | Single-Ended Unbuffered | Internal 2.0 V    |

| 09                   | FE09              | Gain Low Byte         | Single-Ended Unbuffered | Internal 2.0 V    |

| 63                   | FE63              | Offset                | Single-Ended Unbuffered | Internal 1.0 V    |

| 0A                   | FE0A              | Gain High Byte        | Single-Ended Unbuffered | Internal 1.0 V    |

| 0B                   | FE0B              | Gain Low Byte         | Single-Ended Unbuffered | Internal 1.0 V    |

| 66                   | FE66              | Offset                | Single-Ended Unbuffered | External 2.0 V    |

| 0C                   | FE0C              | Gain High Byte        | Single-Ended Unbuffered | External 2.0 V    |

| 0D                   | FE0D              | Gain Low Byte         | Single-Ended Unbuffered | External 2.0 V    |

### **Serialization Data**

Table 94. Serial Number at 001C-001F (S\_NUM)

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD     | S_NUM                                           |     |     |     |     |     |     |     |  |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR      | Information Page Memory 001C-001F               |     |     |     |     |     |     |     |  |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |  |

S NUM— Serial Number Byte

The serial number is a unique four-byte binary value.

PS024314-0308 Flash Option Bits

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

Write Program Counter (06H)—The Write Program Counter command writes the data

that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode

or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are

discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG ← 07H

DBG → ProgramCounter[15:8]

DBG → ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG ← 08H

DBG ← {4'h0,Register Address[11:8]}

DBG ← Register Address[7:0]

DBG ← Size[7:0]

DBG ← 1-256 data bytes

```

• Read Register (09H)—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG ← 09H

DBG ← {4'h0,Register Address[11:8]}

DBG ← Register Address[7:0]

DBG ← Size[7:0]

DBG → 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device

PS024314-0308 On-Chip Debugger

### **Watchdog Timer Failure**

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

## **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control register.

## Oscillator Control Register

The Oscillator Control register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

Table 102. Oscillator Control Register (OSCCTL)

| BITS  | 7     | 6        | 5     | 4     | 3     | 2      | 1   | 0   |  |  |

|-------|-------|----------|-------|-------|-------|--------|-----|-----|--|--|

| FIELD | INTEN | Reserved | WDTEN | POFEN | WDFEN | SCKSEL |     |     |  |  |

| RESET | 1     | 0        | 1     | 0     | 0     | 0      | 0   | 0   |  |  |

| R/W   | R/W   | R/W      | R/W   | R/W   | R/W   | R/W    | R/W | R/W |  |  |

| ADDR  |       |          |       | F8    | 6H    |        |     |     |  |  |

PS024314-0308 Oscillator Control

Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                            | Addre       | ss Mode     | e<br>- Opcode(s) | Fla | ıgs |              |         |   |   | – Fetch | Instr. |

|-----------------|------------------------------------------------------------|-------------|-------------|------------------|-----|-----|--------------|---------|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                         | dst         | src         | (Hex)            | С   | Z   | s            | ٧       | D | Н | Cycles  |        |

| COM dst         | dst ← ~dst                                                 | R           |             | 60               | _   | *   | *            | 0       | _ | - | 2       | 2      |

|                 |                                                            | IR          |             | 61               | _   |     |              |         |   |   | 2       | 3      |

| CP dst, src     | dst - src                                                  | r           | r           | A2               | *   | *   | *            | *       | _ | _ | 2       | 3      |

|                 |                                                            | r           | lr          | A3               | _   |     |              |         |   |   | 2       | 4      |

|                 |                                                            | R           | R           | A4               | _   |     |              |         |   |   | 3       | 3      |

|                 |                                                            | R           | IR          | A5               | _   |     |              |         |   |   | 3       | 4      |

|                 |                                                            | R           | IM          | A6               | _   |     |              |         |   |   | 3       | 3      |

|                 |                                                            | IR          | IM          | A7               | _   |     |              |         |   |   | 3       | 4      |

| CPC dst, src    | dst - src - C                                              | r           | r           | 1F A2            | *   | *   | *            | *       | _ | - | 3       | 3      |

|                 |                                                            | r           | lr          | 1F A3            | _   |     |              |         |   |   | 3       | 4      |

|                 |                                                            | R           | R           | 1F A4            | _   |     |              |         |   |   | 4       | 3      |

|                 |                                                            | R           | IR          | 1F A5            | _   |     |              |         |   |   | 4       | 4      |

|                 |                                                            | R           | IM          | 1F A6            | _   |     |              |         |   |   | 4       | 3      |

|                 |                                                            | IR          | IM          | 1F A7            | _   |     |              |         |   |   | 4       | 4      |

| CPCX dst, src   | dst - src - C                                              | ER          | ER          | 1F A8            | *   | *   | *            | *       | _ | _ | 5       | 3      |

|                 |                                                            | ER          | IM          | 1F A9            | _   |     |              |         |   |   | 5       | 3      |

| CPX dst, src    | dst - src                                                  | ER          | ER          | A8               | *   | *   | *            | *       | - | _ | 4       | 3      |

|                 |                                                            | ER          | IM          | A9               | _   |     |              |         |   |   | 4       | 3      |

| DA dst          | dst ← DA(dst)                                              | R           |             | 40               | *   | *   | *            | Χ       | - | _ | 2       | 2      |

|                 |                                                            | IR          |             | 41               | _   |     |              |         |   |   | 2       | 3      |

| DEC dst         | dst ← dst - 1                                              | R           |             | 30               | _   | *   | *            | *       | _ | - | 2       | 2      |

|                 |                                                            | IR          |             | 31               | _   |     |              |         |   |   | 2       | 3      |

| DECW dst        | dst ← dst - 1                                              | RR          |             | 80               | -   | *   | *            | *       | - | - | 2       | 5      |

|                 |                                                            | IRR         |             | 81               | _   |     |              |         |   |   | 2       | 6      |

| DI              | IRQCTL[7] ← 0                                              |             |             | 8F               | -   | _   | _            | -       | - | - | 1       | 2      |

| DJNZ dst, RA    | dst ← dst − 1<br>if dst ≠ 0<br>PC ← PC + X                 | r           |             | 0A-FA            | -   | _   | -            | _       | - | - | 2       | 3      |

| El              | IRQCTL[7] ← 1                                              |             |             | 9F               | _   | _   | _            | _       | _ | _ | 1       | 2      |

| Flags Notation: | * = Value is a function<br>- = Unaffected<br>X = Undefined | of the resu | It of the o | pperation.       |     |     | ese<br>et to | to<br>1 | 0 |   |         |        |

PS024314-0308 eZ8 CPU Instruction Set

Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                                                                                              | Addre      | ss Mode     | - Opcode(s) | Fla | ıgs          |   |         |   |   | – Fetch | Inetr  |

|-----------------|------------------------------------------------------------------------------------------------------------------------------|------------|-------------|-------------|-----|--------------|---|---------|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                                                                           | dst        | src         | (Hex)       | С   | Z            | s | ٧       | D | Н |         | Cycles |

| SUBX dst, src   | dst ← dst – src                                                                                                              | ER         | ER          | 28          | *   | *            | * | *       | 1 | * | 4       | 3      |

|                 |                                                                                                                              | ER         | IM          | 29          | _   |              |   |         |   |   | 4       | 3      |

| SWAP dst        | $dst[7:4] \leftrightarrow dst[3:0]$                                                                                          | R          |             | F0          | Х   | *            | * | Χ       | - | - | 2       | 2      |

|                 |                                                                                                                              | IR         |             | F1          | _   |              |   |         |   |   | 2       | 3      |

| TCM dst, src    | (NOT dst) AND src                                                                                                            | r          | r           | 62          | -   | *            | * | 0       | - | - | 2       | 3      |

|                 |                                                                                                                              | r          | lr          | 63          | _   |              |   |         |   |   | 2       | 4      |

|                 |                                                                                                                              | R          | R           | 64          | _   |              |   |         |   |   | 3       | 3      |

|                 |                                                                                                                              | R          | IR          | 65          | _   |              |   |         |   |   | 3       | 4      |

|                 |                                                                                                                              | R          | IM          | 66          | _   |              |   |         |   |   | 3       | 3      |

|                 |                                                                                                                              | IR         | IM          | 67          | _   |              |   |         |   |   | 3       | 4      |

| TCMX dst, src   | (NOT dst) AND src                                                                                                            | ER         | ER          | 68          | -   | *            | * | 0       | - | - | 4       | 3      |

|                 |                                                                                                                              | ER         | IM          | 69          | _   |              |   |         |   |   | 4       | 3      |

| TM dst, src     | dst AND src                                                                                                                  | r          | r           | 72          | -   | *            | * | 0       | - | - | 2       | 3      |

|                 |                                                                                                                              | r          | lr          | 73          | _   |              |   |         |   |   | 2       | 4      |

|                 |                                                                                                                              | R          | R           | 74          | _   |              |   |         |   |   | 3       | 3      |

|                 |                                                                                                                              | R          | IR          | 75          | _   |              |   |         |   |   | 3       | 4      |

|                 |                                                                                                                              | R          | IM          | 76          | _   |              |   |         |   |   | 3       | 3      |

|                 |                                                                                                                              | IR         | IM          | 77          | _   |              |   |         |   |   | 3       | 4      |

| TMX dst, src    | dst AND src                                                                                                                  | ER         | ER          | 78          | _   | *            | * | 0       | _ | _ | 4       | 3      |

|                 |                                                                                                                              | ER         | IM          | 79          | _   |              |   |         |   |   | 4       | 3      |

| TRAP Vector     | $SP \leftarrow SP - 2$<br>$@SP \leftarrow PC$<br>$SP \leftarrow SP - 1$<br>$@SP \leftarrow FLAGS$<br>$PC \leftarrow @Vector$ |            | Vector      | F2          | _   | _            | _ | _       | _ | _ | 2       | 6      |

| WDT             |                                                                                                                              |            |             | 5F          | -   | _            | _ | _       | - | - | 1       | 2      |

| Flags Notation: | * = Value is a function o<br>- = Unaffected<br>X = Undefined                                                                 | f the resu | It of the o | peration.   |     | = Re<br>= Se |   | to<br>1 | 0 |   |         |        |

PS024314-0308 eZ8 CPU Instruction Set

Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|        |                     | $V_{DD} = 3.0 \text{ V to } 3.6 \text{ V}$ $T_A = 0 \text{ °C to +70 °C}$ (unless otherwise stated)  Arameter Minimum Typical Maximum |     | 70 °C    |       |                                           |

|--------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------|-----|----------|-------|-------------------------------------------|

| Symbol | Parameter           |                                                                                                                                       |     | Maximum  | Units | Conditions                                |

| Zin    | Input Impedance     | _                                                                                                                                     | 150 |          | kΩ    | In unbuffered mode at 20 MHz <sup>5</sup> |

|        |                     |                                                                                                                                       |     |          |       |                                           |

| Vin    | Input Voltage Range | 0                                                                                                                                     |     | $V_{DD}$ | V     | Unbuffered Mode                           |

|        |                     |                                                                                                                                       |     |          |       |                                           |

#### Notes

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30 °C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

**Table 126. Comparator Electrical Characteristics**

|                   |                       |                 | = 2.7 V to<br>40 °C to + |                    |       |                    |

|-------------------|-----------------------|-----------------|--------------------------|--------------------|-------|--------------------|

| Symbol            | Parameter             | Minimum         | Minimum Typical Max      |                    | Units | Conditions         |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                        |                    | mV    |                    |

| V <sub>CREF</sub> | Programmable Internal |                 | <u>+</u> 5               |                    | %     | 20-/28-pin devices |

|                   | Reference Voltage     |                 | <u>+</u> 3               |                    | %     | 8-pin devices      |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                      |                    | ns    |                    |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                        |                    | mV    |                    |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V     |                    |

## **General Purpose I/O Port Input Data Sample Timing**

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

PS024314-0308 Electrical Characteristics

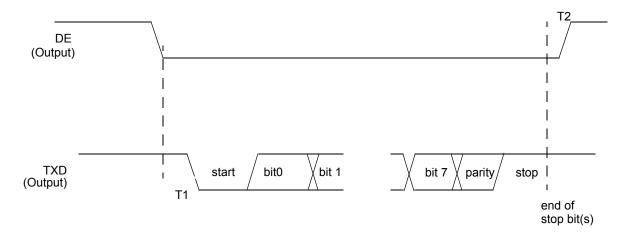

Figure 33 and Table 131 provide timing information for UART pins for the case where CTS is not used for flow control. DE asserts after the transmit data register has been written. DE remains asserted for multiple characters as long as the transmit data register is written with the next character before the current character has completed.

Figure 33. UART Timing Without CTS

**Table 131. UART Timing Without CTS**

|                |                                                                        | Delay (ns)        |            |

|----------------|------------------------------------------------------------------------|-------------------|------------|

| Parameter      | Abbreviation                                                           | Minimum           | Maximum    |

| UART           |                                                                        |                   |            |

| T <sub>1</sub> | DE assertion to TXD falling edge (start bit) delay                     | 1 * XIN<br>period | 1 bit time |

| T <sub>2</sub> | End of Stop Bit(s) to DE deassertion delay (Tx data register is empty) | ± 5               |            |

PS024314-0308 Electrical Characteristics