Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                |                                                           |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413pj005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

| Address (Hex)   | Register Description      | Mnemonic | Reset (Hex) | Page No |  |

|-----------------|---------------------------|----------|-------------|---------|--|

| F0C             | Timer 1 PWM High Byte     | T1PWMH   | 00          | 81      |  |

| F0D             | Timer 1 PWM Low Byte      | T1PWML   | 00          | 82      |  |

| F0E             | Timer 1 Control 0         | T1CTL0   | 00          | 82      |  |

| F0F             | Timer 1 Control 1         | T1CTL1   | 00          | 80      |  |

| F10–F3F         | Reserved                  | —        | XX          |         |  |

| UART            |                           |          |             |         |  |

| F40             | UART0 Transmit Data       | U0TXD    | XX          | 104     |  |

|                 | UART0 Receive Data        | U0RXD    | XX          | 105     |  |

| F41             | UART0 Status 0            | U0STAT0  | 0000011Xb   | 105     |  |

| F42             | UART0 Control 0           | U0CTL0   | 00          | 107     |  |

| F43             | UART0 Control 1           | U0CTL1   | 00          | 107     |  |

| F44             | UART0 Status 1            | U0STAT1  | 00          | 106     |  |

| F45             | UART0 Address Compare     | U0ADDR   | 00          | 109     |  |

| F46             | UART0 Baud Rate High Byte | U0BRH    | FF          | 110     |  |

| F47             | UART0 Baud Rate Low Byte  | U0BRL    | FF          | 110     |  |

| F48–F6F         | Reserved                  | _        | XX          |         |  |

| Analog-to-Digit | al Converter (ADC)        |          |             |         |  |

| F70             | ADC Control 0             | ADCCTL0  | 00          | 122     |  |

| F71             | ADC Control 1             | ADCCTL1  | 80          | 122     |  |

| F72             | ADC Data High Byte        | ADCD_H   | XX          | 124     |  |

| F73             | ADC Data Low Bits         | ADCD_L   | XX          | 124     |  |

| F74–F7F         | Reserved                  | _        | XX          |         |  |

| Low Power Cor   | ntrol                     |          |             |         |  |

| F80             | Power Control 0           | PWRCTL0  | 80          | 33      |  |

| F81             | Reserved                  |          | XX          |         |  |

| LED Controller  |                           |          |             |         |  |

| F82             | LED Drive Enable          | LEDEN    | 00          | 51      |  |

| F83             | LED Drive Level High Byte | LEDLVLH  | 00          | 51      |  |

| F84             | LED Drive Level Low Byte  | LEDLVLL  | 00          | 52      |  |

| F85             | Reserved                  | _        | XX          |         |  |

| Oscillator Cont | rol                       |          |             |         |  |

| F86             | Oscillator Control        | OSCCTL   | A0          | 167     |  |

| F87–F8F         | Reserved                  | _        | XX          |         |  |

| Comparator 0    |                           |          |             |         |  |

| F90             | Comparator 0 Control      | CMP0     | 14          | 128     |  |

|                 |                           |          |             |         |  |

vector address. Following Stop Mode Recovery, the STOP bit in the Watchdog Timer Control Register is set to 1. Table 11 lists the Stop Mode Recovery sources and resulting actions. The section following the table provides more detailed information on each of the Stop Mode Recovery sources.

#### Table 11. Stop Mode Recovery Sources and Resulting Action

| Operating Mode | Stop Mode Recovery Source                                                      | Action                                                              |  |  |  |  |

|----------------|--------------------------------------------------------------------------------|---------------------------------------------------------------------|--|--|--|--|

| STOP mode      | Watchdog Timer time-out when configured for Reset                              | Stop Mode Recovery                                                  |  |  |  |  |

|                | Watchdog Timer time-out when configured for interrupt                          | Stop Mode Recovery followed by interrup (if interrupts are enabled) |  |  |  |  |

|                | Data transition on any GPIO port pin<br>enabled as a Stop Mode Recovery source | Stop Mode Recovery                                                  |  |  |  |  |

|                | Assertion of external RESET Pin                                                | System Reset                                                        |  |  |  |  |

|                | Debug Pin driven Low                                                           | System Reset                                                        |  |  |  |  |

### Stop Mode Recovery Using Watchdog Timer Time-Out

If the Watchdog Timer times out during STOP mode, the device undergoes a Stop Mode Recovery sequence. In the Watchdog Timer Control register, the WDT and STOP bits are set to 1. If the Watchdog Timer is configured to generate an interrupt upon time-out and Z8 Encore! XP<sup>®</sup> F0823 Series device is configured to respond to interrupts, the eZ8 CPU services the Watchdog Timer interrupt request following the normal Stop Mode Recovery sequence.

### Stop Mode Recovery Using a GPIO Port Pin Transition

Each of the GPIO port pins can be configured as a Stop Mode Recovery input source. On any GPIO pin enabled as a Stop Mode Recovery source, a change in the input pin value (from High to Low or from Low to High) initiates Stop Mode Recovery.

- **Note:** The SMR pulses shorter than specified does not trigger a recovery. When this happens, the STOP bit in the Reset Status (RSTSTAT) register is set to 1.

- **Caution:** In STOP mode, the GPIO Port Input Data registers (PxIN) are disabled. The Port Input Data registers record the port transition only if the signal stays on the port pin through the end of the Stop Mode Recovery delay. As a result, short pulses on the port pin can initiate Stop Mode Recovery without being written to the Port Input Data register or without initiating an interrupt (if enabled for that pin).

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. For more details, see Timers on page 67.

**Caution:** For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

## **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA, and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current can result in excessive total current. For the maximum total current for the applicable package, see Electrical Characteristics on page 193.

## **Shared Reset Pin**

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, take care that no external stimulus drives the pin Low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

## **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer func-

# Timers

Z8 Encore! XP<sup>®</sup> F0823 Series products contain up to two 16-bit reloadable timers that are used for timing, event counting, or generation of PWM signals. The timers' features include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the baud rate generator of the UART (if unused) also provides basic timing functionality. For information on using the baud rate generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 93.

# Architecture

Figure 9 displays the architecture of the timers. Timer Block Timer Data Bus Control Block Control Timer 16-Bit Interrupt, Compare Interrupt **Reload Register** PWM, and Timer Timer Output Output System Control Timer Clock 16-Bit Counter I Output with Prescaler Timer Complement Input Compare I Gate 16-Bit Input PWM/Compare Capture Input

Figure 9. Timer Block Diagram

- 0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

- 10 = Timer Interrupt only on defined Input Capture/Deassertion Events

- 11 = Timer Interrupt only on defined Reload/Compare Events

Reserved-Must be 0

#### PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

000 = No delay 001 = 2 cycles delay 010 = 4 cycles delay 011 = 8 cycles delay 100 = 16 cycles delay 101 = 32 cycles delay 110 = 64 cycles delay111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| BITS  | 7   | 6          | 5          | 4   | 3   | 2     | 1   | 0   |  |  |

|-------|-----|------------|------------|-----|-----|-------|-----|-----|--|--|

| FIELD | TEN | TPOL       | PRES TMODE |     |     |       |     |     |  |  |

| RESET | 0   | 0          | 0          | 0   | 0   | 0 0 0 |     |     |  |  |

| R/W   | R/W | R/W        | R/W        | R/W | R/W | R/W   | R/W | R/W |  |  |

| ADDR  |     | F07H, F0FH |            |     |     |       |     |     |  |  |

Table 56. Timer 0–1 Control Register 1 (TxCTL1)

TEN—Timer Enable

0 = Timer is disabled

1 = Timer enabled to count

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer

86

010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value.

0000 = ONE-SHOT mode

0001 = CONTINUOUS mode

0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

- 1000 = PWM DUAL OUTPUT mode

- 1001 = CAPTURE RESTART mode

- 1010 = COMPARATOR COUNTER Mode

# Universal Asynchronous Receiver/Transmitter

The universal asynchronous receiver/transmitter (UART) is a full-duplex communication channel capable of handling asynchronous data transfers. The UART uses a single 8-bit data mode with selectable parity. The features of UART include:

- 8-bit asynchronous data transfer

- Selectable even- and odd-parity generation and checking

- Option of one or two STOP bits

- Separate transmit and receive interrupts

- Framing, parity, overrun, and break detection

- Separate transmit and receive enables

- 16-bit baud rate generator (BRG)

- Selectable MULTIPROCESSOR (9-bit) mode with three configurable interrupt schemes

- BRG can be configured and used as a basic 16-bit timer

- Driver Enable output for external bus transceivers

#### Architecture

The UART consists of three primary functional blocks: transmitter, receiver, and baud rate generator. The UART's transmitter and receiver function independently, but employ the same baud rate and data format. Figure 10 displays the UART architecture.

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

## Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

## **MULTIPROCESSOR (9-Bit) Mode**

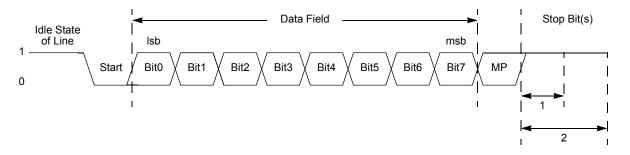

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made

108

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |  |

|-------|---------|------|---------|------|-------|--------|--------|------|--|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |  |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |

| ADDR  | F43H    |      |         |      |       |        |        |      |  |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F0823 Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Factory trimming information for the internal precision oscillator

- Factory calibration values for ADC

- Factory serialization and randomized lot identifier (optional)

# Operation

## **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0823 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device

```

DBG \leftarrow 05H

DBG \rightarrow OCDCTL[7:0]

```

• Write Program Counter (06H)—The Write Program Counter command writes the data that follows to the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the Program Counter (PC) values are discarded.

```

DBG ← 06H

DBG ← ProgramCounter[15:8]

DBG ← ProgramCounter[7:0]

```

• **Read Program Counter (07H)**—The Read Program Counter command reads the value in the eZ8 CPU's Program Counter (PC). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFFFH.

```

DBG \leftarrow 07H

DBG \rightarrow ProgramCounter[15:8]

DBG \rightarrow ProgramCounter[7:0]

```

• Write Register (08H)—The Write Register command writes data to the Register File. Data can be written 1–256 bytes at a time (256 bytes can be written by setting size to 0). If the device is not in DEBUG mode, the address and data values are discarded. If the Flash Read Protect Option bit is enabled, only writes to the Flash Control Registers are allowed and all other register write data values are discarded.

```

DBG \leftarrow 08H

DBG \leftarrow {4'h0,Register Address[11:8]}

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-256 data bytes

```

• **Read Register (09H)**—The Read Register command reads data from the Register File. Data can be read 1–256 bytes at a time (256 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, this command returns FFH for all the data values.

```

DBG \leftarrow 09H

DBG \leftarrow {4'h0,Register Address[11:8]

DBG \leftarrow Register Address[7:0]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-256 data bytes

```

• Write Program Memory (0AH)—The Write Program Memory command writes data to Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). The on-chip Flash Controller must be written to and unlocked for the programming operation to occur. If the Flash Controller is not unlocked, the data is discarded. If the device

|   |                           |                            |                              |                                |                            |                             | Lo                            | ower Nil                       | oble (He                      | x)                             |                            |                          |                    |                           |                  |                          |

|---|---------------------------|----------------------------|------------------------------|--------------------------------|----------------------------|-----------------------------|-------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|--------------------|---------------------------|------------------|--------------------------|

|   | 0                         | 1                          | 2                            | 3                              | 4                          | 5                           | 6                             | 7                              | 8                             | 9                              | А                          | В                        | С                  | D                         | Е                | F                        |

| 0 | 1.1<br>BRK                | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1 | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM    | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br>LD<br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1        | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM    | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                    |                           |                  | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1          | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1 | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM    | 3.4<br><b>SUB</b><br>IR1,IM    | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1, 2<br>ATM              |

| 3 | 2.2<br><b>DEC</b><br>R1   | 2.3<br><b>DEC</b><br>IR1   | 2.3<br><b>SBC</b><br>r1,r2   | 2.4<br><b>SBC</b><br>r1,lr2    | 3.3<br><b>SBC</b><br>R2,R1 | 3.4<br><b>SBC</b><br>IR2,R1 | 3.3<br><b>SBC</b><br>R1,IM    | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                    |                           |                  |                          |

| 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1  | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM     | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                    |                           |                  |                          |

| 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br>AND<br>r1,r2          | 2.4<br>AND<br>r1,lr2           | 3.3<br><b>AND</b><br>R2,R1 | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM    | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                    |                           |                  | 1.2<br>WDT               |

| 6 | 2.2<br>COM<br>R1          | 2.3<br>COM<br>IR1          | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1 | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM    | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.2<br>STOP              |

| 7 | 2.2<br>PUSH<br>R2         | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1  | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM     | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>HALT              |

| 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,Irr2 | 2.9<br><b>LDEI</b><br>Ir1,Irr2 | 3.2<br>LDX<br>r1,ER2       | 3.3<br>LDX<br>lr1,ER2       | 3.4<br>LDX<br>IRR2,R1         | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                    |                           |                  | 1.2<br>DI                |

| 9 | 2.2<br><b>RL</b><br>R1    | 2.3<br><b>RL</b><br>IR1    | 2.5<br><b>LDE</b><br>r2,Irr1 | 2.9<br><b>LDEI</b><br>Ir2,Irr1 | 3.2<br>LDX<br>r2,ER1       | 3.3<br>LDX<br>lr2,ER1       | 3.4<br>LDX<br>R2,IRR1         | 3.5<br><b>LDX</b><br>IR2,IRR1  | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                    |                           |                  | 1.2<br>El                |

| А | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1  | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM     | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.4<br>RET               |

| В | 2.2<br>CLR<br>R1          | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1 | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM    | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.5<br>IRET              |

| С | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,Irr2 | 2.9<br>LDCI<br>Ir1,Irr2        | 2.3<br><b>JP</b><br>IRR1   | 2.9<br>LDC<br>lr1,lrr2      |                               | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                    |                           |                  | 1.2<br>RCF               |

| D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1        | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA             | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                    |                           |                  | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1  | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM     | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1         | 2.3<br><b>SWAP</b><br>IR1  | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1  | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b><br>p,b,r1,X | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | V                          | V                        | ▼                  | ♥                         | ▼                |                          |

Figure 27. First Opcode Map

190

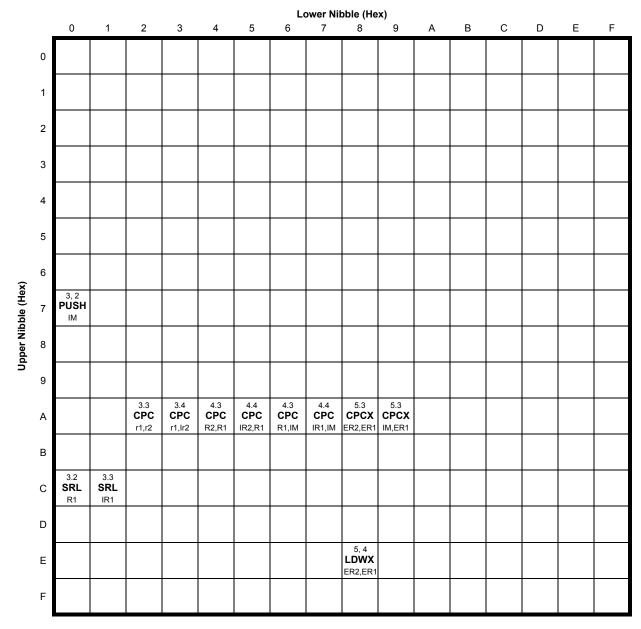

Upper Nibble (Hex)

Figure 28. Second Opcode Map after 1FH

191

#### 197

#### Table 119. Power Consumption (Continued)

|                                                                                                               |                 | V <sub>DE</sub>      | <sub>o</sub> = 2.7 V to 3 | 3.6 V                |       |                        |  |  |

|---------------------------------------------------------------------------------------------------------------|-----------------|----------------------|---------------------------|----------------------|-------|------------------------|--|--|

|                                                                                                               |                 |                      | Maximum <sup>2</sup>      | Maximum <sup>3</sup> |       |                        |  |  |

| Symbol                                                                                                        | Parameter       | Typical <sup>1</sup> | Std Temp                  | Ext Temp             | Units | Conditions             |  |  |

| I <sub>DD</sub> BG                                                                                            | Band Gap Supply | 320                  | 480                       | 500                  | μA    | For 20-/28-pin devices |  |  |

|                                                                                                               | Current         |                      |                           |                      |       | For 8-pin devices      |  |  |

| <b>Notes</b><br>1. Typical conditions are defined as $V_{DD} = 3.3 \text{ V}$ and $\pm 30 ^{\circ}\text{C}$ . |                 |                      |                           |                      |       |                        |  |  |

Typical conditions are defined as V<sub>DD</sub> = 3.3 V and +30 °C.

Standard temperature is defined as T<sub>A</sub> = 0 °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                                   |                                                                                                                                                                | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise<br>stated) |                   |       |                                           |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------------------------------|--|--|--|--|--|

| Symbol                            | Parameter                                                                                                                                                      | Minimum                                                                                                | Maximum           | Units | Conditions                                |  |  |  |  |  |

| F <sub>SYSCLK</sub>               | System Clock Frequency                                                                                                                                         | _                                                                                                      | 20.0 <sup>1</sup> | MHz   | Read-only from Flash memory               |  |  |  |  |  |

|                                   |                                                                                                                                                                | 0.032768                                                                                               | 20.0 <sup>1</sup> | MHz   | Program or erasure of the<br>Flash memory |  |  |  |  |  |

| T <sub>XIN</sub>                  | System Clock Period                                                                                                                                            | 50                                                                                                     | _                 | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>  |  |  |  |  |  |

| T <sub>XINH</sub>                 | System Clock High Time                                                                                                                                         | 20                                                                                                     | 30                | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| T <sub>XINL</sub>                 | System Clock Low Time                                                                                                                                          | 20                                                                                                     | 30                | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| T <sub>XINR</sub>                 | System Clock Rise Time                                                                                                                                         | -                                                                                                      | 3                 | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| T <sub>XINF</sub>                 | System Clock Fall Time                                                                                                                                         | -                                                                                                      | 3                 | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| <sup>1</sup> System 0<br>Table 12 | <sup>1</sup> System Clock Frequency is limited by the Internal Precision Oscillator on the Z8 Encore! XP <sup>®</sup> F0823 Series. See Table 121 on page 198. |                                                                                                        |                   |       |                                           |  |  |  |  |  |

#### Table 120. AC Characteristics

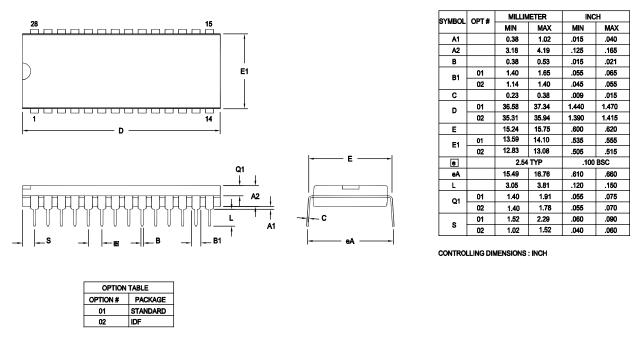

# Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

#### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

page erase 135 page select register 138, 139 FPS register 138, 139 FSTAT register 137

# G

GATED mode 84 general-purpose I/O 35 GPIO 4.35 alternate functions 36 architecture 36 control register definitions 43 input data sample timing 202 interrupts 43 port A-C pull-up enable sub-registers 48, 49 port A-H address registers 44 port A-H alternate function sub-registers 45 port A-H control registers 44 port A-H data direction sub-registers 45 port A-H high drive enable sub-registers 47 port A-H input data registers 49 port A-H output control sub-registers 46 port A-H output data registers 50 port A-H stop mode recovery sub-registers 47 port availability by device 35 port input timing 203 port output timing 204

# Η

H 174 HALT 176 halt mode 32, 176 hexadecimal number prefix/suffix 174

##

I2C 4 IM 173 immediate data 173 immediate operand prefix 174 **INC 175** increment 175 increment word 175 **INCW 175** indexed 173 indirect address prefix 174 indirect register 173 indirect register pair 173 indirect working register 173 indirect working register pair 173 infrared encoder/decoder (IrDA) 113 Instruction Set 171 instruction set. eZ8 CPU 171 instructions ADC 175 **ADCX 175** ADD 175 **ADDX 175** AND 177 **ANDX 177** arithmetic 175 **BCLR 176 BIT 176** bit manipulation 176 block transfer 176 **BRK 178 BSET 176** BSWAP 176, 178 **BTJ 178 BTJNZ 178 BTJZ 178 CALL 178** CCF 176 CLR 177 COM 177 CP 175 **CPC 175 CPCX 175** CPU control 176 **CPX 175** DA 175 **DEC 175 DECW 175**

DI 176