Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | · .                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413pj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **CPU and Peripheral Overview**

# eZ8 CPU Features

The eZ8 CPU, Zilog's latest 8-bit central processing unit (CPU), meets the continuing demand for faster and code-efficient microcontrollers. The eZ8 CPU executes a superset of the original  $Z8^{\text{(R)}}$  instruction set. The eZ8 CPU features include:

- Direct register-to-register architecture allows each register to function as an accumulator, improving execution time and decreasing the required program memory.

- Software stack allows much greater depth in subroutine calls and interrupts than hardware stacks.

- Compatible with existing Z8 code.

- Expanded internal Register File allows access of up to 4 KB.

- New instructions improve execution efficiency for code developed using higher-level programming languages, including C.

- Pipelined instruction fetch and execution.

- New instructions for improved performance including BIT, BSWAP, BTJ, CPC, LDC, LDCI, LEA, MULT, and SRL.

- New instructions support 12-bit linear addressing of the Register file.

- Up to 10 MIPS operation.

- C-Compiler friendly.

- 2 to 9 clock cycles per instruction.

For more information on eZ8 CPU, refer to eZ8 CPU Core User Manual (UM0128) available for download at <u>www.zilog.com</u>.

# General-Purpose I/O

Z8 Encore! XP F0823 Series features 6 to 24 port pins (Ports A–C) for general-purpose I/O (GPIO). The number of GPIO pins available is a function of package. Each pin is individually programmable. 5 V tolerant input pins are available on all I/Os on 8-pin devices, most I/Os on other package types.

# Flash Controller

The Flash Controller programs and erases Flash memory. The Flash Controller supports protection against accidental program and erasure, as well as factory serialization and read protection.

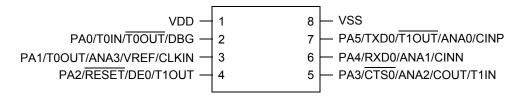

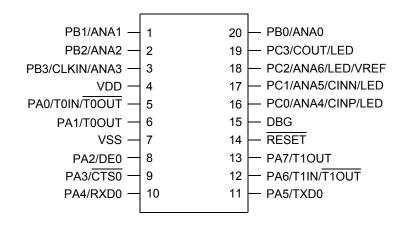

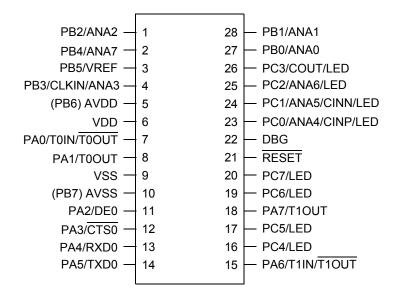

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

#### Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

## Figure 3. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package\*

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\text{(R)}}$  F0823 Series 8-pin devices.

**Note:** All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 4 below describes 5 V-tolerance for the 20- and 28-pin packages only.

|                    |           |                               | Active<br>Low or          |                    |                                  | Schmitt-         |                        |                  |

|--------------------|-----------|-------------------------------|---------------------------|--------------------|----------------------------------|------------------|------------------------|------------------|

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>High            | Tristate<br>Output | Internal Pull-up<br>or Pull-down | Trigger<br>Input | Open Drain<br>Output   | 5 V<br>Tolerance |

| AVDD               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | N/A              |

| AVSS               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | NA               |

| DBG                | I/O       | I                             | N/A                       | Yes                | No                               | Yes              | Yes                    | Yes              |

| PA[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PA[7:2]<br>only  |

| PB[7:0]            | I/O       | Ι                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PB[7:6]<br>only  |

| PC[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PC[7:3]<br>only  |

| RESET              | I/O       | I/O<br>(defaults<br>to RESET) | Low (in<br>Reset<br>mode) | Yes (PD0<br>only)  | Alw <u>ays on</u> for<br>RESET   | Yes              | Always on for<br>RESET | Yes              |

| VDD                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

| VSS                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

#### Table 4. Pin Characteristics (20- and 28-pin Devices)

**Note:** *PB6 and PB7 are available only in the devices without ADC.*

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

## **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–C Control Registers on page 44), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overline{\text{RESET}}$  pin Low. The  $\overline{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) register is set.

# **Stop Mode Recovery**

The device enters into STOP mode when eZ8 CPU executes a STOP instruction. For more details on STOP mode, see Low-Power Modes on page 31. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

WDT-Watchdog Timer time-out Indicator

If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

Reserved-0 when read

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA5 | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         |                                         |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled.

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

## Port A–C Pull-up Enable Sub-Registers

The Port A–C Pull-up Enable sub-register (Table 25) is accessed through the Port A–C Control register by writing 06H to the Port A–C Address register. Setting the bits in the Port A–C Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

Table 25. Port A–C Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| FIELD | PPUE7    | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W                                                           |       |       |       |       |       |       |  |

| ADDR  | lf 06H i | If 06H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |  |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

## Port A–C Alternate Function Set 1 Sub-Registers

The Port A–C Alternate Function Set1 sub-register (Table 26) is accessed through the Port A–C Control register by writing 07H to the Port A–C Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 36.

Note:

*Alternate function selection on port pins must also be enabled as described in* Port A–C Alternate Function Sub-Registers *on page 45*.

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the hold-ing register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

## **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

#### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 =Count occurs on the rising edge of the Timer Input signal

- 1 = Count occurs on the falling edge of the Timer Input signal

#### **PWM SINGLE OUTPUT Mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARE Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### GATED Mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

#### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control register is set to 1. For more information on System Reset, see Reset and Stop Mode Recovery on page 21.

#### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. For more information, see Reset and Stop Mode Recovery on page 21.

## Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Control Register Definitions

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL register address unlocks the three

108

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |

|-------|---------|------|---------|------|-------|--------|--------|------|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |

| ADDR  |         | F43H |         |      |       |        |        |      |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

# **Flash Memory**

The products in Z8 Encore! XP<sup>®</sup> F0823 Series features either 8 KB (8192), 4 KB (4096), 2 KB (2048) or 1 KB (1024) of non-volatile Flash memory with read/write/erase capability. Flash Memory can be programmed and erased in-circuit by either user code or through the On-Chip Debugger.

The Flash Memory array is arranged in pages with 512 bytes per page. The 512-byte page is the minimum Flash block size that can be erased. Each page is divided into 8 rows of 64 bytes.

For program/data protection, the Flash memory is also divided into sectors. In the Z8 Encore! XP F0823 Series, these sectors are either 1024 bytes (in the 8 KB devices) or 512 bytes in size (all other memory sizes); each sector maps to a page. Page and sector sizes are not generally equal.

The first two bytes of the Flash Program memory are used as Flash Option Bits. For more information on their operation, see Flash Option Bits on page 141.

Table 77 describes the Flash memory configuration for each device in the Z8 Encore! XP F0823 Series. Figure 20 displays the Flash memory arrangement.

| Part Number | Flash Size<br>KB (Bytes) | Flash<br>Pages | Program Memory<br>Addresses | Flash Sector<br>Size (bytes) |

|-------------|--------------------------|----------------|-----------------------------|------------------------------|

| Z8F08x3     | 8 (8192)                 | 16             | 0000H–1FFFH                 | 1024                         |

| Z8F04x3     | 4 (4096)                 | 8              | 0000H-0FFFH                 | 512                          |

| Z8F02x3     | 2 (2048)                 | 4              | 0000H–07FFH                 | 512                          |

| Z8F01x3     | 1 (1024)                 | 2              | 0000H-03FFH                 | 512                          |

#### Table 77. Z8 Encore! XP F0823 Series Flash Memory Configurations

138

Reserved—0 when read

FSTAT—Flash Controller Status 000000 = Flash Controller locked 000001 = First unlock command received (73H written) 000010 = Second unlock command received (8CH written) 000011 = Flash Controller unlocked 000100 = Sector protect register selected 001xxx = Program operation in progress 010xxx = Page erase operation in progress 100xxx = Mass erase operation in progress

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6   | 5    | 4   | 3   | 2   | 1   | 0   |

|-------|---------|-----|------|-----|-----|-----|-----|-----|

| FIELD | INFO_EN |     | PAGE |     |     |     |     |     |

| RESET | 0       | 0   | 0    | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W |

| ADDR  |         |     |      | FF  | 9H  |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0.

# Trim Bit Data Register

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

Table 86. Trim Bit Data Register (TRMDR)

| BITS  | 7   | 6                     | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----------------------|-----|-----|-----|-----|-----|-----|

| FIELD |     | TRMDR - Trim Bit Data |     |     |     |     |     |     |

| RESET | 0   | 0                     | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W | R/W                   | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |                       |     | FF  | 7H  |     |     |     |

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

# Flash Program Memory Address 0000H

Table 87. Flash Option Bits at Program Memory Address 0000H

| BITS                                            | 7                    | 6      | 5    | 4     | 3      | 2   | 1        | 0   |

|-------------------------------------------------|----------------------|--------|------|-------|--------|-----|----------|-----|

| FIELD                                           | WDT_RES              | WDT_AO | Rese | erved | VBO_AO | FRP | Reserved | FWP |

| RESET                                           | U                    | U      | U    | U     | U      | U   | U        | U   |

| R/W                                             | R/W                  | R/W    | R/W  | R/W   | R/W    | R/W | R/W      | R/W |

| ADDR                                            | Program Memory 0000H |        |      |       |        |     |          |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |        |      |       |        |     |          |     |

WDT RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always ON

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the

# OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 157).

## **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

## **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

| Debug Command       | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit |

|---------------------|-----------------|---------------------------------------|----------------------------------------------|

| Stuff Instruction   | 11H             | -                                     | Disabled.                                    |

| Execute Instruction | 12H             | -                                     | Disabled.                                    |

| Reserved            | 13H–FFH         | _                                     | _                                            |

In the following list of OCD Commands, data and commands sent from the host to the OCD are identified by 'DBG  $\leftarrow$  Command/Data'. Data sent from the OCD back to the host is identified by 'DBG  $\rightarrow$  Data'.

• **Read OCD Revision (00H)**—The Read OCD Revision command determines the version of the OCD. If OCD commands are added, removed, or changed, this revision number changes.

```

DBG \leftarrow 00H

DBG \rightarrow OCDRev[15:8] (Major revision number)

DBG \rightarrow OCDRev[7:0] (Minor revision number)

```

Read OCD Status Register (02H)—The Read OCD Status register command reads the OCDSTAT register.

```

DBG \leftarrow 02H

DBG \rightarrow OCDSTAT[7:0]

```

Read Runtime Counter (03H)—The Runtime Counter counts system clock cycles in between breakpoints. The 16-bit Runtime Counter counts up from 0000H and stops at the maximum count of FFFFH. The Runtime Counter is overwritten during the Write Memory, Read Memory, Write Register, Read Register, Read Memory CRC, Step Instruction, Stuff Instruction, and Execute Instruction commands.

```

DBG \leftarrow 03H

DBG \rightarrow RuntimeCounter[15:8]

DBG \rightarrow RuntimeCounter[7:0]

```

• Write OCD Control Register (04H)—The Write OCD Control Register command writes the data that follows to the OCDCTL register. When the Flash Read Protect Option Bit is enabled, the DBGMODE bit (OCDCTL[7]) can only be set to 1, it cannot be cleared to 0 and the only method of returning the device to normal operating mode is to reset the device.

```

DBG \leftarrow 04H

DBG \leftarrow OCDCTL[7:0]

```

• **Read OCD Control Register (05H)**—The Read OCD Control Register command reads the value of the OCDCTL register.

168

INTEN—Internal Precision Oscillator Enable

1 = Internal precision oscillator is enabled

0 = Internal precision oscillator is disabled

Reserved—R/W bits must be 0 during writes; 0 when read

WDTEN—Watchdog Timer Oscillator Enable

1 = Watchdog Timer oscillator is enabled

0 = Watchdog Timer oscillator is disabled

POFEN—Primary Oscillator Failure Detection Enable

1 = Failure detection and recovery of primary oscillator is enabled

0 = Failure detection and recovery of primary oscillator is disabled

WDFEN—Watchdog Timer Oscillator Failure Detection Enable

1 = Failure detection of Watchdog Timer oscillator is enabled

0 = Failure detection of Watchdog Timer oscillator is disabled

SCKSEL—System Clock Oscillator Select

000 = Internal precision oscillator functions as system clock at 5.53 MHz

001 = Internal precision oscillator functions as system clock at 32 kHz

010 = Reserved

011 = Watchdog Timer oscillator functions as system clock

100 = External clock signal on PB3 functions as system clock

101 = Reserved

110 = Reserved

111 = Reserved

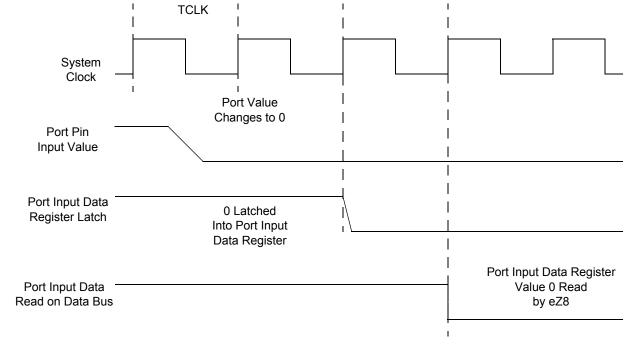

| Table 127 | . GPIO | Port | Input | Timing |

|-----------|--------|------|-------|--------|

|-----------|--------|------|-------|--------|

|                     |                                                                                                    | Delay (ns) |         |  |

|---------------------|----------------------------------------------------------------------------------------------------|------------|---------|--|

| Parameter           | Abbreviation                                                                                       | Minimum    | Maximum |  |

| T <sub>S_PORT</sub> | Port Input Transition to XIN Rise Setup Time (Not pictured)                                        | 5          | _       |  |

| T <sub>H_PORT</sub> | XIN Rise to Port Input Transition Hold Time (Not pictured)                                         | 0          | -       |  |

| T <sub>SMR</sub>    | GPIO Port Pin Pulse Width to ensure Stop Mode Recovery (for GPIO Port Pins enabled as SMR sources) | 1 μs       |         |  |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

208

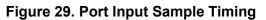

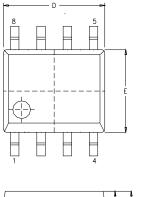

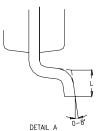

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIMETER |                                                                                     | INCH                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIN        | MAX                                                                                 | MIN                                                                                                                                                                                                                                                                                                    | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.55       | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                                                  | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.10       | 0.25                                                                                | 0.004                                                                                                                                                                                                                                                                                                  | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.40       | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                                                  | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.36       | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                                                  | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.18       | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                                                  | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.80       | 4.98                                                                                | 0.189                                                                                                                                                                                                                                                                                                  | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.81       | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                                                  | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.27 BSC   |                                                                                     | .050 BSC                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.84       | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                                                  | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.25       | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                                                  | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.46       | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                                                  | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | MIN         MAX           1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)