Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413qb005ec |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| On-Chip Debugger Initiated Reset                    | 26 |

|-----------------------------------------------------|----|

| Stop Mode Recovery                                  |    |

| Stop Mode Recovery Using Watchdog Timer Time-Out    |    |

| Stop Mode Recovery Using a GPIO Port Pin Transition |    |

| Stop Mode Recovery Using the External RESET Pin     |    |

| Reset Register Definitions                          |    |

| Low-Power Modes                                     |    |

| STOP Mode                                           |    |

| HALT Mode                                           |    |

| Peripheral-Level Power Control                      | 32 |

| Power Control Register Definitions                  | 32 |

| General-Purpose Input/Output                        | 35 |

| GPIO Port Availability By Device                    | 35 |

| Architecture                                        | 36 |

| GPIO Alternate Functions                            | 36 |

| Direct LED Drive                                    | 37 |

| Shared Reset Pin                                    | 37 |

| Shared Debug Pin                                    | 37 |

| Crystal Oscillator Override                         | 38 |

| 5 V Tolerance                                       |    |

| External Clock Setup                                |    |

| GPIO Interrupts                                     |    |

| GPIO Control Register Definitions                   |    |

| Port A–C Address Registers                          |    |

| Port A–C Control Registers                          |    |

| Port A–C Data Direction Sub-Registers               | 45 |

| Port A–C Alternate Function Sub-Registers           |    |

| Port A–C Input Data Registers                       |    |

| Port A–C Output Data Register                       |    |

|                                                     |    |

| LED Drive Level High Register                       |    |

|                                                     |    |

| Interrupt Controller                                |    |

| Interrupt Vector Listing                            |    |

| Architecture                                        |    |

| Operation                                           |    |

| IVIASIEI IIIIEIIUPI LIIAVIE                         | 00 |

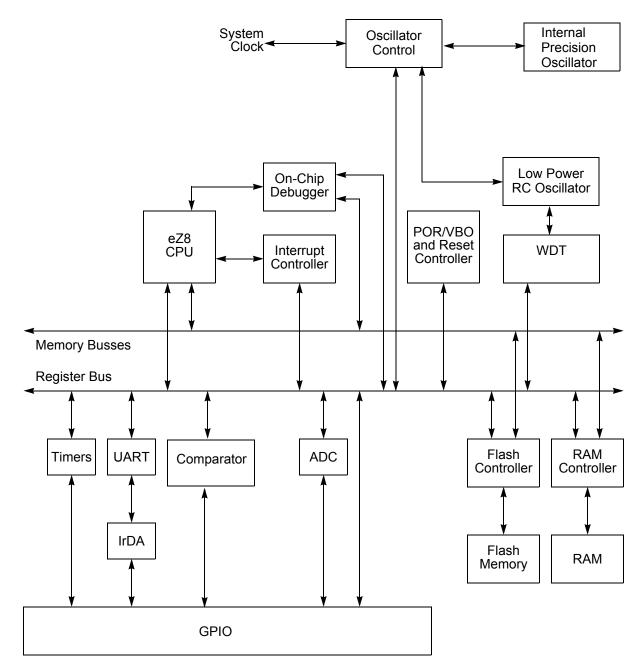

# Block Diagram

Figure 1 on page 3 displays the block diagram of the architecture of Z8 Encore! XP F0823 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0823 Series Block Diagram

Note:

\*Analog input alternate functions (ANA) are not available on the Z8F0x13 devices.

# **Signal Descriptions**

Table 3 lists the Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series signals. To determine the signals available for the specific package styles, see Pin Configurations on page 7.

#### Table 3. Signal Descriptions

| Signal Mnemonic                                       | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C                                   | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                               | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                               | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                               | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| Note: PB6 and PB7 are<br>replaced by AV <sub>DI</sub> |         | /ailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                      |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                  | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                  | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                  | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                    | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                                |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                           | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT                                           | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                             | I       | Timer Input 0–1. These signals are used as the <u>capture</u> , gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                |

| Comparator                                            |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                             | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                  | 0       | Comparator Output. This is the output of the comparator.                                                                                                                                                                                                                                                |

|                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |  |  |

|-----------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|--|--|

| Reset<br>Type         | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |  |  |

| System<br>Reset       | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL and OSC_CTL<br>registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |  |  |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

#### **Reset Sources**

Table 10 lists the possible sources of a System Reset.

| ial Conditions                              |

|---------------------------------------------|

| t delay begins after supply voltage exceeds |

| Table 10. | <b>Reset Sources</b> | and Resulting | Reset Type |

|-----------|----------------------|---------------|------------|

|           |                      | and Resulting | Redet Type |

| Operating Mode       | Reset Source                                      | Special Conditions                                                                                             |

|----------------------|---------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                     |

|                      | Watchdog Timer time-out when configured for Reset | None.                                                                                                          |

|                      | RESET pin assertion                               | All reset pulses less than three system clocks in width are ignored.                                           |

|                      | OCD initiated Reset<br>(OCDCTL[0] set to 1)       | System Reset, except the OCD is unaffected by the reset.                                                       |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                     |

|                      | RESET pin assertion                               | All reset pulses less than the specified analog delay are ignored. See Electrical Characteristics on page 193. |

|                      | DBG pin driven Low                                | None.                                                                                                          |

#### **Power-On Reset**

Each device in the Z8 Encore! XP F0823 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following the POR, the POR status bit in Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 5 displays POR operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 193.

# Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F0823 Series device is in STOP mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see Electrical Characteristics on page 193.

# **Reset Register Definitions**

#### **Reset Status Register**

The Reset Status (RSTSTAT) register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer control register, which is writeonly (Table 12).

#### Table 12. Reset Status Register (RSTSTAT)

| BITS  | 7     | 6            | 5     | 4   | 3        | 2       | 1 | 0 |  |  |  |  |

|-------|-------|--------------|-------|-----|----------|---------|---|---|--|--|--|--|

| FIELD | POR   | STOP         | WDT   | EXT | Reserved |         |   |   |  |  |  |  |

| RESET | See d | lescriptions | below | 0   | 0        | 0 0 0 0 |   |   |  |  |  |  |

| R/W   | R     | R            | R     | R   | R        | R R R R |   |   |  |  |  |  |

| ADDR  |       |              |       | FF  | FOH      |         |   |   |  |  |  |  |

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

#### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event is occurred. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value.

0000 = ONE-SHOT mode

0001 = CONTINUOUS mode

0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

- 1000 = PWM DUAL OUTPUT mode

- 1001 = CAPTURE RESTART mode

- 1010 = COMPARATOR COUNTER Mode

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

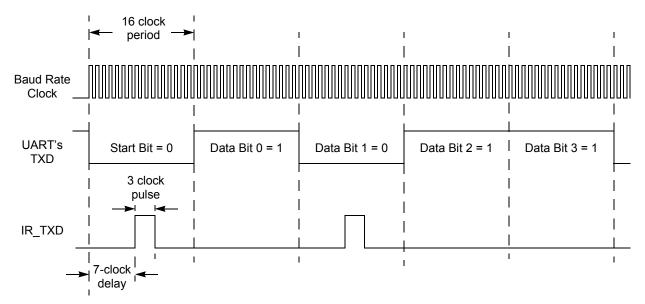

#### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

132

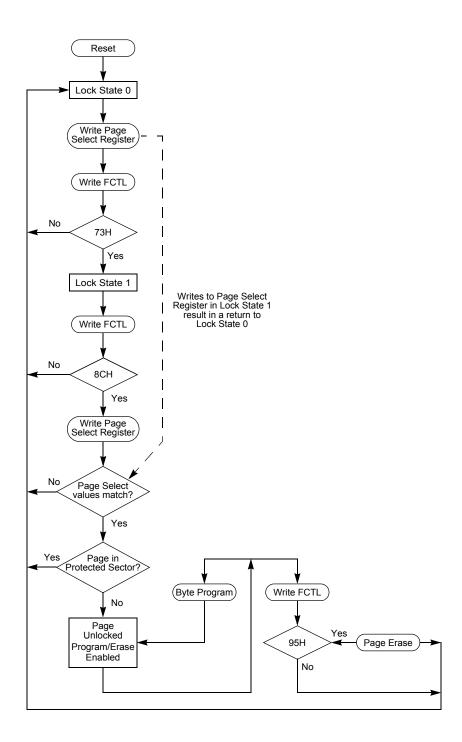

Figure 21. Flash Controller Operation Flowchart

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

INTEN—Internal Precision Oscillator Enable

1 = Internal precision oscillator is enabled

0 = Internal precision oscillator is disabled

Reserved—R/W bits must be 0 during writes; 0 when read

WDTEN—Watchdog Timer Oscillator Enable

1 = Watchdog Timer oscillator is enabled

0 = Watchdog Timer oscillator is disabled

POFEN—Primary Oscillator Failure Detection Enable

1 = Failure detection and recovery of primary oscillator is enabled

0 = Failure detection and recovery of primary oscillator is disabled

WDFEN—Watchdog Timer Oscillator Failure Detection Enable

1 = Failure detection of Watchdog Timer oscillator is enabled

0 = Failure detection of Watchdog Timer oscillator is disabled

SCKSEL—System Clock Oscillator Select

000 = Internal precision oscillator functions as system clock at 5.53 MHz

001 = Internal precision oscillator functions as system clock at 32 kHz

010 = Reserved

011 = Watchdog Timer oscillator functions as system clock

100 = External clock signal on PB3 functions as system clock

101 = Reserved

110 = Reserved

111 = Reserved

| Assembly        |                                                              | Addre       | ss Mode    | -<br>Opcode(s) | Fla | ıgs |              |   | - Fetch | Instr. |   |        |

|-----------------|--------------------------------------------------------------|-------------|------------|----------------|-----|-----|--------------|---|---------|--------|---|--------|

| Mnemonic        | Symbolic Operation                                           | dst         | src        | (Hex)          | С   | z   | S            | v | D       | Н      |   | Cycles |

| LDC dst, src    | $dst \gets src$                                              | r           | Irr        | C2             | -   | _   |              | _ | _       | -      | 2 | 5      |

|                 |                                                              | lr          | Irr        | C5             | _   |     |              |   |         |        | 2 | 9      |

|                 |                                                              | Irr         | r          | D2             | _   |     |              |   |         |        | 2 | 5      |

| LDCI dst, src   | $dst \leftarrow src$                                         | lr          | Irr        | C3             | -   | _   | _            | _ | _       | _      | 2 | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr         | lr         | D3             | _   |     |              |   |         |        | 2 | 9      |

| LDE dst, src    | $dst \gets src$                                              | r           | Irr        | 82             | -   | _   |              | _ | _       | -      | 2 | 5      |

|                 |                                                              | Irr         | r          | 92             | _   |     |              |   |         |        | 2 | 5      |

| LDEI dst, src   | $dst \gets src$                                              | lr          | Irr        | 83             | -   | _   |              | _ | _       | -      | 2 | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr         | lr         | 93             | _   |     |              |   |         |        | 2 | 9      |

| LDWX dst, src   | $dst \leftarrow src$                                         | ER          | ER         | 1FE8           | _   | _   | . <u> </u>   | _ | _       | _      | 5 | 4      |

| LDX dst, src    | $dst \gets src$                                              | r           | ER         | 84             | -   | _   |              | _ | _       | _      | 3 | 2      |

|                 |                                                              | lr          | ER         | 85             | _   |     |              |   |         |        | 3 | 3      |

|                 |                                                              | R           | IRR        | 86             | _   |     |              |   |         |        | 3 | 4      |

|                 |                                                              | IR          | IRR        | 87             | _   |     |              |   |         |        | 3 | 5      |

|                 |                                                              | r           | X(rr)      | 88             | _   |     |              |   |         |        | 3 | 4      |

|                 |                                                              | X(rr)       | r          | 89             | _   |     |              |   |         |        | 3 | 4      |

|                 |                                                              | ER          | r          | 94             | _   |     |              |   |         |        | 3 | 2      |

|                 |                                                              | ER          | lr         | 95             | _   |     |              |   |         |        | 3 | 3      |

|                 |                                                              | IRR         | R          | 96             | _   |     |              |   |         |        | 3 | 4      |

|                 |                                                              | IRR         | IR         | 97             | _   |     |              |   |         |        | 3 | 5      |

|                 |                                                              | ER          | ER         | E8             | _   |     |              |   |         |        | 4 | 2      |

|                 |                                                              | ER          | IM         | E9             | _   |     |              |   |         |        | 4 | 2      |

| LEA dst, X(src) | $dst \gets src + X$                                          | r           | X(r)       | 98             | -   | _   |              | _ | _       | -      | 3 | 3      |

|                 |                                                              | rr          | X(rr)      | 99             |     |     |              |   |         |        | 3 | 5      |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR          |            | F4             | -   | _   |              | _ | _       | -      | 2 | 8      |

| NOP             | No operation                                                 |             |            | 0F             | -   | _   |              | _ | _       | -      | 1 | 2      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resul | t of the c | operation.     |     |     | ese<br>et to |   | 0       |        |   |        |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                                  | Addre   | ss Mode     | - Opcode(s) | Fla | ıgs |              | - Fetch | Instr. |   |          |   |

|-----------------|------------------------------------------------------------------|---------|-------------|-------------|-----|-----|--------------|---------|--------|---|----------|---|

| Mnemonic        | Symbolic Operation                                               | dst     | src         | (Hex)       | С   | Ζ   | S            | v       | D      | Н | Cycles C |   |

| RR dst          |                                                                  | R       |             | E0          | *   | *   | *            | *       | _      | - | 2        | 2 |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                             | IR      |             | E1          | -   |     |              |         |        |   | 2        | 3 |

| RRC dst         |                                                                  | R       |             | C0          | *   | *   | *            | *       | _      | - | 2        | 2 |

|                 | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR      |             | C1          | _   |     |              |         |        |   | 2        | 3 |

| SBC dst, src    | $dst \gets dst - src - C$                                        | r       | r           | 32          | *   | *   | *            | *       | 1      | * | 2        | 3 |

|                 |                                                                  | r       | lr          | 33          | _   |     |              |         |        |   | 2        | 4 |

|                 |                                                                  | R       | R           | 34          |     |     |              |         |        |   | 3        | 3 |

|                 |                                                                  | R       | IR          | 35          | _   |     |              |         |        |   | 3        | 4 |

|                 |                                                                  | R       | IM          | 36          |     |     |              |         |        |   | 3        | 3 |

|                 |                                                                  | IR      | IM          | 37          |     |     |              |         |        |   | 3        | 4 |

| SBCX dst, src   | $dst \gets dst - src - C$                                        | ER      | ER          | 38          | *   | *   | *            | *       | 1      | * | 4        | 3 |

|                 |                                                                  | ER      | IM          | 39          | _   |     |              |         |        |   | 4        | 3 |

| SCF             | C ← 1                                                            |         |             | DF          | 1   | -   | -            | _       | _      | - | 1        | 2 |

| SRA dst         | <b>*</b> *                                                       | R       |             | D0          | *   | *   | *            | 0       | _      | - | 2        | 2 |

|                 | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR      |             | D1          |     |     |              |         |        |   | 2        | 3 |

| SRL dst         |                                                                  | R       |             | 1F C0       | *   | *   | 0            | *       | _      | - | 3        | 2 |

|                 | dst                                                              | IR      |             | 1F C1       |     |     |              |         |        |   | 3        | 3 |

| SRP src         | $RP \leftarrow src$                                              |         | IM          | 01          | _   | _   | _            | _       | _      | _ | 2        | 2 |

| STOP            | STOP Mode                                                        |         |             | 6F          | _   | _   | _            | _       | _      | - | 1        | 2 |

| SUB dst, src    | $dst \gets dst - src$                                            | r       | r           | 22          | *   | *   | *            | *       | 1      | * | 2        | 3 |

|                 |                                                                  | r       | lr          | 23          | _   |     |              |         |        |   | 2        | 4 |

|                 |                                                                  | R       | R           | 24          | _   |     |              |         |        |   | 3        | 3 |

|                 |                                                                  | R       | IR          | 25          | _   |     |              |         |        |   | 3        | 4 |

|                 |                                                                  | R       | IM          | 26          | -   |     |              |         |        |   | 3        | 3 |

|                 |                                                                  | IR      | IM          | 27          | _   |     |              |         |        |   | 3        | 4 |

| Flags Notation: | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu | It of the o | peration.   |     |     | ese<br>et to |         | 0      |   |          |   |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

#### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|        |                     | T <sub>A</sub> = | = 3.0 V to<br>0 °C to +<br>otherwis | 70 °C           |       |                                      |

|--------|---------------------|------------------|-------------------------------------|-----------------|-------|--------------------------------------|

| Symbol | Parameter           | Minimum          | Typical                             | Maximum         | Units | Conditions                           |

| Zin    | Input Impedance     | -                | 150                                 |                 | kΩ    | In unbuffered mode at 20 $\rm MHz^5$ |

|        |                     |                  |                                     |                 |       |                                      |

| Vin    | Input Voltage Range | 0                |                                     | V <sub>DD</sub> | V     | Unbuffered Mode                      |

|        |                     |                  |                                     |                 |       |                                      |

Notes

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30 °C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| Table 126. C | Comparator | Electrical | Characteristics |

|--------------|------------|------------|-----------------|

|--------------|------------|------------|-----------------|

|                   |                       |                 | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |                    |       |                    |

|-------------------|-----------------------|-----------------|------------------------------------------------------------------------|--------------------|-------|--------------------|

| Symbol            | Parameter             | Minimum         | Typical                                                                | Maximum            | Units | Conditions         |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                                                                      |                    | mV    |                    |

|                   | Programmable Internal |                 | <u>+</u> 5                                                             |                    | %     | 20-/28-pin devices |

|                   | Reference Voltage     |                 | <u>+</u> 3                                                             |                    | %     | 8-pin devices      |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                                                                    |                    | ns    |                    |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                                                                      |                    | mV    |                    |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                                                                        | V <sub>DD</sub> -1 | V     |                    |

#### General Purpose I/O Port Input Data Sample Timing

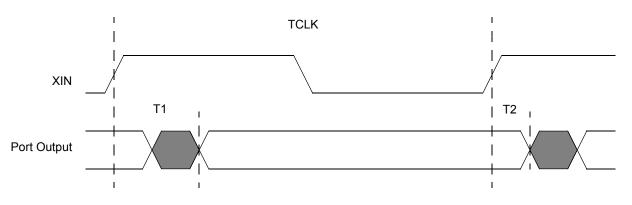

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

# General Purpose I/O Port Output Timing

Figure 30 and Table 128 provide timing information for GPIO Port pins.

#### Figure 30. GPIO Port Output Timing

|                |                                     | Delay (ns) |         |  |  |  |  |

|----------------|-------------------------------------|------------|---------|--|--|--|--|

| Parameter      | Abbreviation                        | Minimum    | Maximum |  |  |  |  |

| GPIO Port pins |                                     |            |         |  |  |  |  |

| T <sub>1</sub> | XIN Rise to Port Output Valid Delay | _          | 15      |  |  |  |  |

| T <sub>2</sub> | XIN Rise to Port Output Hold Time   | 2          | _       |  |  |  |  |

#### Table 128. GPIO Port Output Timing

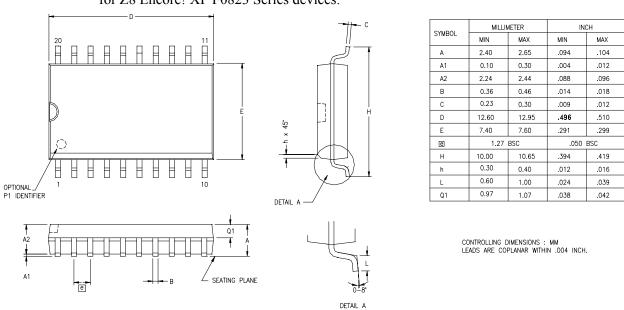

Figure 38 displays the 20-pin Small Outline Integrated Circuit Package (SOIC) available for Z8 Encore! XP F0823 Series devices.

Figure 38. 20-Pin Small Outline Integrated Circuit Package (SOIC)

Figure 39 displays the 20-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

Figure 39. 20-Pin Small Shrink Outline Package (SSOP)

#### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

page erase 135 page select register 138, 139 FPS register 138, 139 FSTAT register 137

# G

GATED mode 84 general-purpose I/O 35 GPIO 4.35 alternate functions 36 architecture 36 control register definitions 43 input data sample timing 202 interrupts 43 port A-C pull-up enable sub-registers 48, 49 port A-H address registers 44 port A-H alternate function sub-registers 45 port A-H control registers 44 port A-H data direction sub-registers 45 port A-H high drive enable sub-registers 47 port A-H input data registers 49 port A-H output control sub-registers 46 port A-H output data registers 50 port A-H stop mode recovery sub-registers 47 port availability by device 35 port input timing 203 port output timing 204

# Η

H 174 HALT 176 halt mode 32, 176 hexadecimal number prefix/suffix 174

##

I2C 4 IM 173 immediate data 173 immediate operand prefix 174 **INC 175** increment 175 increment word 175 **INCW 175** indexed 173 indirect address prefix 174 indirect register 173 indirect register pair 173 indirect working register 173 indirect working register pair 173 infrared encoder/decoder (IrDA) 113 Instruction Set 171 instruction set. eZ8 CPU 171 instructions ADC 175 **ADCX 175** ADD 175 **ADDX 175** AND 177 **ANDX 177** arithmetic 175 **BCLR 176 BIT 176** bit manipulation 176 block transfer 176 **BRK 178 BSET 176** BSWAP 176, 178 **BTJ 178 BTJNZ 178 BTJZ 178 CALL 178** CCF 176 CLR 177 COM 177 CP 175 **CPC 175 CPCX 175** CPU control 176 **CPX 175** DA 175 **DEC 175 DECW 175**

DI 176