Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413qb005sc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

- 2.7 V to 3.6 V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

## **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore! XP<sup>®</sup> F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

WDT-Watchdog Timer time-out Indicator

If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

Reserved-0 when read

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 151.

## **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 167), the GPIO settings are overridden and PA0 and PA1 are disabled.

## **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0], and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

## **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see Oscillator Control Register Definitions on page 167) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA5 | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA7 | T1OUT       | Timer 1 Output                          | -                                       |

|        |     | Reserved    |                                         |                                         |

### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

## **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

## **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

### Table 17. GPIO Port Registers and Sub-Registers

|          | •                                   | •                                                                          |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer on page 87)                             |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          |                                     |                                                                            |

### Table 33. Trap and Interrupt Vectors in Order of Priority

6. Write to the Timer Control register to enable the timer and initiate counting.

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

$ONE-SHOT Mode Time-Out Period (s) = \frac{(Reload Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below to configure a timer for CONTINUOUS mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

### **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1001 = Divide by 2

## Watchdog Timer

The Watchdog Timer (WDT) protects against corrupt or unreliable software, power faults, and other system-level problems which can place Z8 Encore! XP<sup>®</sup> F0823 Series devices into unsuitable operating states. The features of Watchdog Timer include:

- On-chip RC oscillator

- A selectable time-out response: reset or interrupt

- 24-bit programmable time-out value

### Operation

The WDT is a retriggerable one-shot timer that resets or interrupts Z8 Encore! XP F0823 Series devices when the WDT reaches its terminal count. The Watchdog Timer uses a dedicated on-chip RC oscillator as its clock source. The Watchdog Timer operates in only two modes: ON and OFF. Once enabled, it always counts and must be refreshed to prevent a time-out. Perform an enable by executing the WDT instruction or by setting the WDT\_AO Flash Option Bit. The WDT\_AO bit forces the Watchdog Timer to operate immediately upon reset, even if a WDT instruction has not been executed.

The Watchdog Timer is a 24-bit reloadable down counter that uses three 8-bit registers in the eZ8 CPU register space to set the reload value. The nominal WDT time-out period is described by the following equation:

WDT Time-out Period (ms) =  $\frac{\text{WDT Reload Value}}{10}$

where the WDT reload value is the decimal value of the 24-bit value given by {WDTU[7:0], WDTH[7:0], WDTL[7:0]} and the typical Watchdog Timer RC oscillator frequency is 10 kHz. The Watchdog Timer cannot be refreshed after it reaches 000002H. The WDT Reload Value must not be set to values below 000004H. Table 57 provides information about approximate time-out delays for the minimum and maximum WDT reload values.

### Table 57. Watchdog Timer Approximate Time-Out Delays

| WDT Reload Value | WDT Reload Value | Approximate Time-Out Delay<br>(with 10 kHz typical WDT oscillator freque |                        |  |  |  |

|------------------|------------------|--------------------------------------------------------------------------|------------------------|--|--|--|

| (Hex)            |                  |                                                                          | Description            |  |  |  |

| 000004           | 4                | 400 μs                                                                   | Minimum time-out delay |  |  |  |

| FFFFF            | 16,777,215       | 28 minutes                                                               | Maximum time-out delay |  |  |  |

bits of resolution are lost because of a rounding error. As a result, the final value is an 11- bit number.

### Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control register.

### Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

### Table 83. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7   | 6    | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |  |

|-------|-----|------|-----|-----|-----|-----|-----|-----|--|--|--|--|

| FIELD |     |      |     | FFR | EQH |     |     |     |  |  |  |  |

| RESET | 0   | 0    | 0   | 0   | 0   | 0   | 0   | 0   |  |  |  |  |

| R/W   | R/W | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |  |

| ADDR  |     | FFAH |     |     |     |     |     |     |  |  |  |  |

FFREQH—Flash Frequency High Byte High byte of the 16-bit Flash Frequency value

### Table 84. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|

| FIELD |   | FFREQL |   |    |    |   |   |   |  |  |

| RESET |   | 0      |   |    |    |   |   |   |  |  |

| R/W   |   | R/W    |   |    |    |   |   |   |  |  |

| ADDR  |   |        |   | FF | BH |   |   |   |  |  |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0AH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

### **Clock Failure Detection and Recovery**

### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. The features of IPO include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

## Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

Power down this block for minimum system power. By default, the oscillator is configured through the Flash Option bits. However, the user code can override these trim values as described in Trim Bit Address Space on page 146.

Select one of the two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 165.

174

Table 106 lists additional symbols that are used throughout the Instruction Summary and Instruction Set Description sections.

|        | -                         |

|--------|---------------------------|

| Symbol | Definition                |

| dst    | Destination Operand       |

| src    | Source Operand            |

| @      | Indirect Address Prefix   |

| SP     | Stack Pointer             |

| PC     | Program Counter           |

| FLAGS  | Flags Register            |

| RP     | Register Pointer          |

| #      | Immediate Operand Prefix  |

| В      | Binary Number Suffix      |

| %      | Hexadecimal Number Prefix |

| Н      | Hexadecimal Number Suffix |

|        |                           |

Table 106. Additional Symbols

Assignment of a value is indicated by an arrow. For example,

$dst \leftarrow dst + src$

indicates the source data is added to the destination data and the result is stored in the destination location.

## eZ8 CPU Instruction Classes

eZ8 CPU instructions are divided functionally into the following groups:

- Arithmetic

- Bit Manipulation

- Block Transfer

- CPU Control

- Load

- Logical

- Program Control

| Assembly        |                                                                  | Addre   | ss Mode     | - Opcode(s) | Fla | ıgs |              |   |   |   |   | Instr.<br>Cycles |

|-----------------|------------------------------------------------------------------|---------|-------------|-------------|-----|-----|--------------|---|---|---|---|------------------|

| Mnemonic        | Symbolic Operation                                               | dst     | src         | (Hex)       | С   | Ζ   | S            | v | D | Н |   |                  |

| RR dst          |                                                                  | R       |             | E0          | *   | *   | *            | * | _ | - | 2 | 2                |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                             | IR      |             | E1          | -   |     |              |   |   |   | 2 | 3                |

| RRC dst         |                                                                  | R       |             | C0          | *   | *   | *            | * | _ | - | 2 | 2                |

|                 | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR      |             | C1          | _   |     |              |   |   |   | 2 | 3                |

| SBC dst, src    | $dst \gets dst - src - C$                                        | r       | r           | 32          | *   | *   | *            | * | 1 | * | 2 | 3                |

|                 |                                                                  | r       | lr          | 33          | _   |     |              |   |   |   | 2 | 4                |

|                 |                                                                  | R       | R           | 34          |     |     |              |   |   |   | 3 | 3                |

|                 |                                                                  | R       | IR          | 35          | _   |     |              |   |   |   | 3 | 4                |

|                 |                                                                  | R       | IM          | 36          |     |     |              |   |   |   | 3 | 3                |

|                 |                                                                  | IR      | IM          | 37          |     |     |              |   |   |   | 3 | 4                |

| SBCX dst, src   | $dst \gets dst - src - C$                                        | ER      | ER          | 38          | *   | *   | *            | * | 1 | * | 4 | 3                |

|                 |                                                                  | ER      | IM          | 39          | _   |     |              |   |   |   | 4 | 3                |

| SCF             | C ← 1                                                            |         |             | DF          | 1   | -   | -            | _ | _ | - | 1 | 2                |

| SRA dst         | <b>T</b> ♥ ♥                                                     | R       |             | D0          | *   | *   | *            | 0 | _ | - | 2 | 2                |

|                 | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR      |             | D1          |     |     |              |   |   |   | 2 | 3                |

| SRL dst         |                                                                  | R       |             | 1F C0       | *   | *   | 0            | * | _ | - | 3 | 2                |

|                 | dst                                                              | IR      |             | 1F C1       |     |     |              |   |   |   | 3 | 3                |

| SRP src         | $RP \leftarrow src$                                              |         | IM          | 01          | _   | _   | _            | _ | _ | _ | 2 | 2                |

| STOP            | STOP Mode                                                        |         |             | 6F          | _   | _   | _            | _ | _ | - | 1 | 2                |

| SUB dst, src    | $dst \gets dst - src$                                            | r       | r           | 22          | *   | *   | *            | * | 1 | * | 2 | 3                |

|                 |                                                                  | r       | lr          | 23          | _   |     |              |   |   |   | 2 | 4                |

|                 |                                                                  | R       | R           | 24          | _   |     |              |   |   |   | 3 | 3                |

|                 |                                                                  | R       | IR          | 25          | _   |     |              |   |   |   | 3 | 4                |

|                 |                                                                  | R       | IM          | 26          | -   |     |              |   |   |   | 3 | 3                |

|                 |                                                                  | IR      | IM          | 27          | _   |     |              |   |   |   | 3 | 4                |

| Flags Notation: | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu | It of the o | peration.   |     |     | ese<br>et to |   | 0 |   |   |                  |

### Table 115. eZ8 CPU Instruction Summary (Continued)

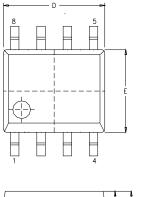

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIMETER |                                                                                     | INCH                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIN        | MAX                                                                                 | MIN                                                                                                                                                                                                                                                                                                    | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 1.55       | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                                                  | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.10       | 0.25                                                                                | 0.004                                                                                                                                                                                                                                                                                                  | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.40       | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                                                  | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.36       | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                                                  | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.18       | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                                                  | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 4.80       | 4.98                                                                                | 0.189                                                                                                                                                                                                                                                                                                  | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 3.81       | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                                                  | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 1.27 BSC   |                                                                                     | .050 BSC                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.84       | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                                                  | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.25       | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                                                  | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 0.46       | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                                                  | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|            | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | MIN         MAX           1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

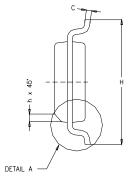

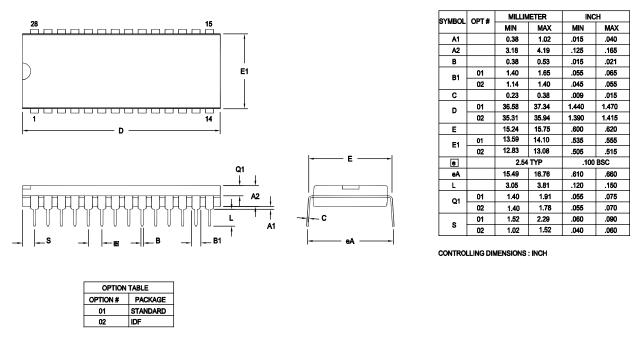

## Figure 40 displays the 28-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Note: ZiLOG supplies both options for production. Component layout PCB design should cover bigger option 01.

### Figure 40. 28-Pin Plastic Dual Inline Package (PDIP)

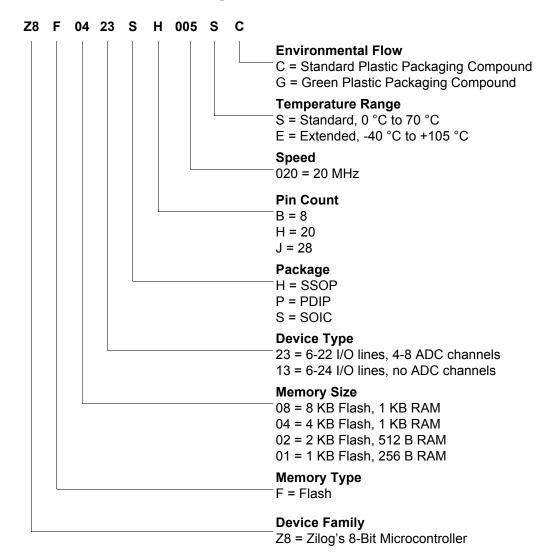

### Part Number Suffix Designations