Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413sh005ec |

# **Table of Contents**

| Overview                                    |   |

|---------------------------------------------|---|

| Features1                                   |   |

| Part Selection Guide                        | • |

| Block Diagram                               |   |

| CPU and Peripheral Overview                 |   |

| eZ8 CPU Features                            |   |

| General-Purpose I/O                         |   |

| Internal Precision Oscillator               |   |

| 10-Bit Analog-to-Digital Converter          |   |

| Analog Comparator                           |   |

| Universal Asynchronous Receiver/Transmitter |   |

| Timers 5                                    |   |

| Interrupt Controller 5                      |   |

| Reset Controller                            |   |

| On-Chip Debugger                            |   |

| Pin Description                             |   |

| Available Packages                          |   |

| Pin Configurations                          |   |

| Signal Descriptions                         |   |

| Pin Characteristics                         |   |

| Address Space                               |   |

| Register File                               |   |

| Program Memory                              |   |

| Data Memory                                 |   |

| Flash Information Area15                    | ) |

| Register Map                                | • |

| Reset and Stop Mode Recovery                |   |

| Reset Types                                 |   |

| Reset Sources                               | ) |

| Power-On Reset                              |   |

| Voltage Brownout Reset 24                   |   |

| Watchdog Timer Reset                        |   |

| External Reset Input                        |   |

| External Reset Indicator                    | • |

PS024314-0308 Table of Contents

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

vi

| Interrupt Vectors and Priority                           |    |

|----------------------------------------------------------|----|

| Interrupt Assertion                                      |    |

| Software Interrupt Assertion                             | 57 |

| Watchdog Timer Interrupt Assertion                       | 57 |

| Interrupt Control Register Definitions                   | 58 |

| Interrupt Request 0 Register                             | 58 |

| Interrupt Request 1 Register                             | 59 |

| Interrupt Request 2 Register                             | 59 |

| IRQ0 Enable High and Low Bit Registers                   | 60 |

| IRQ1 Enable High and Low Bit Registers                   |    |

| IRQ2 Enable High and Low Bit Registers                   |    |

| Interrupt Edge Select Register                           | 63 |

| Shared Interrupt Select Register                         | 64 |

| Interrupt Control Register                               | 64 |

| Timers                                                   | 67 |

| Architecture                                             | 67 |

| Operation                                                | 68 |

| Timer Operating Modes                                    | 68 |

| Reading the Timer Count Values                           | 79 |

| Timer Pin Signal Operation                               | 79 |

| Timer Control Register Definitions                       | 80 |

| Timer 0–1 High and Low Byte Registers                    | 80 |

| Timer Reload High and Low Byte Registers                 | 80 |

| Timer 0-1 PWM High and Low Byte Registers                | 81 |

| Timer 0–1 Control Registers                              | 82 |

| Watchdog Timer                                           | 87 |

| Operation                                                |    |

| Watchdog Timer Refresh                                   |    |

| Watchdog Timer Time-Out Response                         |    |

| Watchdog Timer Reload Unlock Sequence                    |    |

| Watchdog Timer Control Register Definitions              |    |

| Watchdog Timer Control Register                          |    |

| Watchdog Timer Reload Upper, High and Low Byte Registers |    |

| Universal Asynchronous Receiver/Transmitter              | 93 |

| Architecture                                             |    |

| Operation                                                |    |

| Data Format                                              |    |

| Transmitting Data using the Polled Method                |    |

| Transmitting Data using the Interrupt-Driven Method      |    |

|                                                          |    |

PS024314-0308 Table of Contents

| Operation                                               |

|---------------------------------------------------------|

| OCD Interface                                           |

| DEBUG Mode                                              |

| OCD Data Format                                         |

| OCD Auto-Baud Detector/Generator                        |

| OCD Serial Errors                                       |

| OCD Unlock Sequence (8-Pin Devices Only)                |

| Breakpoints                                             |

| Runtime Counter                                         |

| On-Chip Debugger Commands                               |

| On-Chip Debugger Control Register Definitions           |

| OCD Control Register                                    |

| OCD Status Register                                     |

| Oscillator Control 16                                   |

| Operation                                               |

| System Clock Selection                                  |

| Clock Failure Detection and Recovery                    |

| Oscillator Control Register Definitions                 |

| Internal Precision Oscillator                           |

| Operation                                               |

| eZ8 CPU Instruction Set 17                              |

| Assembly Language Programming Introduction              |

| Assembly Language Syntax                                |

| eZ8 CPU Instruction Notation                            |

| eZ8 CPU Instruction Classes                             |

| eZ8 CPU Instruction Summary                             |

| Opcode Maps                                             |

| Electrical Characteristics                              |

|                                                         |

| Absolute Maximum Ratings                                |

| DC Characteristics                                      |

| AC Characteristics                                      |

| On-Chip Peripheral AC and DC Electrical Characteristics |

| General Purpose I/O Port Input Data Sample Timing       |

| General Purpose I/O Port Output Timing                  |

| On-Chip Debugger Timing                                 |

| UART Timing                                             |

| Packaging                                               |

PS024314-0308 Table of Contents

# **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

#### **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

PS024314-0308 Overview

6

### **Reset Controller**

Z8 Encore! XP<sup>®</sup> F0823 Series products can be reset using the RESET pin, POR, WDT time-out, STOP mode exit, or Voltage Brownout warning signal. The RESET pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

### **On-Chip Debugger**

Z8 Encore! XP F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

PS024314-0308 Overview

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

| Program Memory Address (Hex)                  | Function                   |

|-----------------------------------------------|----------------------------|

| 0002–0003                                     | Reset Vector               |

| 0004–0005                                     | WDT Interrupt Vector       |

| 0006–0007                                     | Illegal Instruction Trap   |

| 0008–0037                                     | Interrupt Vectors*         |

| 0038–003D                                     | Oscillator Fail Traps*     |

| 003E-03FF                                     | Program Memory             |

| *See Table 33 on page 54 for a list of the in | terrupt vectors and traps. |

|                                               |                            |

# **Data Memory**

Z8 Encore!  $XP^{\circledR}$  F0823 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

### Flash Information Area

Table 7 lists the Z8 Encore! XP F0823 Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

Table 7. Z8 Encore! XP F0823 Series Flash Memory Information Area Map

| Program Memory Address<br>(Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00-FE3F                       | Zilog Option Bits.                                                                         |

| FE40-FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60-FE7F                       | Zilog Calibration Data.                                                                    |

| FE80-FFFF                       | Reserved.                                                                                  |

PS024314-0308 Address Space

Table 9. Reset and Stop Mode Recovery Characteristics and Latency

|                       | Reset Characteristics and Latency                |            |                                                            |  |  |  |  |

|-----------------------|--------------------------------------------------|------------|------------------------------------------------------------|--|--|--|--|

| Reset<br>Type         | Control Registers                                | eZ8<br>CPU | Reset Latency (Delay)                                      |  |  |  |  |

| System<br>Reset       | Reset (as applicable)                            | Reset      | 66 Internal Precision Oscillator Cycles                    |  |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except WDT_CTL and OSC_CTL registers | Reset      | 66 Internal Precision Oscillator Cycles + IPO startup time |  |  |  |  |

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

#### **Reset Sources**

Table 10 lists the possible sources of a System Reset.

#### **HALT Mode**

Executing the eZ8 CPU's HALT instruction places the device into HALT mode, which powers down the CPU but leaves all other peripherals active. In HALT mode, the operating characteristics are:

- Primary oscillator is enabled and continues to operate.

- System clock is enabled and continues to operate.

- eZ8 CPU is stopped.

- Program counter stops incrementing.

- Watchdog Timer's internal RC oscillator continues to operate.

- If enabled, the Watchdog Timer continues to operate.

- All other on-chip peripherals continue to operate.

The eZ8 CPU can be brought out of HALT mode by any of the following operations:

- Interrupt

- Watchdog Timer time-out (interrupt or reset)

- Power-On Reset

- Voltage Brownout reset

- External RESET pin assertion

To minimize current in HALT mode, all GPIO pins that are configured as inputs must be driven to one of the supply rails (V<sub>CC</sub> or GND).

# **Peripheral-Level Power Control**

In addition to the STOP and HALT modes, it is possible to disable each peripheral on each of the Z8 Encore! XP F0823 Series devices. Disabling a given peripheral minimizes its power consumption.

# **Power Control Register Definitions**

The following sections describe the power control registers.

#### **Power Control Register 0**

Each bit of the following registers disables a peripheral block, either by gating its system clock input or by removing power from the block.

PS024314-0308 Low-Power Modes

**Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)**

| Port   | ort Pin Mnemonic Alternate Function Description |             | Alternate Function<br>Set Register AFS1 |     |  |

|--------|-------------------------------------------------|-------------|-----------------------------------------|-----|--|

| Port A | PA0                                             | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A |  |

|        |                                                 | Reserved    |                                         | -   |  |

|        | PA1                                             | T0OUT       | Timer 0 Output                          | -   |  |

|        |                                                 | Reserved    |                                         | -   |  |

|        | PA2                                             | DE0         | UART 0 Driver Enable                    | _   |  |

|        |                                                 | Reserved    |                                         | _   |  |

|        | PA3                                             | CTS0        | UART 0 Clear to Send                    | _   |  |

|        |                                                 | Reserved    |                                         | _   |  |

|        | PA4                                             | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | _   |  |

|        |                                                 | Reserved    |                                         | _   |  |

|        | PA5                                             | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | _   |  |

|        |                                                 | Reserved    |                                         | _   |  |

|        | PA6                                             | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement | _   |  |

|        |                                                 | Reserved    |                                         | _   |  |

|        | PA7                                             | T1OUT       | Timer 1 Output                          | _   |  |

|        |                                                 | Reserved    |                                         |     |  |

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

<sup>\*</sup> Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

#### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPARATOR COUNTER mode, the prescaler is disabled.

**Caution:** The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COMPARATOR COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER mode. After the first timer Reload in COMPARATOR COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions = Current Count Value - Start Value

PS024314-0308 Timers

timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Follow the steps below to configure a timer for COMPARE mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for Compare mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In COMPARE mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

#### **GATED Mode**

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer Reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

PS024314-0308 Timers

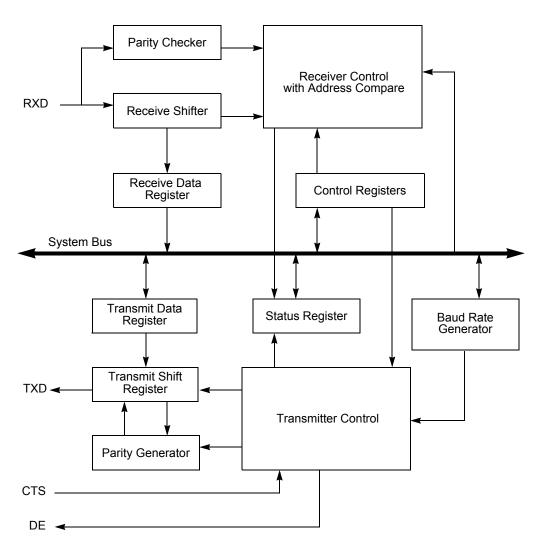

Figure 10. UART Block Diagram

# **Operation**

### **Data Format**

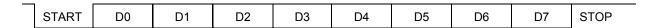

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

0 = Send a 0 in the multiprocessor bit location of the data stream (data byte)

1 = Send a 1 in the multiprocessor bit location of the data stream (address byte)

DEPOL—Driver Enable Polarity

0 = DE signal is Active High

1 = DE signal is Active Low

BRGCTL—Baud Rate Control

This bit causes an alternate UART behavior depending on the value of the REN bit in the UART Control 0 Register.

When the UART receiver is **not** enabled (REN=0), this bit determines whether the Baud Rate Generator issues interrupts.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

1 = The Baud Rate Generator generates a receive interrupt when it counts down to 0. Reads from the Baud Rate High and Low Byte registers return the current BRG count value.

When the UART receiver is enabled (REN=1), this bit allows reads from the Baud Rate Registers to return the BRG count value instead of the Reload Value.

0 = Reads from the Baud Rate High and Low Byte registers return the BRG Reload Value.

1 = Reads from the Baud Rate High and Low Byte registers return the current BRG count value. Unlike the Timers, there is no mechanism to latch the Low Byte when the High Byte is read.

RDAIRO—Receive Data Interrupt Enable

0 = Received data and receiver errors generates an interrupt request to the Interrupt Controller.

1 = Received data does not generate an interrupt request to the Interrupt Controller. Only receiver errors generate an interrupt request.

IREN—Infrared Encoder/Decoder Enable

0 = Infrared Encoder/Decoder is disabled. UART operates normally.

1 = Infrared Encoder/Decoder is enabled. The UART transmits and receives data through the Infrared Encoder/Decoder.

### **UART Address Compare Register**

The UART Address Compare register stores the multi-node network address of the UART. When the MPMD[1] bit of UART Control Register 0 is set, all incoming address bytes are compared to the value stored in the Address Compare register. Receive interrupts and RDA assertions only occur in the event of a match.

value 63H to the Flash Control register initiates the Mass Erase operation. While the Flash Controller executes the Mass Erase operation, the eZ8 CPU idles but the system clock and on-chip peripherals continue to operate. Using the On-Chip Debugger, poll the Flash Status register to determine when the Mass Erase operation is complete. When the Mass Erase is complete, the Flash Controller returns to its locked state.

### Flash Controller Bypass

The Flash Controller can be bypassed and the control signals for the Flash memory brought out to the GPIO pins. Bypassing the Flash Controller allows faster Row Programming algorithms by controlling the Flash programming signals directly.

Row programing is recommended for gang programming applications and large volume customers who do not require in-circuit initial programming of the Flash memory. Page Erase operations are also supported when the Flash Controller is bypassed.

For more information on bypassing the Flash Controller, refer to *Third-Party Flash Programming Support for Z8 Encore!* (AN0117) available for download at <a href="https://www.zilog.com">www.zilog.com</a>.

#### Flash Controller Behavior in DEBUG Mode

The following changes in behavior of the Flash Controller occur when the Flash Controller is accessed using the On-Chip Debugger:

- The Flash Write Protect option bit is ignored

- The Flash Sector Protect register is ignored for programming and erase operations

- Programming operations are not limited to the page selected in the Page Select register

- Bits in the Flash Sector Protect register can be written to one or zero

- The second write of the Page Select register to unlock the Flash Controller is not necessary

- The Page Select register can be written when the Flash Controller is unlocked

- The Mass Erase command is enabled through the Flash Control register

- **Caution:** For security reasons, Flash controller allows only a single page to be opened for write/ erase. When writing multiple Flash pages, the Flash controller must go through the unlock sequence again to select another page.

PS024314-0308 Flash Memory

point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG mode. For more details, see OCD Unlock Sequence (8-Pin Devices Only) on page 156.

#### **Exiting DEBUG Mode**

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the  $\overline{RESET}$  pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a system reset

#### **OCD Data Format**

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

Figure 25. OCD Data Format

Note:

When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open-drain output.

### **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous

PS024314-0308 On-Chip Debugger

#### **Watchdog Timer Failure**

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control register.

# Oscillator Control Register

The Oscillator Control register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

Table 102. Oscillator Control Register (OSCCTL)

| BITS  | 7     | 6        | 5     | 4     | 3     | 2   | 1      | 0   |

|-------|-------|----------|-------|-------|-------|-----|--------|-----|

| FIELD | INTEN | Reserved | WDTEN | POFEN | WDFEN |     | SCKSEL |     |

| RESET | 1     | 0        | 1     | 0     | 0     | 0   | 0      | 0   |

| R/W   | R/W   | R/W      | R/W   | R/W   | R/W   | R/W | R/W    | R/W |

| ADDR  | F86H  |          |       |       |       |     |        |     |

PS024314-0308 Oscillator Control

Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|        |                     | $V_{DD}$ = 3.0 V to 3.6 V<br>$T_A$ = 0 °C to +70 °C<br>(unless otherwise stated) |         |          |       |                                           |

|--------|---------------------|----------------------------------------------------------------------------------|---------|----------|-------|-------------------------------------------|

| Symbol | Parameter           | Minimum                                                                          | Typical | Maximum  | Units | Conditions                                |

| Zin    | Input Impedance     | _                                                                                | 150     |          | kΩ    | In unbuffered mode at 20 MHz <sup>5</sup> |

|        |                     |                                                                                  |         |          |       |                                           |

| Vin    | Input Voltage Range | 0                                                                                |         | $V_{DD}$ | V     | Unbuffered Mode                           |

|        |                     |                                                                                  |         |          |       |                                           |

#### Notes

- 1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

- 2. Devices are factory calibrated at  $V_{DD}$  = 3.3 V and  $T_A$  = +30 °C, so the ADC is maximally accurate under these conditions.

- 3. LSBs are defined assuming 10-bit resolution.

- 4. This is the maximum recommended resistance seen by the ADC input pin.

- 5. The input impedance is inversely proportional to the system clock frequency.

**Table 126. Comparator Electrical Characteristics**

|                   |                       |                 | = 2.7 V to<br>40 °C to + |                    |       |                    |  |

|-------------------|-----------------------|-----------------|--------------------------|--------------------|-------|--------------------|--|

| Symbol            | Parameter             | Minimum         | Typical                  | Maximum            | Units | Conditions         |  |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                        |                    | mV    |                    |  |

| V <sub>CREF</sub> | Programmable Internal |                 | <u>+</u> 5               |                    | %     | 20-/28-pin devices |  |

|                   | Reference Voltage     |                 | <u>+</u> 3               |                    | %     | 8-pin devices      |  |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                      |                    | ns    |                    |  |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                        |                    | mV    |                    |  |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V     |                    |  |

# General Purpose I/O Port Input Data Sample Timing

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

PS024314-0308 Electrical Characteristics

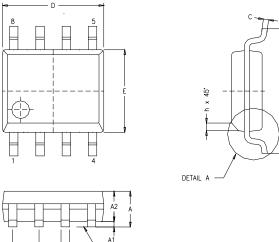

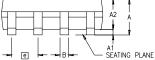

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

| SYMBOL | MILLI | METER | INCH  |       |  |

|--------|-------|-------|-------|-------|--|

| SIMBUL | MIN   | MAX   | MIN   | MAX   |  |

| Α      | 1.55  | 1.73  | 0.061 | 0.068 |  |

| A1     | 0.10  | 0.25  | 0.004 | 0.010 |  |

| A2     | 1.40  | 1.55  | 0.055 | 0.061 |  |

| В      | 0.36  | 0.48  | 0.014 | 0.019 |  |

| С      | 0.18  | 0.25  | 0.007 | 0.010 |  |

| D      | 4.80  | 4.98  | 0.189 | 0.196 |  |

| E      | 3.81  | 3.99  | 0.150 | 0.157 |  |

| е      | 1.27  | BSC   | .050  | BSC   |  |

| Н      | 5.84  | 6.15  | 0.230 | 0.242 |  |

| h      | 0.25  | 0.40  | 0.010 | 0.016 |  |

| L      | 0.46  | 0.81  | 0.018 | 0.032 |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

PS024314-0308 Packaging

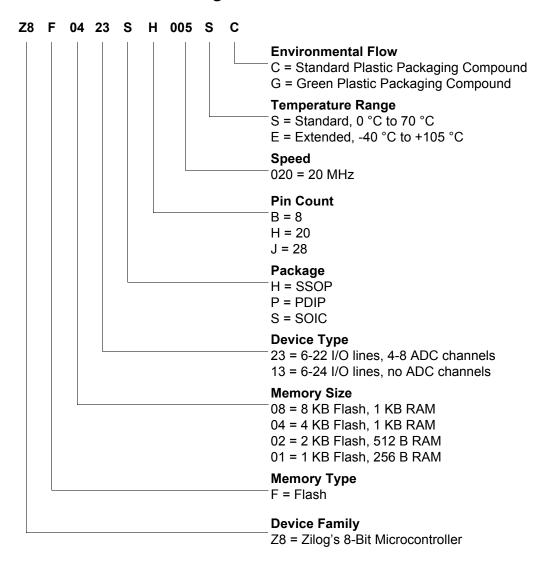

### **Part Number Suffix Designations**

PS024314-0308 Ordering Information

| Index                                                   | ANDX 177                                                       |

|---------------------------------------------------------|----------------------------------------------------------------|

|                                                         | arithmetic instructions 175                                    |

|                                                         | assembly language programming 171 assembly language syntax 172 |

| Symbols                                                 | assembly language symax 172                                    |

| # 174                                                   |                                                                |

| % 174                                                   | В                                                              |

| @ 174                                                   | B 174                                                          |

|                                                         | b 173                                                          |

|                                                         | baud rate generator, UART 103                                  |

| Numerics                                                | BCLR 176                                                       |

| 10-bit ADC 4                                            | binary number suffix 174                                       |

| 40-lead plastic dual-inline package 214, 215            | BIT 176                                                        |

|                                                         | bit 173<br>clear 176                                           |

| Α                                                       | manipulation instructions 176                                  |

|                                                         | set 176                                                        |

| absolute maximum ratings 193 AC characteristics 197     | set or clear 176                                               |

| ADC 175                                                 | swap 176                                                       |

| architecture 117                                        | test and jump 178                                              |

| automatic power-down 118                                | test and jump if non-zero 178                                  |

| block diagram 118                                       | test and jump if zero 178                                      |

| continuous conversion 120                               | bit jump and test if non-zero 178                              |

| control register 122, 124                               | bit swap 178                                                   |

| control register definitions 122                        | block diagram 3 block transfer instructions 176                |

| data high byte register 124                             | BRK 178                                                        |

| data low bits register 125                              | BSET 176                                                       |

| electrical characteristics and timing 201 operation 118 | BSWAP 176, 178                                                 |

| single-shot conversion 119                              | BTJ 178                                                        |

| ADCCTL register 122, 124                                | BTJNZ 178                                                      |

| ADCDH register 124                                      | BTJZ 178                                                       |

| ADCDL register 125                                      |                                                                |

| ADCX 175                                                | C                                                              |

| ADD 175                                                 | C                                                              |

| add - extended addressing 175                           | CALL procedure 178                                             |

| add with carry 175                                      | CAPTURE mode 84, 85 CAPTURE/COMPARE mode 85                    |

| add with carry - extended addressing 175                | cc 173                                                         |

| additional symbols 174 address space 13                 | CCF 176                                                        |

| ADDX 175                                                | characteristics, electrical 193                                |

| analog signals 10                                       | clear 177                                                      |

| analog-to-digital converter (ADC) 117                   | CLR 177                                                        |

| AND 177                                                 | COM 177                                                        |

PS024314-0308 Index