# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0413sh005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Information Area                                       | . 130 |

|--------------------------------------------------------------|-------|

| Operation                                                    | . 131 |

| Flash Operation Timing Using the Flash Frequency Registers   |       |

| Flash Code Protection Against External Access                |       |

| Flash Code Protection Against Accidental Program and Erasure |       |

| Byte Programming                                             |       |

| Page Erase                                                   |       |

| Mass Erase                                                   |       |

| Flash Controller Bypass                                      |       |

| Flash Controller Behavior in DEBUG Mode                      |       |

| Flash Control Register Definitions                           |       |

| Flash Control Register                                       |       |

| Flash Status Register                                        |       |

| Flash Page Select Register   Flash Sector Protect Register   |       |

| Flash Frequency High and Low Byte Registers                  |       |

|                                                              |       |

| Flash Option Bits                                            |       |

| Operation                                                    |       |

| Option Bit Configuration By Reset                            |       |

| Option Bit Types                                             |       |

| Reading the Flash Information Page                           |       |

| Flash Option Bit Control Register Definitions                |       |

| Trim Bit Address Register                                    | -     |

| Trim Bit Data Register                                       |       |

| Flash Option Bit Address Space                               |       |

| Flash Program Memory Address 0000H                           |       |

| Flash Program Memory Address 0001H                           |       |

| Trim Bit Address Space                                       |       |

| Trim Bit Address 0000H—Reserved                              |       |

| Trim Bit Address 0001H—Reserved                              |       |

| Trim Bit Address 0002H                                       |       |

| Trim Bit Address 00031—Reserved                              |       |

|                                                              |       |

| Zilog Calibration Data                                       |       |

| Serialization Data                                           |       |

| Randomized Lot Identifier                                    |       |

|                                                              |       |

| On-Chip Debugger                                             |       |

| Architecture                                                 | . 151 |

|                                                              |       |

#### viii

|                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |  |

|-----------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|--|

| Reset<br>Type         | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |  |

| System<br>Reset       | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL and OSC_CTL<br>registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |  |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

## **Reset Sources**

Table 10 lists the possible sources of a System Reset.

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

|          | •                                   | •                                                                          |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer on page 87)                             |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          |                                     |                                                                            |

## Table 33. Trap and Interrupt Vectors in Order of Priority

Caution:

To avoid missing interrupts, use the following coding style to clear bits in the Interrupt Request 0 register:

#### Good coding style that avoids lost interrupt requests: ANDX IRQ0, MASK

## **Software Interrupt Assertion**

Program code generates interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** The following coding style used to generate software interrupts by setting bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests: LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

Good coding style that avoids lost interrupt requests: ORX IRQ0, MASK

## Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

**Caution:** To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

> CLEARWDT: LDX r0, RSTSTAT ; read reset status register to clear wdt bit BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6   | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|-----|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0   | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          |     |     | FC           | 0H    |          |          |      |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period. If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

#### PWM Dual Output Mode

In PWM DUAL OUTPUT mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM Dual Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM Dual Output mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register

- Set the prescale value

timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Follow the steps below to configure a timer for COMPARE mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for Compare mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In COMPARE mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

COMPARE Mode Time (s) = (Compare Value – Start Value) × Prescale System Clock Frequency (Hz)

#### GATED Mode

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer Reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

# **Timer Control Register Definitions**

## Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 49 and Table 50) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |

|-------|-----|-----|-----|-------|------|-----|-----|-----|--|

| FIELD |     | TH  |     |       |      |     |     |     |  |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |  |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |

| ADDR  |     |     |     | F00H, | F08H |     |     |     |  |

Table 49. Timer 0–1 High Byte Register (TxH)

## Table 50. Timer 0–1 Low Byte Register (TxL)

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |  |

|-------|-----|-----|-----|-------|------|-----|-----|-----|--|--|

| FIELD |     | TL  |     |       |      |     |     |     |  |  |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 1   |  |  |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |  |

| ADDR  |     |     |     | F01H, | F09H |     |     |     |  |  |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value

## **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 51 and Table 52) store a 16-bit Reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

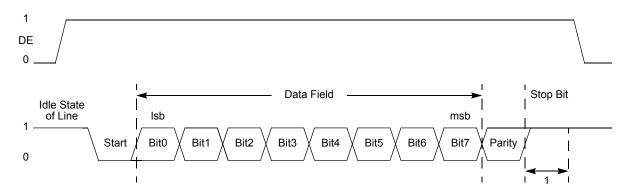

## **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

## **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7 | 6   | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|-----|---|----|----|---|---|---|--|

| FIELD |   | TXD |   |    |    |   |   |   |  |

| RESET | Х | Х   | Х | Х  | Х  | Х | Х | Х |  |

| R/W   | W | W   | W | W  | W  | W | W | W |  |

| ADDR  |   |     |   | F4 | 0H |   |   |   |  |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

Reserved—R/W bits must be 0 during writes; 0 when read.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame

1 = The current byte is the first data byte of a new frame

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 66 and Table 67) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Table 66. UART Control 0 Register (U0CTL0)

| BITS  | 7   | 6   | 5    | 4   | 3    | 2    | 1    | 0        |

|-------|-----|-----|------|-----|------|------|------|----------|

| FIELD | TEN | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN     |

| RESET | 0   | 0   | 0    | 0   | 0    | 0    | 0    | 0        |

| R/W   | R/W | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W      |

| ADDR  |     |     |      | F4  | 2H   |      |      | <u>.</u> |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled

1 = Transmitter enabled

REN—Receive Enable

This bit enables or disables the receiver.

- 0 =Receiver disabled

- 1 =Receiver enabled

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |  |

|-------|---------|------|---------|------|-------|--------|--------|------|--|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |  |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |

| ADDR  |         | F43H |         |      |       |        |        |      |  |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

## ADC Data Low Bits Register

The ADC Data Low Byte register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 75. ADC Data Low Bits Register (ADCD\_L)

| BITS  | 7 | 6     | 5 | 4  | 3        | 2 | 1 | 0 |  |

|-------|---|-------|---|----|----------|---|---|---|--|

| FIELD |   | ADCDL |   |    | Reserved |   |   |   |  |

| RESET | Х | Х     | Х | Х  | Х        | Х | Х | Х |  |

| R/W   | R | R     | R | R  | R        | R | R | R |  |

| ADDR  |   |       |   | F7 | 3H       |   |   |   |  |

ADCDL—ADC Data Low Bits

These bits are the least significant three bits of the 11-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Undefined when read

OVF—Overflow Status

0= An overflow did not occur in the digital filter for the current sample

1= An overflow did occur in the digital filter for the current sample

Reserved—0 when read

FSTAT—Flash Controller Status 000000 = Flash Controller locked 000001 = First unlock command received (73H written) 000010 = Second unlock command received (8CH written) 000011 = Flash Controller unlocked 000100 = Sector protect register selected 001xxx = Program operation in progress 010xxx = Page erase operation in progress 100xxx = Mass erase operation in progress

## Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6   | 5    | 4   | 3   | 2   | 1   | 0   |

|-------|---------|-----|------|-----|-----|-----|-----|-----|

| FIELD | INFO_EN |     | PAGE |     |     |     |     |     |

| RESET | 0       | 0   | 0    | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W     | R/W | R/W  | R/W | R/W | R/W | R/W | R/W |

| ADDR  |         |     |      | FF  | 9H  |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0. configurations. The information contained here is lost when page 0 of the Program Memory is erased.

#### **Trim Option Bits**

The trim option bits are contained in the information page of the Flash memory. These bits are factory programmed values required to optimize the operation of onboard analog circuitry and cannot be permanently altered. Program Memory may be erased without endangering these values. It is possible to alter working values of these bits by accessing the Trim Bit Address and Data Registers, but these working values are lost after a power loss or any other reset event.

There are 32 bytes of trim data. To modify one of these values the user code must first write a value between 00H and 1FH into the Trim Bit Address Register. The next write to the Trim Bit Data register changes the working value of the target trim data byte.

Reading the trim data requires the user code to write a value between 00H and 1FH into the Trim Bit Address Register. The next read from the Trim Bit Data register returns the working value of the target trim data byte.

The trim address range is from information address 20-3F only. The remainder of the information page is not accessible through the trim bit address and data registers.

#### **Calibration Option Bits**

The calibration option bits are also contained in the information page. These bits are factory programmed values intended for use in software correcting the device's analog performance. To read these values, the user code must employ the LDC instruction to access the information area of the address space as defined in Flash Information Area on page 15

#### **Serialization Bits**

As an optional feature, Zilog<sup>®</sup> is able to provide factory-programmed serialization. For serialized products, the individual devices are programmed with unique serial numbers. These serial numbers are binary values, four bytes in length. The numbers increase in size with each device, but gaps in the serial sequence may exist.

These serial numbers are stored in the Flash information page (for more details, see Reading the Flash Information Page on page 143 and Serialization Data on page 148) and are unaffected by mass erasure of the device's Flash memory.

#### **Randomized Lot Identification Bits**

As an optional feature, Zilog is able to provide a factory-programmed random lot identifier. With this feature, all devices in a given production lot are programmed with the same random number. This random number is uniquely regenerated for each successive production lot and is not likely to be repeated.

Note:

datastreams, the maximum recommended baud rate is the system clock frequency divided by eight. The maximum possible baud rate for asynchronous datastreams is the system clock frequency divided by four, but this theoretical maximum is possible only for low noise designs with clean signals. Table 98 lists minimum and recommended maximum baud rates for sample crystal frequencies.

| System Clock<br>Frequency (MHz) | Recommended<br>Maximum Baud<br>Rate (kbps) | Recommended<br>Standard PC<br>Baud Rate (bps) | Minimum Baud<br>Rate (kbps) |  |  |

|---------------------------------|--------------------------------------------|-----------------------------------------------|-----------------------------|--|--|

| 5.5296                          | 1382.4                                     | 691,200                                       | 1.08                        |  |  |

| 0.032768 (32 kHz)               | 4.096                                      | 2400                                          | 0.064                       |  |  |

#### Table 98. OCD Baud-Rate Limits

If the OCD receives a Serial Break (nine or more continuous bits Low) the auto-baud detector/generator resets. Reconfigure the auto-baud detector/generator by sending 80H.

### **OCD Serial Errors**

The OCD detects any of the following error conditions on the DBG pin:

- Serial Break (a minimum of nine continuous bits Low)

- Framing Error (received Stop bit is Low)

- Transmit Collision (OCD and host simultaneous transmission detected by the OCD)

When the OCD detects one of these errors, it aborts any command currently in progress, transmits a four character long Serial Break back to the host, and resets the auto-baud detector/generator. A Framing Error or Transmit Collision may be caused by the host sending a Serial Break to the OCD. Because of the open-drain nature of the interface, returning a Serial Break break back to the host only extends the length of the Serial Break if the host releases the Serial Break early.

The host transmits a Serial Break on the DBG pin when first connecting to the Z8 Encore! XP F0823 Series devices or when recovering from an error. A Serial Break from the host resets the auto-baud generator/detector but does not reset the OCD Control register. A Serial Break leaves the device in DEBUG mode if that is the current mode. The OCD is held in Reset until the end of the Serial Break when the DBG pin returns High. Because of the open-drain nature of the DBG pin, the host sends a Serial Break to the OCD even if the OCD is transmitting a character.

| Table 114. Rotate and Shift Instructions | (Continued) |

|------------------------------------------|-------------|

|------------------------------------------|-------------|

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SRA      | dst      | Shift Right Arithmetic |

| SRL      | dst      | Shift Right Logical    |

| SWAP     | dst      | Swap Nibbles           |

## eZ8 CPU Instruction Summary

Table 115 summarizes the eZ8 CPU instructions. The table identifies the addressing modes employed by the instruction, the effect upon the Flags register, the number of CPU clock cycles required for the instruction fetch, and the number of CPU clock cycles required for the instruction.

| Assembly        |                                                              | Addre      | Address Mode |                      | Flags |              |   |   |   | - Fetch | Instr. |   |

|-----------------|--------------------------------------------------------------|------------|--------------|----------------------|-------|--------------|---|---|---|---------|--------|---|

| Mnemonic        | Symbolic Operation                                           | dst        | src          | – Opcode(s)<br>(Hex) | С     | Ζ            | S | v | D | Н       | Cycles |   |

| ADC dst, src    | $dst \gets dst + src + C$                                    | r          | r            | 12                   | *     | *            | * | * | 0 | *       | 2      | 3 |

|                 |                                                              | r          | lr           | 13                   | _     |              |   |   |   |         | 2      | 4 |

|                 |                                                              | R          | R            | 14                   | _     |              |   |   |   |         | 3      | 3 |

|                 |                                                              | R          | IR           | 15                   | _     |              |   |   |   |         | 3      | 4 |

|                 |                                                              | R          | IM           | 16                   | _     |              |   |   |   |         | 3      | 3 |

|                 |                                                              | IR         | IM           | 17                   | _     |              |   |   |   |         | 3      | 4 |

| ADCX dst, src   | $dst \gets dst + src + C$                                    | ER         | ER           | 18                   | *     | *            | * | * | 0 | *       | 4      | 3 |

|                 |                                                              | ER         | IM           | 19                   | _     |              |   |   |   |         | 4      | 3 |

| ADD dst, src    | $dst \gets dst + src$                                        | r          | r            | 02                   | *     | *            | * | * | 0 | *       | 2      | 3 |

|                 |                                                              | r          | lr           | 03                   | _     |              |   |   |   |         | 2      | 4 |

|                 |                                                              | R          | R            | 04                   | _     |              |   |   |   |         | 3      | 3 |

|                 |                                                              | R          | IR           | 05                   | _     |              |   |   |   |         | 3      | 4 |

|                 |                                                              | R          | IM           | 06                   | _     |              |   |   |   |         | 3      | 3 |

|                 |                                                              | IR         | IM           | 07                   | _     |              |   |   |   |         | 3      | 4 |

| ADDX dst, src   | $dst \gets dst + src$                                        | ER         | ER           | 08                   | *     | *            | * | * | 0 | *       | 4      | 3 |

|                 |                                                              | ER         | IM           | 09                   | _     |              |   |   |   |         | 4      | 3 |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resu | It of the o  | peration.            |       | = Re<br>= Se |   |   | 0 |         |        |   |

#### Table 115. eZ8 CPU Instruction Summary

# **On-Chip Peripheral AC and DC Electrical Characteristics**

## Table 122. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C       |          |                                                                                                       |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|--------------|----------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum      | Units    | Conditions                                                                                            |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70         | V        | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65         | V        | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75           | mV       |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | _                  | V <sub>SS</sub>      | -            | V        |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -            | μs       | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                                                             |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | _            | μs       | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100          | ms       |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |              | ns       | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

|                   | he typical column is from char are not tested in production.                                                   | acterization       | at 3.3 V and         | 30 °C. These | values a | re provided for design guidance                                                                       |  |

199

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  |        | Notes                                                                                                                                                             |  |  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  |                                                                                                                                                                   |  |  |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |  |  |

| Flash Byte Program Time                       | 20        | -                                    | 40      | μs     |                                                                                                                                                                   |  |  |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |  |  |

| Flash Mass Erase Time                         | 200       | -                                    | _       | ms     |                                                                                                                                                                   |  |  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                   |  |  |

| Flash Row Program Time                        | _         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |  |

| Data Retention                                | 100       | _                                    | -       | years  | 25 °C                                                                                                                                                             |  |  |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |  |  |

## Table 123. Flash Memory Electrical Characteristics and Timing

### Table 124. Watchdog Timer Electrical Characteristics and Timing

|                     |                          | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |    |             |            |                                                                        |

|---------------------|--------------------------|-----------------------------------------------------------------------------------------------------|----|-------------|------------|------------------------------------------------------------------------|

| Symbol              | Parameter                | Minimum Typical Maximum L                                                                           |    | Units       | Conditions |                                                                        |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                                                                                                     | 10 |             | kHz        |                                                                        |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                                                                                                     |    | <u>+</u> 50 | %          |                                                                        |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98                                                                                                | 1  | 1.02        | S          | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C                     |

|                     |                          | 0.70                                                                                                | 1  | 1.30        | S          | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |

|                     |                          | 0.50                                                                                                | 1  | 1.50        | S          | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |