Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423hj005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **Warning:** DO NOT USE IN LIFE SUPPORT

#### LIFE SUPPORT POLICY

ZILOG'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS PRIOR WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF ZILOG CORPORATION.

#### As used herein

Life support devices or systems are devices which (a) are intended for surgical implant into the body, or (b) support or sustain life and whose failure to perform when properly used in accordance with instructions for use provided in the labeling can be reasonably expected to result in a significant injury to the user. A critical component is any component in a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system or to affect its safety or effectiveness.

#### **Document Disclaimer**

©2008 by Zilog, Inc. All rights reserved. Information in this publication concerning the devices, applications, or technology described is intended to suggest possible uses and may be superseded. ZILOG, INC. DOES NOT ASSUME LIABILITY FOR OR PROVIDE A REPRESENTATION OF ACCURACY OF THE INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED IN THIS DOCUMENT. ZILOG ALSO DOES NOT ASSUME LIABILITY FOR INTELLECTUAL PROPERTY INFRINGEMENT RELATED IN ANY MANNER TO USE OF INFORMATION, DEVICES, OR TECHNOLOGY DESCRIBED HEREIN OR OTHERWISE. The information contained within this document has been verified according to the general principles of electrical and mechanical engineering.

Z8, Z8 Encore!, Z8 Encore! XP, Z8 Encore! MC, Crimzon, eZ80, and ZNEO are trademarks or registered trademarks of Zilog, Inc. All other product or service names are the property of their respective owners.

| Reading the Timer Count Values                           |     |

|----------------------------------------------------------|-----|

| Timer Control Register Definitions                       | 80  |

| Timer 0–1 High and Low Byte Registers                    | 80  |

| Timer Reload High and Low Byte Registers                 | 80  |

| Timer 0-1 PWM High and Low Byte Registers                | 81  |

| Timer 0–1 Control Registers                              | 82  |

| Watchdog Timer                                           | 87  |

| Operation                                                | 87  |

| Watchdog Timer Refresh                                   |     |

| Watchdog Timer Time-Out Response                         | 88  |

| Watchdog Timer Reload Unlock Sequence                    |     |

| Watchdog Timer Control Register Definitions              | 89  |

| Watchdog Timer Control Register                          |     |

| Watchdog Timer Reload Upper, High and Low Byte Registers |     |

| Universal Asynchronous Receiver/Transmitter              | 93  |

| Architecture                                             | 93  |

| Operation                                                | 94  |

|                                                          | ~ 4 |

Shared Interrupt Select Register ..... 64 Interrupt Control Register ..... 64

#### vi

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

Note:

\*Analog input alternate functions (ANA) are not available on the Z8F0x13 devices.

## **Signal Descriptions**

Table 3 lists the Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series signals. To determine the signals available for the specific package styles, see Pin Configurations on page 7.

#### Table 3. Signal Descriptions

| Signal Mnemonic                                       | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C                                   | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                               | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                               | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                               | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| Note: PB6 and PB7 are<br>replaced by AV <sub>DI</sub> |         | /ailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                      |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                  | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                  | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                  | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                    | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                                |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                           | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT                                           | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                             | I       | Timer Input 0–1. These signals are used as the <u>capture</u> , gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                |

| Comparator                                            |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                             | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                  | 0       | Comparator Output. This is the output of the comparator.                                                                                                                                                                                                                                                |

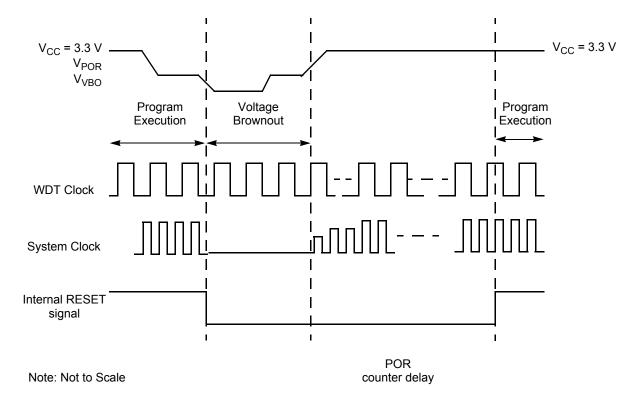

Figure 6. Voltage Brownout Reset Operation

The POR level is greater than the VBO level by the specified hysteresis value. This ensures that the device undergoes a POR after recovering from a VBO condition.

## Watchdog Timer Reset

If the device is in NORMAL or STOP mode, the Watchdog Timer can initiate a System Reset at time-out if the WDT\_RES Flash Option Bit is programmed to 1. This is the unprogrammed state of the WDT\_RES Flash Option Bit. If the bit is programmed to 0, it configures the Watchdog Timer to cause an interrupt, not a System Reset, at time-out.

The WDT status bit in the WDT Control register is set to signify that the reset was initiated by the Watchdog Timer.

## **External Reset Input**

The  $\overline{\text{RESET}}$  pin has a Schmitt-Triggered input and an internal pull-up resistor. Once the  $\overline{\text{RESET}}$  pin is asserted for a minimum of four system clock cycles, the device progresses through the System Reset sequence. Because of the possible asynchronicity of the system

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

## **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

63

#### Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[ | x] Priority | Description |

|------------|----------|-------------|-------------|

| 1          | 1        | Level 3     | High        |

where x indicates the register bits from 0–7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|-----|------|-------|-----|-------|-------|-------|-------|

| FIELD |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |     |      |       | FC  | 7H    |       |       |       |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|-----|------|-------|-----|-------|-------|-------|-------|

| FIELD |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |     |      |       | FC  | 8H    |       |       |       |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| BITS  | 7    | 6 | 5 | 4  | 3        | 2 | 1 | 0 |

|-------|------|---|---|----|----------|---|---|---|

| FIELD | IRQE |   |   |    | Reserved |   |   |   |

| RESET | 0    | 0 | 0 | 0  | 0        | 0 | 0 | 0 |

| R/W   | R/W  | R | R | R  | R        | R | R | R |

| ADDR  |      |   |   | FC | FH       |   |   |   |

## Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$$

#### COMPARE Mode

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the

#### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

#### **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1001 = Divide by 2

## Table 59. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS     | 7              | 6            | 5             | 4              | 3             | 2            | 1    | 0    |

|----------|----------------|--------------|---------------|----------------|---------------|--------------|------|------|

| FIELD    |                |              |               | WE             | UTU           |              |      |      |

| RESET    |                |              |               | 00             | )H            |              |      |      |

| R/W      | R/W*           | R/W*         | R/W*          | R/W*           | R/W*          | R/W*         | R/W* | R/W* |

| ADDR     |                |              |               | FF             | 1H            |              |      |      |

| R/W*—Rea | ad returns the | e current WD | T count value | . Write sets t | he appropriat | e Reload Val | ue.  |      |

WDTU—WDT Reload Upper Byte Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

## Table 60. Watchdog Timer Reload High Byte Register (WDTH)

| BITS     | 7              | 6           | 5            | 4              | 3             | 2            | 1    | 0    |  |  |

|----------|----------------|-------------|--------------|----------------|---------------|--------------|------|------|--|--|

| FIELD    |                | WDTH        |              |                |               |              |      |      |  |  |

| RESET    |                | 04H         |              |                |               |              |      |      |  |  |

| R/W      | R/W*           | R/W*        | R/W*         | R/W*           | R/W*          | R/W*         | R/W* | R/W* |  |  |

| ADDR     |                |             |              | FF             | 2H            |              |      |      |  |  |

| R/W*—Rea | ad returns the | current WDT | count value. | Write sets the | e appropriate | Reload Value | 9.   |      |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

### Table 61. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS     | 7             | 6             | 5            | 4             | 3             | 2           | 1    | 0    |  |  |

|----------|---------------|---------------|--------------|---------------|---------------|-------------|------|------|--|--|

| FIELD    |               | WDTL          |              |               |               |             |      |      |  |  |

| RESET    |               | 00H           |              |               |               |             |      |      |  |  |

| R/W      | R/W*          | R/W*          | R/W*         | R/W*          | R/W*          | R/W*        | R/W* | R/W* |  |  |

| ADDR     | FF3H          |               |              |               |               |             |      |      |  |  |

| R/W*—Rea | d returns the | e current WD1 | count value. | Write sets th | e appropriate | Reload Valu | e.   |      |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

bits of resolution are lost because of a rounding error. As a result, the final value is an 11- bit number.

### Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

119

## ADC Data Low Bits Register

The ADC Data Low Byte register contains the lower bits of the ADC output as well as an overflow status bit. The output is a 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data Low Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 75. ADC Data Low Bits Register (ADCD\_L)

| BITS  | 7 | 6     | 5 | 4  | 3    | 2     | 1 | 0   |

|-------|---|-------|---|----|------|-------|---|-----|

| FIELD |   | ADCDL |   |    | Rese | erved |   | OVF |

| RESET | Х | Х     | Х | Х  | Х    | Х     | Х | Х   |

| R/W   | R | R     | R | R  | R    | R     | R | R   |

| ADDR  |   |       |   | F7 | 3H   |       |   |     |

ADCDL—ADC Data Low Bits

These bits are the least significant three bits of the 11-bits of the ADC output. These bits are undefined after a Reset.

Reserved—Undefined when read

OVF—Overflow Status

0= An overflow did not occur in the digital filter for the current sample

1= An overflow did occur in the digital filter for the current sample

| Abbreviation | Description                           | Abbreviation                                   | Description            |

|--------------|---------------------------------------|------------------------------------------------|------------------------|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |

| СС           | Condition code                        | р                                              | Polarity (0 or 1)      |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |

| DA           | Destination address                   | R                                              | 8-bit register         |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |

| Ir           | Indirect Working Register             | RA                                             | Relative               |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |

## Table 116. Opcode Map Abbreviations

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

|   |                           |                            |                              |                                |                             |                             | Lo                           | ower Nil                       | oble (He                      | x)                             |                            |                          |                    |                           |                  |                          |

|---|---------------------------|----------------------------|------------------------------|--------------------------------|-----------------------------|-----------------------------|------------------------------|--------------------------------|-------------------------------|--------------------------------|----------------------------|--------------------------|--------------------|---------------------------|------------------|--------------------------|

|   | 0                         | 1                          | 2                            | 3                              | 4                           | 5                           | 6                            | 7                              | 8                             | 9                              | А                          | В                        | С                  | D                         | Е                | F                        |

| 0 | 1.1<br>BRK                | 2.2<br>SRP<br>IM           | 2.3<br><b>ADD</b><br>r1,r2   | 2.4<br>ADD<br>r1,lr2           | 3.3<br><b>ADD</b><br>R2,R1  | 3.4<br>ADD<br>IR2,R1        | 3.3<br><b>ADD</b><br>R1,IM   | 3.4<br>ADD<br>IR1,IM           | 4.3<br>ADDX<br>ER2,ER1        | 4.3<br>ADDX<br>IM,ER1          | 2.3<br><b>DJNZ</b><br>r1,X | 2.2<br><b>JR</b><br>cc,X | 2.2<br>LD<br>r1,IM | 3.2<br><b>JP</b><br>cc,DA | 1.2<br>INC<br>r1 | 1.2<br>NOP               |

| 1 | 2.2<br><b>RLC</b><br>R1   | 2.3<br><b>RLC</b><br>IR1   | 2.3<br>ADC<br>r1,r2          | 2.4<br>ADC<br>r1,lr2           | 3.3<br>ADC<br>R2,R1         | 3.4<br>ADC<br>IR2,R1        | 3.3<br><b>ADC</b><br>R1,IM   | 3.4<br>ADC<br>IR1,IM           | 4.3<br>ADCX<br>ER2,ER1        | 4.3<br>ADCX<br>IM,ER1          |                            |                          |                    |                           |                  | See 2nd<br>Opcode<br>Map |

| 2 | 2.2<br>INC<br>R1          | 2.3<br>INC<br>IR1          | 2.3<br><b>SUB</b><br>r1,r2   | 2.4<br>SUB<br>r1,lr2           | 3.3<br><b>SUB</b><br>R2,R1  | 3.4<br>SUB<br>IR2,R1        | 3.3<br><b>SUB</b><br>R1,IM   | 3.4<br><b>SUB</b><br>IR1,IM    | 4.3<br>SUBX<br>ER2,ER1        | 4.3<br><b>SUBX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1, 2<br>ATM              |

| 3 | 2.2<br>DEC<br>R1          | 2.3<br><b>DEC</b><br>IR1   | 2.3<br><b>SBC</b><br>r1,r2   | 2.4<br><b>SBC</b><br>r1,lr2    | 3.3<br><b>SBC</b><br>R2,R1  | 3.4<br><b>SBC</b><br>IR2,R1 | 3.3<br><b>SBC</b><br>R1,IM   | 3.4<br>SBC<br>IR1,IM           | 4.3<br><b>SBCX</b><br>ER2,ER1 | 4.3<br><b>SBCX</b><br>IM,ER1   |                            |                          |                    |                           |                  |                          |

| 4 | 2.2<br><b>DA</b><br>R1    | 2.3<br><b>DA</b><br>IR1    | 2.3<br><b>OR</b><br>r1,r2    | 2.4<br><b>OR</b><br>r1,lr2     | 3.3<br><b>OR</b><br>R2,R1   | 3.4<br><b>OR</b><br>IR2,R1  | 3.3<br><b>OR</b><br>R1,IM    | 3.4<br><b>OR</b><br>IR1,IM     | 4.3<br><b>ORX</b><br>ER2,ER1  | 4.3<br><b>ORX</b><br>IM,ER1    |                            |                          |                    |                           |                  |                          |

| 5 | 2.2<br><b>POP</b><br>R1   | 2.3<br><b>POP</b><br>IR1   | 2.3<br><b>AND</b><br>r1,r2   | 2.4<br><b>AND</b><br>r1,lr2    | 3.3<br><b>AND</b><br>R2,R1  | 3.4<br><b>AND</b><br>IR2,R1 | 3.3<br><b>AND</b><br>R1,IM   | 3.4<br><b>AND</b><br>IR1,IM    | 4.3<br>ANDX<br>ER2,ER1        | 4.3<br>ANDX<br>IM,ER1          |                            |                          |                    |                           |                  | 1.2<br>WDT               |

| 6 | 2.2<br><b>COM</b><br>R1   | 2.3<br>COM<br>IR1          | 2.3<br><b>TCM</b><br>r1,r2   | 2.4<br><b>TCM</b><br>r1,lr2    | 3.3<br><b>TCM</b><br>R2,R1  | 3.4<br><b>TCM</b><br>IR2,R1 | 3.3<br><b>TCM</b><br>R1,IM   | 3.4<br><b>TCM</b><br>IR1,IM    | 4.3<br><b>TCMX</b><br>ER2,ER1 | 4.3<br><b>TCMX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.2<br>STOP              |

| 7 | 2.2<br>PUSH<br>R2         | 2.3<br><b>PUSH</b><br>IR2  | 2.3<br><b>TM</b><br>r1,r2    | 2.4<br><b>TM</b><br>r1,lr2     | 3.3<br><b>TM</b><br>R2,R1   | 3.4<br><b>TM</b><br>IR2,R1  | 3.3<br><b>TM</b><br>R1,IM    | 3.4<br><b>TM</b><br>IR1,IM     | 4.3<br><b>TMX</b><br>ER2,ER1  | 4.3<br><b>TMX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>HALT              |

| 8 | 2.5<br><b>DECW</b><br>RR1 | 2.6<br><b>DECW</b><br>IRR1 | 2.5<br><b>LDE</b><br>r1,Irr2 | 2.9<br><b>LDEI</b><br>Ir1,Irr2 | 3.2<br><b>LDX</b><br>r1,ER2 | 3.3<br>LDX<br>Ir1,ER2       | 3.4<br>LDX<br>IRR2,R1        | 3.5<br><b>LDX</b><br>IRR2,IR1  | 3.4<br><b>LDX</b><br>r1,rr2,X | 3.4<br><b>LDX</b><br>rr1,r2,X  |                            |                          |                    |                           |                  | 1.2<br>DI                |

| 9 | 2.2<br><b>RL</b><br>R1    | 2.3<br><b>RL</b><br>IR1    | 2.5<br><b>LDE</b><br>r2,Irr1 | 2.9<br><b>LDEI</b><br>Ir2,Irr1 | 3.2<br>LDX<br>r2,ER1        | 3.3<br>LDX<br>Ir2,ER1       | 3.4<br><b>LDX</b><br>R2,IRR1 | 3.5<br><b>LDX</b><br>IR2,IRR1  | 3.3<br><b>LEA</b><br>r1,r2,X  | 3.5<br><b>LEA</b><br>rr1,rr2,X |                            |                          |                    |                           |                  | 1.2<br>El                |

| А | 2.5<br>INCW<br>RR1        | 2.6<br>INCW<br>IRR1        | 2.3<br><b>CP</b><br>r1,r2    | 2.4<br><b>CP</b><br>r1,lr2     | 3.3<br><b>CP</b><br>R2,R1   | 3.4<br><b>CP</b><br>IR2,R1  | 3.3<br><b>CP</b><br>R1,IM    | 3.4<br><b>CP</b><br>IR1,IM     | 4.3<br><b>CPX</b><br>ER2,ER1  | 4.3<br><b>CPX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.4<br>RET               |

| в | 2.2<br><b>CLR</b><br>R1   | 2.3<br><b>CLR</b><br>IR1   | 2.3<br><b>XOR</b><br>r1,r2   | 2.4<br><b>XOR</b><br>r1,lr2    | 3.3<br><b>XOR</b><br>R2,R1  | 3.4<br><b>XOR</b><br>IR2,R1 | 3.3<br><b>XOR</b><br>R1,IM   | 3.4<br><b>XOR</b><br>IR1,IM    | 4.3<br><b>XORX</b><br>ER2,ER1 | 4.3<br><b>XORX</b><br>IM,ER1   |                            |                          |                    |                           |                  | 1.5<br>IRET              |

| с | 2.2<br><b>RRC</b><br>R1   | 2.3<br><b>RRC</b><br>IR1   | 2.5<br><b>LDC</b><br>r1,Irr2 | 2.9<br>LDCI<br>Ir1,Irr2        | 2.3<br><b>JP</b><br>IRR1    | 2.9<br>LDC<br>lr1,lrr2      |                              | 3.4<br><b>LD</b><br>r1,r2,X    | 3.2<br>PUSHX<br>ER2           |                                |                            |                          |                    |                           |                  | 1.2<br>RCF               |

| D | 2.2<br><b>SRA</b><br>R1   | 2.3<br><b>SRA</b><br>IR1   | 2.5<br><b>LDC</b><br>r2,Irr1 | 2.9<br><b>LDCI</b><br>lr2,lrr1 | 2.6<br>CALL<br>IRR1         | 2.2<br><b>BSWAP</b><br>R1   | 3.3<br>CALL<br>DA            | 3.4<br><b>LD</b><br>r2,r1,X    | 3.2<br><b>POPX</b><br>ER1     |                                |                            |                          |                    |                           |                  | 1.2<br>SCF               |

| E | 2.2<br><b>RR</b><br>R1    | 2.3<br><b>RR</b><br>IR1    | 2.2<br><b>BIT</b><br>p,b,r1  | 2.3<br><b>LD</b><br>r1,lr2     | 3.2<br><b>LD</b><br>R2,R1   | 3.3<br><b>LD</b><br>IR2,R1  | 3.2<br><b>LD</b><br>R1,IM    | 3.3<br><b>LD</b><br>IR1,IM     | 4.2<br><b>LDX</b><br>ER2,ER1  | 4.2<br><b>LDX</b><br>IM,ER1    |                            |                          |                    |                           |                  | 1.2<br>CCF               |

| F | 2.2<br>SWAP<br>R1         | 2.3<br><b>SWAP</b><br>IR1  | 2.6<br>TRAP<br>Vector        | 2.3<br><b>LD</b><br>lr1,r2     | 2.8<br><b>MULT</b><br>RR1   | 3.3<br><b>LD</b><br>R2,IR1  | 3.3<br><b>BTJ</b>            | 3.4<br><b>BTJ</b><br>p,b,lr1,X |                               |                                | V                          | V                        | V                  | ┥┥                        | V                |                          |

Figure 27. First Opcode Map

190

Upper Nibble (Hex)

#### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|        |                     | T <sub>A</sub> = | = 3.0 V to<br>0 °C to +<br>otherwise | 70 °C           |       |                                      |  |

|--------|---------------------|------------------|--------------------------------------|-----------------|-------|--------------------------------------|--|

| Symbol | Symbol Parameter    |                  | Typical                              | Maximum         | Units | Conditions                           |  |

| Zin    | Input Impedance     | -                | 150                                  |                 | kΩ    | In unbuffered mode at 20 $\rm MHz^5$ |  |

|        |                     |                  |                                      |                 |       |                                      |  |

| Vin    | Input Voltage Range | 0                |                                      | V <sub>DD</sub> | V     | Unbuffered Mode                      |  |

|        |                     |                  |                                      |                 |       |                                      |  |

Notes

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30 °C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| Table 126. | Comparator | Electrical | Characteristics |

|------------|------------|------------|-----------------|

|------------|------------|------------|-----------------|

|                   |                       |                 | = 2.7 V to<br>40 °C to + |                    |       |                    |

|-------------------|-----------------------|-----------------|--------------------------|--------------------|-------|--------------------|

| Symbol Parameter  |                       | Minimum         | Typical                  | Maximum            | Units | Conditions         |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                        |                    | mV    |                    |

| V <sub>CREF</sub> | Programmable Internal |                 | <u>+</u> 5               |                    | %     | 20-/28-pin devices |

|                   | Reference Voltage     |                 | <u>+</u> 3               |                    | %     | 8-pin devices      |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                      |                    | ns    |                    |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                        |                    | mV    |                    |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V     |                    |

## General Purpose I/O Port Input Data Sample Timing

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

#### 209

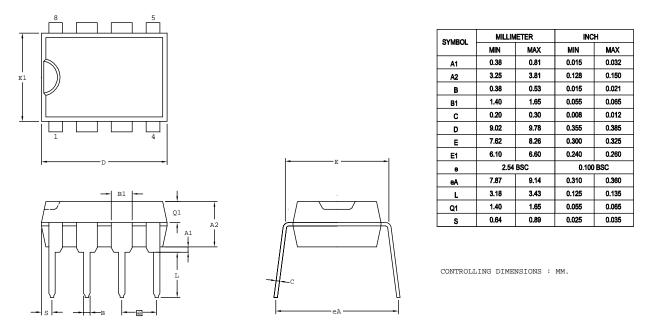

# Packaging

Figure 34 displays the 8-pin Plastic Dual Inline Package (PDIP) available for the Z8 Encore!  $XP^{\textcircled{R}}$  F0823 Series devices.

Figure 34. 8-Pin Plastic Dual Inline Package (PDIP)

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIN    | IETER                                                                               | INCH                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|-----------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| MIN MAX   |                                                                                     | MIN                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| 1.55      | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                        | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0.10 0.25 |                                                                                     | 0.004                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 1.40      | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                        | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0.36      | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                        | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0.18      | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 4.80      | 4.80 4.98                                                                           |                                                                                                                                                                                                                                                                              | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 3.81      | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                        | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 1.27      | BSC                                                                                 | .050 BSC                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| 5.84      | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                        | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0.25      | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                        | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

| 0.46      | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                        | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |

|           | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | 1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |  |  |  |  |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

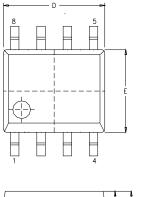

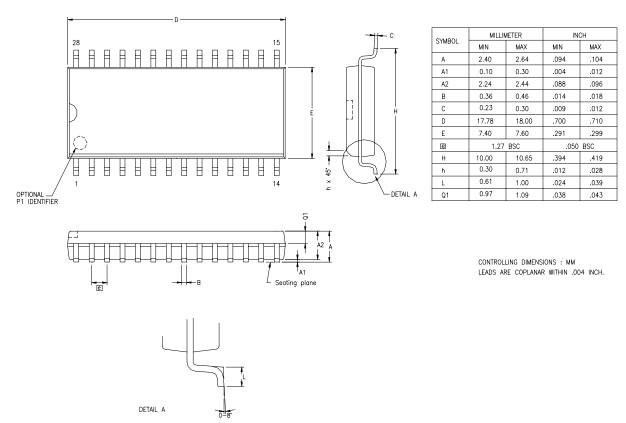

# Figure 41 displays the 28-pin Small Outline Integrated Circuit package (SOIC) available in Z8 Encore! XP F0823 Series devices.

Figure 41. 28-Pin Small Outline Integrated Circuit Package (SOIC)