Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423ph005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

WDT-Watchdog Timer time-out Indicator

If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

Reserved-0 when read

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 151.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 167), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0], and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see Oscillator Control Register Definitions on page 167) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

#### Table 17. GPIO Port Registers and Sub-Registers

0 = The drains are enabled for any output mode (unless overridden by the alternate function).

1 = The drain of the associated pin is disabled (open-drain mode).

#### Port A–C High Drive Enable Sub-Registers

The Port A–C High Drive Enable sub-register (Table 23) is accessed through the Port A–C Control register by writing 04H to the Port A–C Address register. Setting the bits in the Port A–C High Drive Enable sub-registers to 1 configures the specified port pins for high current output drive operation. The Port A–C High Drive Enable sub-register affects the pins directly and, as a result, alternate functions are also affected.

Table 23. Port A–C High Drive Enable Sub-Registers (PxHDE)

| BITS  | 7        | 6            | 5           | 4             | 3            | 2             | 1            | 0        |

|-------|----------|--------------|-------------|---------------|--------------|---------------|--------------|----------|

| FIELD | PHDE7    | PHDE6        | PHDE5       | PHDE4         | PHDE3        | PHDE2         | PHDE1        | PHDE0    |

| RESET | 0        | 0            | 0           | 0             | 0            | 0             | 0            | 0        |

| R/W   | R/W      | R/W          | R/W         | R/W           | R/W          | R/W           | R/W          | R/W      |

| ADDR  | lf 04H i | n Port A–C / | Address Reg | gister, acces | sible throug | n the Port A- | -C Control F | Register |

PHDE[7:0]—Port High Drive Enabled.

0 = The Port pin is configured for standard output current drive.

1 = The Port pin is configured for high output current drive.

#### Port A–C Stop Mode Recovery Source Enable Sub-Registers

The Port A–C Stop Mode Recovery Source Enable sub-register (Table 24) is accessed through the Port A–C Control register by writing 05H to the Port A–C Address register. Setting the bits in the Port A–C Stop Mode Recovery Source Enable sub-registers to 1 configures the specified Port pins as a Stop Mode Recovery source. During STOP mode, any logic transition on a Port pin enabled as a Stop Mode Recovery source initiates Stop Mode Recovery.

| BITS  | 7        | 6          | 5           | 4             | 3            | 2            | 1            | 0        |

|-------|----------|------------|-------------|---------------|--------------|--------------|--------------|----------|

| FIELD | PSMRE7   | PSMRE6     | PSMRE5      | PSMRE4        | PSMRE3       | PSMRE2       | PSMRE1       | PSMRE0   |

| RESET | 0        | 0          | 0           | 0             | 0            | 0            | 0            | 0        |

| R/W   | R/W      | R/W        | R/W         | R/W           | R/W          | R/W          | R/W          | R/W      |

| ADDR  | lf 05H i | n Port A–C | Address Reg | gister, acces | sible throug | h the Port A | -C Control F | Register |

|          | •                                   | •                                                                          |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer on page 87)                             |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          |                                     |                                                                            |

## Table 33. Trap and Interrupt Vectors in Order of Priority

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6   | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|-----|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0   | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          |     |     | FC           | 0H    |          |          |      |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

6. Write to the Timer Control register to enable the timer and initiate counting.

In ONE-SHOT mode, the system clock always provides the timer input. The timer period is given by the following equation:

$ONE-SHOT Mode Time-Out Period (s) = \frac{(Reload Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CONTINUOUS Mode**

In CONTINUOUS mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below to configure a timer for CONTINUOUS mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CONTINUOUS mode

- Set the prescale value

- If using the Timer Output alternate function, set the initial output level (High or Low)

- 2. Write to the Timer High and Low Byte registers to set the starting count value (usually 0001H). This action only affects the first pass in CONTINUOUS mode. After the first timer Reload in CONTINUOUS mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt (if appropriate) and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin (if using the Timer Output function) for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In CONTINUOUS mode, the system clock always provides the timer input. The timer period is given by the following equation:

CONTINUOUS Mode Time-Out Period (s) =  $\frac{\text{Reload Value} \times \text{Prescale}}{\text{System Clock Frequency (Hz)}}$

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first time-out period.

Reserved—R/W bits must be 0 during writes; 0 when read.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame

1 = The current byte is the first data byte of a new frame

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

## **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 66 and Table 67) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Table 66. UART Control 0 Register (U0CTL0)

| BITS  | 7   | 6   | 5    | 4   | 3    | 2    | 1    | 0        |

|-------|-----|-----|------|-----|------|------|------|----------|

| FIELD | TEN | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN     |

| RESET | 0   | 0   | 0    | 0   | 0    | 0    | 0    | 0        |

| R/W   | R/W | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W      |

| ADDR  |     |     |      | F4  | 2H   |      |      | <u>.</u> |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled

1 = Transmitter enabled

REN—Receive Enable

This bit enables or disables the receiver.

0 =Receiver disabled

1 =Receiver enabled

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit

- 4. When the first conversion in continuous operation is complete (after 5129 system clock cycles, plus the 40 cycles for power-up, if necessary), the ADC control logic performs the following operations:

- CEN resets to 0 to indicate the first conversion is complete. CEN remains 0 for all subsequent conversions in continuous operation.

- An interrupt request is sent to the Interrupt Controller to indicate the conversion is complete.

- 5. The ADC writes a new data result every 256 system clock cycles. For each completed conversion, the ADC control logic performs the following operations:

- Writes the 11-bit two's complement result to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- An interrupt request to the Interrupt Controller denoting conversion complete.

- 6. To disable continuous conversion, clear the CONT bit in the ADC Control register to 0.

#### Interrupts

The ADC is able to interrupt the CPU whenever a conversion has been completed and the ADC is enabled.

When the ADC is disabled, an interrupt is not asserted; however, an interrupt pending when the ADC is disabled is not cleared.

#### **Calibration and Compensation**

Z8 Encore! XP<sup>®</sup> F0823 Series ADC can be factory calibrated for offset error and gain error, with the compensation data stored in Flash memory. Alternatively, user code can perform its own calibration, storing the values into Flash themselves.

#### **Factory Calibration**

Devices that have been factory calibrated contain nine bytes of calibration data in the Flash option bit space. This data consists of three bytes for each reference type. For a list of input modes for which calibration data exists, see Zilog Calibration Data on page 147. There is 1 byte for offset, 2 bytes for gain correction.

#### User Calibration

If you have precision references available, its own external calibration can be performed, storing the values into Flash themselves.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flowchart in Figure 21 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

## Table 83. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|-----|-----|-----|-----|-----|-----|-----|-----|

| FIELD |     |     |     | FFR | EQH |     |     |     |

| RESET | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  |     |     |     | FF  | AH  |     |     |     |

FFREQH—Flash Frequency High Byte High byte of the 16-bit Flash Frequency value

## Table 84. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6 | 5 | 4   | 3   | 2 | 1 | 0 |

|-------|---|---|---|-----|-----|---|---|---|

| FIELD |   |   |   | FFR | EQL |   |   |   |

| RESET |   |   |   | (   | 0   |   |   |   |

| R/W   |   |   |   | R/  | W   |   |   |   |

| ADDR  |   |   |   | FF  | BH  |   |   |   |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value

## Table 105. Notational Shorthand

| Notation | Description                    | Operand | Range                                                                                                                        |

|----------|--------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                             |

| СС       | Condition Code                 | —       | See Condition Codes overview in the eZ8 CPU User Manual.                                                                     |

| DA       | Direct Address                 | Addrs   | Addrs represents a number in the range of 0000H to FFFFH.                                                                    |

| ER       | Extended Addressing Register   | Reg     | Reg represents a number in the range of 000H to FFFH.                                                                        |

| IM       | Immediate Data                 | #Data   | Data is a number between 00H to FFH.                                                                                         |

| lr       | Indirect Working Register      | @Rn     | n = 0–15.                                                                                                                    |

| IR       | Indirect Register              | @Reg    | Reg. represents a number in the range of 00H to FFH.                                                                         |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                            |

| IRR      | Indirect Register Pair         | @Reg    | Reg represents an even number in the range 00H to FEH                                                                        |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either 0B or 1B.                                                                    |

| r        | Working Register               | Rn      | n = 0–15.                                                                                                                    |

| R        | Register                       | Reg     | Reg. represents a number in the range of 00H to FFH.                                                                         |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to –<br>128 which is an offset relative to the address of<br>the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                            |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of 00H to FEH.                                                                   |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of 00H to FFH.                                                                       |

| X        | Indexed                        | #Index  | The register or register pair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.      |

| 190 |

|-----|

|-----|

|                    |                                                         | $T_A = $                | = 2.7 V to 3<br>-40 °C to +1<br>s otherwise |            |     |                                                   |

|--------------------|---------------------------------------------------------|-------------------------|---------------------------------------------|------------|-----|---------------------------------------------------|

| Symbol             | Parameter                                               | Minimum Typical Maximum |                                             |            |     | Conditions                                        |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                         | 5.53                                        |            | MHz | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                         | 32.7                                        |            | kHz | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                         | <u>+</u> 1                                  | <u>+</u> 4 | %   |                                                   |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                         | 3                                           |            | μs  |                                                   |

## Table 121. Internal Precision Oscillator Electrical Characteristics

200

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  |        |                                                                                                                                                                   |  |  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Parameter                                     | Minimum   | Typical                              | Maximum | Units  | Notes                                                                                                                                                             |  |  |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |  |  |

| Flash Byte Program Time                       | 20        | -                                    | 40      | μs     |                                                                                                                                                                   |  |  |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |  |  |

| Flash Mass Erase Time                         | 200       | -                                    | _       | ms     |                                                                                                                                                                   |  |  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                   |  |  |

| Flash Row Program Time                        | _         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |  |

| Data Retention                                | 100       | _                                    | -       | years  | 25 °C                                                                                                                                                             |  |  |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |  |  |

## Table 123. Flash Memory Electrical Characteristics and Timing

## Table 124. Watchdog Timer Electrical Characteristics and Timing

|                     |                          | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise stated) |         |             |       |                                                                        |  |

|---------------------|--------------------------|-----------------------------------------------------------------------------------------------------|---------|-------------|-------|------------------------------------------------------------------------|--|

| Symbol              | Parameter                | Minimum                                                                                             | Typical | Maximum     | Units | Conditions                                                             |  |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |                                                                                                     | 10      |             | kHz   |                                                                        |  |

| F <sub>WDT</sub>    | WDT Oscillator Error     |                                                                                                     |         | <u>+</u> 50 | %     |                                                                        |  |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98                                                                                                | 1       | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C                     |  |

|                     |                          | 0.70                                                                                                | 1       | 1.30        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |  |

|                     |                          | 0.50                                                                                                | 1       | 1.50        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |  |

#### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|        |                     | T <sub>A</sub> = | V <sub>DD</sub> = 3.0 V to 3.6 V<br>T <sub>A</sub> = 0 °C to +70 °C<br>(unless otherwise stated) |                 |       |                                      |

|--------|---------------------|------------------|--------------------------------------------------------------------------------------------------|-----------------|-------|--------------------------------------|

| Symbol | Parameter           | Minimum          | Typical                                                                                          | Maximum         | Units | Conditions                           |

| Zin    | Input Impedance     | -                | 150                                                                                              |                 | kΩ    | In unbuffered mode at 20 $\rm MHz^5$ |

|        |                     |                  |                                                                                                  |                 |       |                                      |

| Vin    | Input Voltage Range | 0                |                                                                                                  | V <sub>DD</sub> | V     | Unbuffered Mode                      |

|        |                     |                  |                                                                                                  |                 |       |                                      |

Notes

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30 °C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| Table 126. | Comparator | Electrical | Characteristics |

|------------|------------|------------|-----------------|

|------------|------------|------------|-----------------|

|                   |                       |                 | = 2.7 V to<br>40 °C to + |                    |       |                    |  |

|-------------------|-----------------------|-----------------|--------------------------|--------------------|-------|--------------------|--|

| Symbol            | Parameter             | Minimum         | Minimum Typical Maximum  |                    | Units | Conditions         |  |

| V <sub>OS</sub>   | Input DC Offset       |                 | 5                        |                    | mV    |                    |  |

| V <sub>CREF</sub> | Programmable Internal |                 | <u>+</u> 5               |                    | %     | 20-/28-pin devices |  |

|                   | Reference Voltage     |                 | <u>+</u> 3               |                    | %     | 8-pin devices      |  |

| T <sub>PROP</sub> | Propagation Delay     |                 | 200                      |                    | ns    |                    |  |

| V <sub>HYS</sub>  | Input Hysteresis      |                 | 4                        |                    | mV    |                    |  |

| V <sub>IN</sub>   | Input Voltage Range   | V <sub>SS</sub> |                          | V <sub>DD</sub> -1 | V     |                    |  |

## General Purpose I/O Port Input Data Sample Timing

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

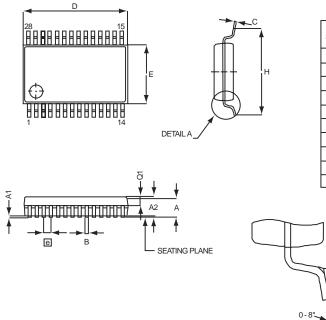

# Figure 42 displays the 28-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

|        |       | MILLIMETER | 2     | INCH  |            |          |  |  |

|--------|-------|------------|-------|-------|------------|----------|--|--|

| SYMBOL | MIN   | NOM        | MAX   | MIN   | NOM        | MAX      |  |  |

| А      | 1.73  | 1.86       | 1.99  | 0.068 | 0.073      | 0.078    |  |  |

| A1     | 0.05  | 0.13       | 0.21  | 0.002 | 0.005      | 0.008    |  |  |

| A2     | 1.68  | 1.73       | 1.78  | 0.066 | 0.068      | 0.070    |  |  |

| В      | 0.25  |            | 0.38  | 0.010 |            | 0.015    |  |  |

| С      | 0.09  | -          | 0.20  | 0.004 | 0.006      | 0.008    |  |  |

| D      | 10.07 | 10.20      | 10.33 | 0.397 | 0.402      | 0.407    |  |  |

| E      | 5.20  | 5.30       | 5.38  | 0.205 | 0.209      | 0.212    |  |  |

| е      |       | 0.65 TYP   |       |       | 0.0256 TYF | <b>b</b> |  |  |

| н      | 7.65  | 7.80       | 7.90  | 0.301 | 0.307      | 0.311    |  |  |

| L      | 0.63  | 0.75       | 0.95  | 0.025 | 0.030      | 0.037    |  |  |

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

Figure 42. 28-Pin Small Shrink Outline Package (SSOP)

|                                          |             |           | S         | ots        | limers                 | 10-Bit A/D Channels | UART with IrDA | otion               |

|------------------------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash       | RAM       | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit /            | UART v         | Description         |

| Z8 Encore! XP with 4                     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur                      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0413PB005SC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005SC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005SC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005SC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005SC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005SC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005SC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005SC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005SC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu                       | re: -40 °C  | to 105 °0 | 0         |            |                        |                     |                |                     |

| Z8F0413PB005EC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0413QB005EC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0413SB005EC                           | 4 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0413SH005EC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0413HH005EC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0413PH005EC                           | 4 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0413SJ005EC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0413HJ005EC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0413PJ005EC                           | 4 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |             |           |           |            |                        |                     |                |                     |

220

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

235

reset in STOP mode 89 time-out response 88 Watchdog Timer Control Register (WDTCTL) 90 WDTCTL register 90, 128, 167 WDTH register 91 WDTL register 91 WDTU register 91 working register 173 working register pair 173

# Χ

X 173 XOR 178 XORX 178

# Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2