Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423ph005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date             | Revision<br>Level | Description                                                                                                                                                                                                       | Page No                              |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| March<br>2008    | 14                | Changed title to Z8 Encore! XP F0823 Series and the contents to match the title.                                                                                                                                  | •                                    |

| December<br>2007 | 13                | Updated title from Z8 Encore! 8K and 4K Series to Z8<br>Encore! XP Z8F0823 Series. Updated Figure 3, Table<br>15, Table 35, Table 59 through Table 61, Table 119,<br>and Part Number Suffix Designations section. | 8, 39,<br>59, 91,<br>196, and<br>226 |

| August<br>2007   | 12                | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                                            | 2, 42,<br>and 13                     |

| June 2007        | 11                | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                                        | All                                  |

| December<br>2006 | 10                | Updated Ordering Information chapter.                                                                                                                                                                             | 217                                  |

# **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

| Signal Mnemonic                                      | I/O | Description                                                                                                                                                                                                           |

|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog                                               |     |                                                                                                                                                                                                                       |

| ANA[7:0]                                             | Ι   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                                                 | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                                          |     |                                                                                                                                                                                                                       |

| CLKIN                                                | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                                          |     |                                                                                                                                                                                                                       |

| LED                                                  | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger                                     |     |                                                                                                                                                                                                                       |

| DBG                                                  | I/O | Debug. This signal is the control and data input and output to and from the OCD.                                                                                                                                      |

|                                                      |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull                                                                                                                                               |

|                                                      |     | up resistor to ensure proper operation.                                                                                                                                                                               |

| Reset                                                |     |                                                                                                                                                                                                                       |

| RESET                                                | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                                         |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>                                      | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub>                                     | Ι   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>                                      | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>                                     | I   | Analog Ground.                                                                                                                                                                                                        |

| Note: The AV <sub>DD</sub> and A<br>PB7 on 28-pin pa |     | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and without ADC.                                                                                                                        |

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

Caution:

To avoid missing interrupts, use the following coding style to clear bits in the Interrupt Request 0 register:

#### Good coding style that avoids lost interrupt requests: ANDX IRQ0, MASK

#### **Software Interrupt Assertion**

Program code generates interrupts directly. Writing a 1 to the correct bit in the Interrupt Request register triggers an interrupt (assuming that interrupt is enabled). When the interrupt request is acknowledged by the eZ8 CPU, the bit in the Interrupt Request register is automatically cleared to 0.

**Caution:** The following coding style used to generate software interrupts by setting bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests: LDX r0, IRQ0 OR r0, MASK LDX IRQ0, r0

**Caution:** To avoid missing interrupts, use the following coding style to set bits in the Interrupt Request registers:

Good coding style that avoids lost interrupt requests: ORX IRQ0, MASK

## Watchdog Timer Interrupt Assertion

The Watchdog Timer interrupt behavior is different from interrupts generated by other sources. The Watchdog Timer continues to assert an interrupt as long as the timeout condition continues. As it operates on a different (and usually slower) clock domain than the rest of the device, the Watchdog Timer continues to assert this interrupt for many system clocks until the counter rolls over.

**Caution:** To avoid re-triggerings of the Watchdog Timer interrupt after exiting the associated interrupt service routine, it is recommended that the service routine continues to read from the RSTSTAT register until the WDT bit is cleared as given in the following coding sample:

> CLEARWDT: LDX r0, RSTSTAT ; read reset status register to clear wdt bit BTJNZ 5, r0, CLEARWDT ; loop until bit is cleared

#### Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[ | x] Priority | Description |

|------------|----------|-------------|-------------|

| 1          | 1        | Level 3     | High        |

where x indicates the register bits from 0–7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|-----|------|-------|-----|-------|-------|-------|-------|

| FIELD |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |     |      |       | FC  | 7H    |       |       |       |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|-------|----------|-----|-----|-----|-------|-------|-------|-------|

| FIELD | Reserved |     |     |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |          |     |     | FC  | 8H    |       |       |       |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

### Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

| BITS  | 7    | 6 | 5             | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|------|---|---------------|----|----|---|---|---|--|--|

| FIELD | IRQE |   | Reserved      |    |    |   |   |   |  |  |

| RESET | 0    | 0 | 0             | 0  | 0  | 0 | 0 | 0 |  |  |

| R/W   | R/W  | R | R R R R R R R |    |    |   |   |   |  |  |

| ADDR  |      |   |               | FC | FH |   |   |   |  |  |

## Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$$

#### COMPARE Mode

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the

## Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Flash Option Bit, see Flash Option Bits on page 141.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see Reset Status Register on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and Z8 Encore! XP F0823 Series are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

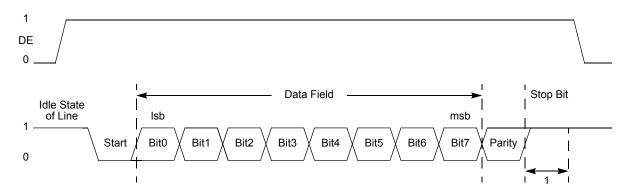

### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |  |  |  |

|-------|---------|------|---------|------|-------|--------|--------|------|--|--|--|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |  |  |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |  |  |  |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |  |  |

| ADDR  |         | F43H |         |      |       |        |        |      |  |  |  |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

# **Flash Option Bits**

Programmable Flash option bits allow user configuration of certain aspects of Z8 Encore! XP<sup>®</sup> F0823 Series operation. The feature configuration data is stored in the Flash program memory and loaded into holding registers during Reset. The features available for control through the Flash Option Bits include:

- Watchdog Timer time-out response selection-interrupt or system reset

- Watchdog Timer always on (enabled at Reset)

- The ability to prevent unwanted read access to user code in Program Memory

- The ability to prevent accidental programming and erasure of all or a portion of the user code in Program Memory

- Voltage Brownout configuration-always enabled or disabled during STOP mode to reduce STOP mode power consumption

- Factory trimming information for the internal precision oscillator

- Factory calibration values for ADC

- Factory serialization and randomized lot identifier (optional)

## Operation

## **Option Bit Configuration By Reset**

Each time the Flash Option Bits are programmed or erased, the device must be Reset for the change to take effect. During any reset operation (System Reset, Power-On Reset, or Stop Mode Recovery), the Flash Option Bits are automatically read from the Flash Program Memory and written to Option Configuration registers. The Option Configuration registers control operation of the devices within the Z8 Encore! XP F0823 Series. Option Bit control is established before the device exits Reset and the eZ8 CPU begins code execution. The Option Configuration registers are not part of the Register File and are not accessible for read or write access.

## **Option Bit Types**

#### **User Option Bits**

The user option bits are contained in the first two bytes of program memory. Access to these bits has been provided because these locations contain application-specific device

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- $0 = Crystal \ oscillator \ is \ enabled \ during \ reset, \ resulting \ in \ longer \ reset \ timing$

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

## **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

## Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS        | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-------------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD       | Reserved                                        |     |     |     |     |     |     |     |  |  |  |

| RESET       | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W         | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR        | Information Page Memory 0020H                   |     |     |     |     |     |     |     |  |  |  |

| Note: U = U | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

Reserved—Altering this register may result in incorrect device operation.

## Trim Bit Address 0001H—Reserved

#### Table 90. Trim Option Bits at 0001H

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|--|

| FIELD     | Reserved                                        |     |     |     |     |     |     |     |  |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |  |

| ADDR      | Information Page Memory 0021H                   |     |     |     |     |     |     |     |  |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |  |

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

#### Example 1

If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 103. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, s | src) |

|------------------------|-----|------|-----|-------------|------|

| Object Code            | 04  | 08   | 43  | (OPC src, d | lst) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

#### Table 104. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 105.

| Assembly<br>Mnemonic Symbolic Operation                                              |                                                              | Address Mode<br>Opcode(s) |            | Fla        | ıgs |   |              | – Fetch | Instr. |   |        |   |

|--------------------------------------------------------------------------------------|--------------------------------------------------------------|---------------------------|------------|------------|-----|---|--------------|---------|--------|---|--------|---|

|                                                                                      | dst                                                          | src                       | (Hex)      | С          | z   | S | v            | D       | Н      |   | Cycles |   |

| LDC dst, src $dst \leftarrow src$                                                    | $dst \gets src$                                              | r                         | Irr        | C2         | -   | _ |              | _       | _      | - | 2      | 5 |

|                                                                                      | lr                                                           | Irr                       | C5         | _          |     |   |              |         |        | 2 | 9      |   |

|                                                                                      | Irr                                                          | r                         | D2         | _          |     |   |              |         |        | 2 | 5      |   |

| LDCI dst, src $dst \leftarrow src$<br>$r \leftarrow r + 1$<br>$rr \leftarrow rr + 1$ |                                                              | lr                        | Irr        | C3         | -   | _ | _            | _       | _      | _ | 2      | 9 |

|                                                                                      | Irr                                                          | lr                        | D3         | _          |     |   |              |         |        | 2 | 9      |   |

| LDE dst, src $dst \leftarrow src$                                                    | r                                                            | Irr                       | 82         | -          | _   |   | _            | _       | -      | 2 | 5      |   |

|                                                                                      | Irr                                                          | r                         | 92         | _          |     |   |              |         |        | 2 | 5      |   |

| LDEI dst, src $dst \leftarrow src$<br>$r \leftarrow r + 1$<br>$rr \leftarrow rr + 1$ | lr                                                           | Irr                       | 83         | -          | _   |   | _            | _       | -      | 2 | 9      |   |

|                                                                                      | Irr                                                          | lr                        | 93         | _          |     |   |              |         |        | 2 | 9      |   |

| LDWX dst, src                                                                        | $dst \leftarrow src$                                         | ER                        | ER         | 1FE8       | _   | _ | . <u> </u>   | _       | _      | _ | 5      | 4 |

| LDX dst, src dst ← src                                                               | r                                                            | ER                        | 84         | -          | _   |   | _            | _       | -      | 3 | 2      |   |

|                                                                                      | lr                                                           | ER                        | 85         | _          |     |   |              |         |        | 3 | 3      |   |

|                                                                                      | R                                                            | IRR                       | 86         | _          |     |   |              |         |        | 3 | 4      |   |

|                                                                                      | IR                                                           | IRR                       | 87         | _          |     |   |              |         |        | 3 | 5      |   |

|                                                                                      | r                                                            | X(rr)                     | 88         | _          |     |   |              |         |        | 3 | 4      |   |

|                                                                                      | X(rr)                                                        | r                         | 89         | _          |     |   |              |         |        | 3 | 4      |   |

|                                                                                      |                                                              | ER                        | r          | 94         | _   |   |              |         |        |   | 3      | 2 |

|                                                                                      | ER                                                           | lr                        | 95         | _          |     |   |              |         |        | 3 | 3      |   |

|                                                                                      | IRR                                                          | R                         | 96         |            |     |   |              |         |        | 3 | 4      |   |

|                                                                                      | IRR                                                          | IR                        | 97         | _          |     |   |              |         |        | 3 | 5      |   |

|                                                                                      | ER                                                           | ER                        | E8         | _          |     |   |              |         |        | 4 | 2      |   |

|                                                                                      |                                                              | ER                        | IM         | E9         | _   |   |              |         |        |   | 4      | 2 |

| LEA dst, X(src) dst $\leftarrow$ src + X                                             | $dst \gets src + X$                                          | r                         | X(r)       | 98         | -   | _ |              | _       | _      | - | 3      | 3 |

|                                                                                      | rr                                                           | X(rr)                     | 99         |            |     |   |              |         |        | 3 | 5      |   |

| MULT dst                                                                             | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR                        |            | F4         | _   | _ | . <u> </u>   | _       | _      | _ | 2      | 8 |

| NOP                                                                                  | No operation                                                 |                           |            | 0F         | -   | _ |              | _       | _      | - | 1      | 2 |

| Flags Notation:                                                                      | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resul               | t of the c | operation. |     |   | ese<br>et to |         | 0      |   |        |   |

### Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly<br>Mnemonic Symbolic Operation      | Address Mode<br>Opcode(s)                                                                   |            | Flags       |           |   |              |   |   | – Fetch | Inetr |        |   |

|----------------------------------------------|---------------------------------------------------------------------------------------------|------------|-------------|-----------|---|--------------|---|---|---------|-------|--------|---|

|                                              | dst                                                                                         | src        | (Hex)       | С         | Ζ | S            | v | D | Н       |       | Cycles |   |

| SUBX dst, src $dst \leftarrow dst - src$     | $dst \gets dst - src$                                                                       | ER         | ER          | 28        | * | *            | * | * | 1       | *     | 4      | 3 |

|                                              |                                                                                             | ER         | IM          | 29        | _ |              |   |   |         |       | 4      | 3 |

| SWAP dst $dst[7:4] \leftrightarrow dst[3:0]$ | R                                                                                           |            | F0          | Х         | * | *            | Х | _ | _       | 2     | 2      |   |

|                                              | IR                                                                                          |            | F1          | _         |   |              |   |   |         | 2     | 3      |   |

| TCM dst, src (NOT dst) AND src               | r                                                                                           | r          | 62          | _         | * | *            | 0 | _ | _       | 2     | 3      |   |

|                                              | r                                                                                           | lr         | 63          |           |   |              |   |   |         | 2     | 4      |   |

|                                              | R                                                                                           | R          | 64          | _         |   |              |   |   |         | 3     | 3      |   |

|                                              | R                                                                                           | IR         | 65          |           |   |              |   |   |         | 3     | 4      |   |

|                                              | R                                                                                           | IM         | 66          | _         |   |              |   |   |         | 3     | 3      |   |

|                                              | IR                                                                                          | IM         | 67          | _         |   |              |   |   |         | 3     | 4      |   |

| TCMX dst, src (NOT dst) AND src              | ER                                                                                          | ER         | 68          | _         | * | *            | 0 | _ | _       | 4     | 3      |   |

|                                              |                                                                                             | ER         | IM          | 69        | _ |              |   |   |         |       | 4      | 3 |

| TM dst, src dst AND src                      | r                                                                                           | r          | 72          | _         | * | *            | 0 | - | -       | 2     | 3      |   |

|                                              | r                                                                                           | lr         | 73          | _         |   |              |   |   |         | 2     | 4      |   |

|                                              | R                                                                                           | R          | 74          | _         |   |              |   |   |         | 3     | 3      |   |

|                                              | R                                                                                           | IR         | 75          |           |   |              |   |   |         | 3     | 4      |   |

|                                              | R                                                                                           | IM         | 76          |           |   |              |   |   |         | 3     | 3      |   |

|                                              | IR                                                                                          | IM         | 77          | _         |   |              |   |   |         | 3     | 4      |   |

| TMX dst, src dst AND src                     | ER                                                                                          | ER         | 78          | _         | * | *            | 0 | _ | -       | 4     | 3      |   |

|                                              | ER                                                                                          | IM         | 79          | _         |   |              |   |   |         | 4     | 3      |   |

| TRAP Vector                                  | $SP \leftarrow SP - 2$<br>@SP ← PC<br>$SP \leftarrow SP - 1$<br>@SP ← FLAGS<br>PC ← @Vector |            | Vector      | F2        | _ | -            | - | - | _       | _     | 2      | 6 |

| WDT                                          |                                                                                             |            |             | 5F        | _ | _            | _ | _ | _       | -     | 1      | 2 |

| Flags Notation:                              | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                | f the resu | It of the o | peration. |   | = Re<br>= Se |   |   | 0       |       |        |   |

## Table 115. eZ8 CPU Instruction Summary (Continued)

TM 176

**HALT 176 INC 175 INCW 175 IRET 178** JP 178 LD 177 LDC 177 LDCI 176, 177 LDE 177 LDEI 176 LDX 177 LEA 177 load 177 logical 177 **MULT 175** NOP 176 OR 177 ORX 178 POP 177 POPX 177 program control 178 **PUSH 177** PUSHX 177 **RCF 176 RET 178** RL 178 **RLC 178** rotate and shift 178 RR 178 **RRC 178** SBC 175 SCF 176, 177 SRA 179 SRL 179 **SRP 177 STOP 177** SUB 175 **SUBX 175 SWAP 179 TCM 176 TCMX 176**

**DJNZ 178**

EI 176

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

TMX 176 **TRAP 178** Watchdog Timer refresh 177 XOR 178 **XORX 178** instructions, eZ8 classes of 174 interrupt control register 64 interrupt controller 53 architecture 53 interrupt assertion types 56 interrupt vectors and priority 56 operation 55 register definitions 58 software interrupt assertion 57 interrupt edge select register 63 interrupt request 0 register 58 interrupt request 1 register 59 interrupt request 2 register 59 interrupt return 178 interrupt vector listing 53 interrupts **UART 101** IR 173 lr 173 **IrDA** architecture 113 block diagram 113 control register definitions 116 operation 113 receiving data 115 transmitting data 114 **IRET 178** IRQ0 enable high and low bit registers 60 IRQ1 enable high and low bit registers 61 IRQ2 enable high and low bit registers 62 **IRR 173** Irr 173

## J

JP 178 jump, conditional, relative, and relative conditional 178

## Т

**TCM 176 TCMX 176** test complement under mask 176 test complement under mask - extended addressing 176 test under mask 176 test under mask - extended addressing 176 timer signals 9 timers 67 architecture 67 block diagram 67 CAPTURE mode 74, 75, 84, 85 CAPTURE/COMPARE mode 78, 85 COMPARE mode 76, 84 CONTINUOUS mode 69, 84 COUNTER mode 70, 71 COUNTER modes 84 GATED mode 77, 84 ONE-SHOT mode 68, 84 operating mode 68 PWM mode 72, 73, 84, 85 reading the timer count values 79 reload high and low byte registers 80 timer control register definitions 80 timer output signal operation 79 timers 0-3 control registers 82, 83 high and low byte registers 80, 81 TM 176 TMX 176 tools, hardware and software 226 transmit IrDA data 114 transmitting UART data-polled method 95 transmitting UART dat-interrupt-driven method 96 **TRAP 178**

## U

UART 4 architecture 93 baud rate generator 103

control register definitions 104 controller signals 9 data format 94 interrupts 101 MULTIPROCESSOR mode 99 receiving data using interrupt-driven method 98 receiving data using the polled method 97 transmitting data using the interrupt-driven method 96 transmitting data using the polled method 95 x baud rate high and low registers 110 x control 0 and control 1 registers 107 x status 0 and status 1 registers 105, 106 UxBRH register 110 UxBRL register 110 UxCTL0 register 107, 110 UxCTL1 register 108 UxRXD register 105 UxSTAT0 register 105 UxSTAT1 register 106 UxTXD register 104

# V

vector 173 Voltage Brownout reset (VBR) 24

## W

Watchdog Timer approximate time-out delay 87 CNTL 24 control register 89, 127, 167 electrical characteristics and timing 200, 202 interrupt in normal operation 88 interrupt in STOP mode 88 refresh 88, 177 reload unlock sequence 89 reload upper, high and low registers 90 reset 25 reset in normal operation 89

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.