Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status Obsolete   Core Processor eZ8                        |      |

|---------------------------------------------------------------------|------|

| Core Processor e78                                                  |      |

|                                                                     |      |

| Core Size 8-Bit                                                     |      |

| Speed 5MHz                                                          |      |

| Connectivity IrDA, UART/USART                                       |      |

| Peripherals Brown-out Detect/Reset, LED, POR, PWM, WDT              |      |

| Number of I/O 22                                                    |      |

| Program Memory Size 4KB (4K x 8)                                    |      |

| Program Memory Type FLASH                                           |      |

| EEPROM Size -                                                       |      |

| RAM Size 1K x 8                                                     |      |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6V                               |      |

| Data Converters A/D 8x10b                                           |      |

| Oscillator Type Internal                                            |      |

| Operating Temperature -40°C ~ 105°C (TA)                            |      |

| Mounting Type Through Hole                                          |      |

| Package / Case     28-DIP (0.600", 15.24mm)                         |      |

| Supplier Device Package -                                           |      |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f0423pj00 | 05ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                       | Reset Characteristics and Latency                      |            |                                                               |  |  |  |

|-----------------------|--------------------------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| Reset<br>Type         | Control Registers                                      | eZ8<br>CPU | Reset Latency (Delay)                                         |  |  |  |

| System<br>Reset       | Reset (as applicable)                                  | Reset      | 66 Internal Precision Oscillator Cycles                       |  |  |  |

| Stop Mode<br>Recovery | Unaffected, except<br>WDT_CTL and OSC_CTL<br>registers | Reset      | 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |  |  |  |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the IPO requires 4 µs to start up. Then the Z8 Encore! XP F0823 Series device is held in Reset for 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is enabled in the Flash option bits, this reset period is increased to 5000 IPO cycles. When a reset occurs because of a low voltage condition or Power-On Reset, this delay is measured from the time that the supply voltage first exceeds the POR level. If the external pin reset remains asserted at the end of the reset period, the device remains in reset until the pin is deasserted.

At the beginning of Reset, all GPIO pins are configured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip peripherals are idle; however, the on-chip crystal oscillator and Watchdog Timer oscillator continue to run.

Upon Reset, control registers within the Register File that have a defined Reset value are loaded with their reset values. Other control registers (including the Stack Pointer, Register Pointer, and Flags) and general-purpose RAM are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset vector address.

When the control registers are re-initialized by a system reset, the system clock after reset is always the IPO. The software must reconfigure the oscillator control block, such that the correct system clock source is enabled and selected.

# **Reset Sources**

Table 10 lists the possible sources of a System Reset.

| ial Conditions                              |

|---------------------------------------------|

| t delay begins after supply voltage exceeds |

| Table 10. | <b>Reset Sources</b> | and Resulting | Reset Type |

|-----------|----------------------|---------------|------------|

|           |                      | and Resulting | Redet Type |

| Operating Mode       | Reset Source                                      | Special Conditions                                                                                           |  |  |

|----------------------|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------|--|--|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                   |  |  |

|                      | Watchdog Timer time-out when configured for Reset | None.                                                                                                        |  |  |

|                      | RESET pin assertion                               | All reset pulses less than three system clocks in width are ignored.                                         |  |  |

|                      | OCD initiated Reset<br>(OCDCTL[0] set to 1)       | System Reset, except the OCD is unaffected by the reset.                                                     |  |  |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                   |  |  |

|                      | RESET pin assertion                               | All reset pulses less than the specified analog delay are ignored. See Electrical Characteristi on page 193. |  |  |

|                      | DBG pin driven Low                                | None.                                                                                                        |  |  |

### **Power-On Reset**

Each device in the Z8 Encore! XP F0823 Series contains an internal POR circuit. The POR circuit monitors the supply voltage and holds the device in the Reset state until the supply voltage reaches a safe operating level. After the supply voltage exceeds the POR voltage threshold ( $V_{POR}$ ), the device is held in the Reset state until the POR Counter has timed out. If the crystal oscillator is enabled by the option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series device exits the POR state, the eZ8 CPU fetches the Reset vector. Following the POR, the POR status bit in Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 5 displays POR operation. For the POR threshold voltage ( $V_{POR}$ ), see Electrical Characteristics on page 193.

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

### Table 17. GPIO Port Registers and Sub-Registers

# Table 19. Port A–C Control Registers (PxCTL)

| BITS  | 7                | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | PCTL             |     |     |     |     |     |     |     |

| RESET | 00H              |     |     |     |     |     |     |     |

| R/W   | R/W              | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | FD1H, FD5H, FD9H |     |     |     |     |     |     |     |

PCTL[7:0]—Port Control

The Port Control register provides access to all sub-registers that configure the GPIO Port operation.

# Port A-C Data Direction Sub-Registers

The Port A–C Data Direction sub-register is accessed through the Port A–C Control register by writing 01H to the Port A–C Address register (Table 20).

| BITS  | 7        | 6                                                                                     | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|----------|---------------------------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|--|

| FIELD | DD7      | DD6                                                                                   | DD5 | DD4 | DD3 | DD2 | DD1 | DD0 |  |

| RESET | 1        | 1                                                                                     | 1   | 1   | 1   | 1   | 1   | 1   |  |

| R/W   | R/W      | R/W                                                                                   | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  | lf 01H i | If 01H in Port A–C Address Register, accessible through the Port A–C Control Register |     |     |     |     |     |     |  |

# Table 20. Port A–C Data Direction Sub-Registers (PxDD)

DD[7:0]—Data Direction

These bits control the direction of the associated port pin. Port Alternate Function operation overrides the Data Direction register setting.

0 = Output. Data in the Port A–C Output Data register is driven onto the port pin.

1 = Input. The port pin is sampled and the value written into the Port A–C Input Data Register. The output driver is tristated.

# Port A–C Alternate Function Sub-Registers

The Port A–C Alternate Function sub-register (Table 21) is accessed through the Port A–C Control register by writing 02H to the Port A–C Address register. The Port A–C Alternate Function sub-registers enable the alternate function selection on pins. If disabled, pins functions as GPIO. If enabled, select one of four alternate functions using alternate function set subregisters 1 and 2 as described in the Port A–C Alternate Function Set 1 Sub-Registers on page 48 and Port A–C Alternate Function Set 2 Sub-Registers on

### Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[ | x] Priority | Description |

|------------|----------|-------------|-------------|

| 1          | 1        | Level 3     | High        |

where x indicates the register bits from 0–7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |  |  |

|-------|-----|------|-------|-----|-------|-------|-------|-------|--|--|

| FIELD |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |  |  |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |  |  |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |  |  |

| ADDR  |     | FC7H |       |     |       |       |       |       |  |  |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7    | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|------|------|-------|-----|-------|-------|-------|-------|

| FIELD |      | Rese | erved |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET | 0    | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W  | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  | FC8H |      |       |     |       |       |       |       |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

# Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

### WDT Reset in NORMAL Operation

If configured to generate a Reset when a time-out occurs, the Watchdog Timer forces the device into the System Reset state. The WDT status bit in the Watchdog Timer Control register is set to 1. For more information on System Reset, see Reset and Stop Mode Recovery on page 21.

### WDT Reset in STOP Mode

If configured to generate a Reset when a time-out occurs and the device is in STOP mode, the Watchdog Timer initiates a Stop Mode Recovery. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following WDT time-out in STOP mode. For more information, see Reset and Stop Mode Recovery on page 21.

# Watchdog Timer Reload Unlock Sequence

Writing the unlock sequence to the Watchdog Timer Control Register (WDTCTL) address unlocks the three Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) to allow changes to the time-out period. These write operations to the WDTCTL register address produce no effect on the bits in the WDTCTL register. The locking mechanism prevents spurious writes to the Reload registers. The following sequence is required to unlock the Watchdog Timer Reload Byte Registers (WDTU, WDTH, and WDTL) for write access.

- 1. Write 55H to the Watchdog Timer Control register (WDTCTL).

- 2. Write AAH to the Watchdog Timer Control register (WDTCTL).

- 3. Write the Watchdog Timer Reload Upper Byte register (WDTU).

- 4. Write the Watchdog Timer Reload High Byte register (WDTH).

- 5. Write the Watchdog Timer Reload Low Byte register (WDTL).

All three Watchdog Timer Reload registers must be written in the order just listed. There must be no other register writes between each of these operations. If a register write occurs, the lock state machine resets and no further writes can occur unless the sequence is restarted. The value in the Watchdog Timer Reload registers is loaded into the counter when the Watchdog Timer is first enabled and every time a WDT instruction is executed.

# Watchdog Timer Control Register Definitions

### Watchdog Timer Control Register

The Watchdog Timer Control (WDTCTL) register is a write-only control register. Writing the 55H, AAH unlock sequence to the WDTCTL register address unlocks the three

# Table 59. Watchdog Timer Reload Upper Byte Register (WDTU)

| BITS                                                                                    | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |

|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|------|------|--|

| FIELD                                                                                   | WDTU |      |      |      |      |      |      |      |  |

| RESET                                                                                   |      | 00H  |      |      |      |      |      |      |  |

| R/W                                                                                     | R/W* |  |

| ADDR                                                                                    | FF1H |      |      |      |      |      |      |      |  |

| R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |      |  |

WDTU—WDT Reload Upper Byte Most significant byte (MSB), Bits[23:16], of the 24-bit WDT reload value.

# Table 60. Watchdog Timer Reload High Byte Register (WDTH)

| BITS     | 7                                                                                       | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|--|--|

| FIELD    |                                                                                         | WDTH |      |      |      |      |      |      |  |  |  |  |  |

| RESET    |                                                                                         | 04H  |      |      |      |      |      |      |  |  |  |  |  |

| R/W      | R/W*                                                                                    | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |  |  |  |

| ADDR     | FF2H                                                                                    |      |      |      |      |      |      |      |  |  |  |  |  |

| R/W*—Rea | R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |  |  |  |

WDTH—WDT Reload High Byte

Middle byte, Bits[15:8], of the 24-bit WDT reload value.

### Table 61. Watchdog Timer Reload Low Byte Register (WDTL)

| BITS     | 7                                                                                       | 6    | 5    | 4    | 3    | 2    | 1    | 0    |  |  |  |  |

|----------|-----------------------------------------------------------------------------------------|------|------|------|------|------|------|------|--|--|--|--|

| FIELD    | WDTL                                                                                    |      |      |      |      |      |      |      |  |  |  |  |

| RESET    | 00H                                                                                     |      |      |      |      |      |      |      |  |  |  |  |

| R/W      | R/W*                                                                                    | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* | R/W* |  |  |  |  |

| ADDR     | FF3H                                                                                    |      |      |      |      |      |      |      |  |  |  |  |

| R/W*—Rea | R/W*—Read returns the current WDT count value. Write sets the appropriate Reload Value. |      |      |      |      |      |      |      |  |  |  |  |

WDTL—WDT Reload Low

Least significant byte (LSB), Bits[7:0], of the 24-bit WDT reload value.

- 6. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to step 7. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 7. Write the UART Control 1 register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR mode is enabled,.

- 11. To transmit additional bytes, return to step 5.

### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow the steps below to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions, if MULTIPROCESSOR mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 7. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01 = Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control register.

### **Oscillator Control Register**

The Oscillator Control register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6                           | 5     | 4     | 3     | 2      | 1 | 0 |  |  |  |  |  |

|-------|-------|-----------------------------|-------|-------|-------|--------|---|---|--|--|--|--|--|

| FIELD | INTEN | Reserved                    | WDTEN | POFEN | WDFEN | SCKSEL |   |   |  |  |  |  |  |

| RESET | 1     | 0                           | 1     | 0     | 0     | 0      | 0 | 0 |  |  |  |  |  |

| R/W   | R/W   | R/W R/W R/W R/W R/W R/W R/W |       |       |       |        |   |   |  |  |  |  |  |

| ADDR  |       | F86H                        |       |       |       |        |   |   |  |  |  |  |  |

Table 102. Oscillator Control Register (OSCCTL)

| Assembly        |                                                                       | Addre       | ss Mode     | - Opcode(s) | Fla | ıgs          |   |   |   |   | - Fetch | Instr. |

|-----------------|-----------------------------------------------------------------------|-------------|-------------|-------------|-----|--------------|---|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                    | dst         | src         | (Hex)       | С   | Ζ            | S | v | D | Н | Cycles  |        |

| COM dst         | dst ← ~dst                                                            | R           |             | 60          | -   | *            | * | 0 | _ | _ | 2       | 2      |

|                 |                                                                       | IR          |             | 61          | _   |              |   |   |   |   | 2       | 3      |

| CP dst, src     | dst - src                                                             | r           | r           | A2          | *   | *            | * | * | - | _ | 2       | 3      |

|                 |                                                                       | r           | lr          | A3          | _   |              |   |   |   |   | 2       | 4      |

|                 |                                                                       | R           | R           | A4          | _   |              |   |   |   |   | 3       | 3      |

|                 |                                                                       | R           | IR          | A5          |     |              |   |   |   |   | 3       | 4      |

|                 |                                                                       | R           | IM          | A6          | _   |              |   |   |   |   | 3       | 3      |

|                 |                                                                       | IR          | IM          | A7          | _   |              |   |   |   |   | 3       | 4      |

| CPC dst, src    | dst - src - C                                                         | r           | r           | 1F A2       | *   | *            | * | * | _ | _ | 3       | 3      |

|                 |                                                                       | r           | lr          | 1F A3       | _   |              |   |   |   |   | 3       | 4      |

|                 |                                                                       | R           | R           | 1F A4       | _   |              |   |   |   |   | 4       | 3      |

|                 |                                                                       | R           | IR          | 1F A5       | _   |              |   |   |   |   | 4       | 4      |

|                 |                                                                       | R           | IM          | 1F A6       | _   |              |   |   |   |   | 4       | 3      |

|                 |                                                                       | IR          | IM          | 1F A7       | _   |              |   |   |   |   | 4       | 4      |

| CPCX dst, src   | dst - src - C                                                         | ER          | ER          | 1F A8       | *   | *            | * | * | - | _ | 5       | 3      |

|                 |                                                                       | ER          | IM          | 1F A9       |     |              |   |   |   |   | 5       | 3      |

| CPX dst, src    | dst - src                                                             | ER          | ER          | A8          | *   | *            | * | * | - | _ | 4       | 3      |

|                 |                                                                       | ER          | IM          | A9          |     |              |   |   |   |   | 4       | 3      |

| DA dst          | $dst \gets DA(dst)$                                                   | R           |             | 40          | *   | *            | * | Х | _ | _ | 2       | 2      |

|                 |                                                                       | IR          |             | 41          | _   |              |   |   |   |   | 2       | 3      |

| DEC dst         | dst ← dst - 1                                                         | R           |             | 30          | -   | *            | * | * | _ | _ | 2       | 2      |

|                 |                                                                       | IR          |             | 31          | _   |              |   |   |   |   | 2       | 3      |

| DECW dst        | dst ← dst - 1                                                         | RR          |             | 80          | -   | *            | * | * | - | _ | 2       | 5      |

|                 |                                                                       | IRR         |             | 81          |     |              |   |   |   |   | 2       | 6      |

| DI              | $IRQCTL[7] \leftarrow 0$                                              |             |             | 8F          | -   | -            | - | - | - | _ | 1       | 2      |

| DJNZ dst, RA    | $dst \leftarrow dst - 1$<br>if dst $\neq 0$<br>PC $\leftarrow$ PC + X | r           |             | 0A-FA       | -   | -            | - | - | - | - | 2       | 3      |

| EI              | $IRQCTL[7] \leftarrow 1$                                              |             |             | 9F          | -   | _            | _ | _ | _ | _ | 1       | 2      |

| Flags Notation: | * = Value is a function<br>– = Unaffected<br>X = Undefined            | of the resu | It of the o | peration.   |     | = Re<br>= Se |   |   | 0 |   |         |        |

### Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                              | Addre       | ss Mode    | -<br>Opcode(s) | Fla | ıgs |              |   |   |   | - Fetch | Instr. |

|-----------------|--------------------------------------------------------------|-------------|------------|----------------|-----|-----|--------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                           | dst         | src        | (Hex)          | С   | z   | S            | v | D | Н |         | Cycles |

| LDC dst, src    | $dst \gets src$                                              | r           | Irr        | C2             | -   | _   |              | _ | _ | - | 2       | 5      |

|                 |                                                              | lr          | Irr        | C5             | _   |     |              |   |   |   | 2       | 9      |

|                 |                                                              | Irr         | r          | D2             | _   |     |              |   |   |   | 2       | 5      |

| LDCI dst, src   | $dst \leftarrow src$                                         | lr          | Irr        | C3             | -   | _   | _            | _ | _ | _ | 2       | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr         | lr         | D3             | _   |     |              |   |   |   | 2       | 9      |

| LDE dst, src    | $dst \leftarrow src$                                         | r           | Irr        | 82             | -   | _   |              | _ | _ | - | 2       | 5      |

|                 |                                                              | Irr         | r          | 92             | _   |     |              |   |   |   | 2       | 5      |

| LDEI dst, src   | $dst \gets src$                                              | lr          | Irr        | 83             | -   | _   |              | _ | _ | - | 2       | 9      |

|                 | r ← r + 1<br>rr ← rr + 1                                     | Irr         | lr         | 93             | _   |     |              |   |   |   | 2       | 9      |

| LDWX dst, src   | $dst \leftarrow src$                                         | ER          | ER         | 1FE8           | _   | _   | . <u> </u>   | _ | _ | _ | 5       | 4      |

| LDX dst, src    | $dst \gets src$                                              | r           | ER         | 84             | -   | _   |              | _ | _ | - | 3       | 2      |

|                 |                                                              | lr          | ER         | 85             | _   |     |              |   |   |   | 3       | 3      |

|                 |                                                              | R           | IRR        | 86             | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                              | IR          | IRR        | 87             | _   |     |              |   |   |   | 3       | 5      |

|                 |                                                              | r           | X(rr)      | 88             | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                              | X(rr)       | r          | 89             | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                              | ER          | r          | 94             | _   |     |              |   |   |   | 3       | 2      |

|                 |                                                              | ER          | lr         | 95             | _   |     |              |   |   |   | 3       | 3      |

|                 |                                                              | IRR         | R          | 96             |     |     |              |   |   |   | 3       | 4      |

|                 |                                                              | IRR         | IR         | 97             | _   |     |              |   |   |   | 3       | 5      |

|                 |                                                              | ER          | ER         | E8             | _   |     |              |   |   |   | 4       | 2      |

|                 |                                                              | ER          | IM         | E9             | _   |     |              |   |   |   | 4       | 2      |

| LEA dst, X(src) | $dst \gets src + X$                                          | r           | X(r)       | 98             | -   | _   |              | _ | _ | - | 3       | 3      |

|                 |                                                              | rr          | X(rr)      | 99             |     |     |              |   |   |   | 3       | 5      |

| MULT dst        | dst[15:0] ←<br>dst[15:8] * dst[7:0]                          | RR          |            | F4             | -   | _   |              | _ | _ | - | 2       | 8      |

| NOP             | No operation                                                 |             |            | 0F             | -   | _   |              | _ | _ | - | 1       | 2      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resul | t of the c | operation.     |     |     | ese<br>et to |   | 0 |   |         |        |

# Table 115. eZ8 CPU Instruction Summary (Continued)

|                   |                               |         | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                 |  |  |

|-------------------|-------------------------------|---------|------------------------|----------------------|-------|---------------------------------------------------------------------------------|--|--|

| Symbol            | Parameter                     | Minimum | Typical                | Maximum              | Units | Conditions                                                                      |  |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4     | _                      | _                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |  |  |

| IIH               | Input Leakage<br>Current      | -       | <u>+</u> 0.002         | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |  |  |

| IIL               | Input Leakage<br>Current      | -       | <u>+</u> 0.007         | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |  |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -       | -                      | <u>+</u> 5           | μA    |                                                                                 |  |  |

| I <sub>LED</sub>  | Controlled Current            | 1.8     | 3                      | 4.5                  | mA    | {AFS2,AFS1} = {0,0}                                                             |  |  |

|                   | Drive                         | 2.8     | 7                      | 10.5                 | mA    | {AFS2,AFS1} = {0,1}                                                             |  |  |

|                   |                               | 7.8     | 13                     | 19.5                 | mA    | {AFS2,AFS1} = {1,0}                                                             |  |  |

|                   |                               | 12      | 20                     | 30                   | mA    | {AFS2,AFS1} = {1,1}                                                             |  |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -       | 8.0 <sup>2</sup>       | -                    | pF    |                                                                                 |  |  |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -       | 8.0 <sup>2</sup>       | _                    | pF    |                                                                                 |  |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -       | 9.5 <sup>2</sup>       | -                    | pF    |                                                                                 |  |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30      | 100                    | 350                  | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |  |  |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD     |                        |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |  |  |

### Table 118. DC Characteristics (Continued)

Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

# **On-Chip Peripheral AC and DC Electrical Characteristics**

# Table 122. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   |                                                                                                                | T <sub>A</sub> = - | 40 °C to +           | 105 °C       |          |                                                                                                       |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|--------------|----------|-------------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                                                                                      | Minimum            | Typical <sup>1</sup> | Maximum      | Units    | Conditions                                                                                            |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70         | V        | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65         | V        | $V_{DD} = V_{VBO}$                                                                                    |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75           | mV       |                                                                                                       |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | _                  | V <sub>SS</sub>      | -            | V        |                                                                                                       |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -            | μs       | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                                                             |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles                                                            |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | _            | μs       | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100          | ms       |                                                                                                       |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |              | ns       | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |

|                   | he typical column is from char are not tested in production.                                                   | acterization       | at 3.3 V and         | 30 °C. These | values a | re provided for design guidance                                                                       |

199

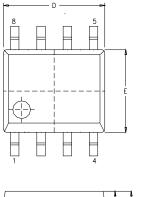

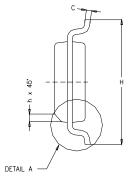

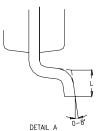

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIN | IETER                                                                               | INCH                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                               |  |  |  |

|--------|-------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MIN    | MAX                                                                                 | MIN                                                                                                                                                                                              | MAX                                                                                                                                                                                                                                                                                                                           |  |  |  |

| 1.55   | 1.73                                                                                | 0.061                                                                                                                                                                                            | 0.068                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.10   | 0.25                                                                                | 0.004                                                                                                                                                                                            | 0.010                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1.40   | 1.55                                                                                | 0.055                                                                                                                                                                                            | 0.061                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.36   | 0.48                                                                                | 0.014                                                                                                                                                                                            | 0.019                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.18   | 0.25                                                                                | 0.007                                                                                                                                                                                            | 0.010                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 4.80   | 4.98                                                                                | 0.189                                                                                                                                                                                            | 0.196                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 3.81   | 3.99                                                                                | 0.150                                                                                                                                                                                            | 0.157                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 1.27   | BSC                                                                                 | .050 BSC                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                               |  |  |  |

| 5.84   | 6.15                                                                                | 0.230                                                                                                                                                                                            | 0.242                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.25   | 0.40                                                                                | 0.010                                                                                                                                                                                            | 0.016                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 0.46   | 0.81                                                                                | 0.018                                                                                                                                                                                            | 0.032                                                                                                                                                                                                                                                                                                                         |  |  |  |

|        | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | 1.55     1.73       0.10     0.25       1.40     1.55       0.36     0.48       0.18     0.25       4.80     4.98       3.81     3.99       1.27     BSC       5.84     6.15       0.25     0.40 | MIN     MAX     MIN       1.55     1.73     0.061       0.10     0.25     0.004       1.40     1.55     0.055       0.36     0.48     0.014       0.18     0.25     0.007       4.80     4.98     0.189       3.81     3.99     0.150       1.27     BSC     .050       5.84     6.15     0.230       0.25     0.40     0.010 |  |  |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

| Part Number              | Flash      | RAM       | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|--------------------------|------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Z8 Encore! XP with 2     |            | l         |           |            |                        |                     |                |                     |

| Standard Temperatur      | e: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0213PB005SC           | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0213QB005SC           | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0213SB005SC           | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0213SH005SC           | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0213HH005SC           | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0213PH005SC           | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0213SJ005SC           | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0213HJ005SC           | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0213PJ005SC           | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatur      | re: -40 °C | to 105 °C | ;         |            |                        |                     |                |                     |

| Z8F0213PB005EC           | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0213QB005EC           | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0213SB005EC           | 2 KB       | 512 B     | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0213SH005EC           | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0213HH005EC           | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0213PH005EC           | 2 KB       | 512 B     | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0213SJ005EC           | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0213HJ005EC           | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0213PJ005EC           | 2 KB       | 512 B     | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lea | d-Free Pac | kaging    |           |            |                        |                     |                |                     |

| Jaquing<br>Trad<br>Z8 Encore! XP <sup>®</sup> F0823 S | Flash | W W W W W W W W W W W W W W W W W W W       | t I/O Lines | ∓<br>Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description                |

|-------------------------------------------------------|-------|---------------------------------------------|-------------|-----------------|------------------------|---------------------|----------------|----------------------------|

| Z8F08A28100KITG                                       |       | -                                           |             |                 | A Serie                | es De               | velo           | pment Kit (20- and 28-Pin) |

| Z8F04A28100KITG                                       |       | Z8 Enco                                     | re! XP      | F042            | A Serie                | es De               | velo           | pment Kit (20- and 28-Pin) |

| Z8F04A08100KITG                                       |       | Z8 Enco                                     | re! XP      | F042            | A Serie                | es De               | velo           | pment Kit (8-Pin)          |

| ZUSBSC00100ZACG                                       |       | USB Smart Cable Accessory Kit               |             |                 |                        |                     |                |                            |

| ZUSBOPTSC01ZACG                                       |       | Opto-Isolated USB Smart Cable Accessory Kit |             |                 |                        |                     |                |                            |

| ZENETSC0100ZACG                                       |       | Ethernet Smart Cable Accessory Kit          |             |                 |                        |                     |                |                            |

# **Customer Support**

For answers to technical questions about the product, documentation, or any other issues with Zilog's offerings, please visit Zilog's Knowledge Base at <u>http://www.zilog.com/kb</u>.

For any comments, detail technical questions, or reporting problems, please visit Zilog's Technical Support at <u>http://support.zilog.com</u>.