Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 28-DIP (0.600", 15.24mm)                                  |

| Supplier Device Package    | ·                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423pj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 13

## **Address Space**

The eZ8 CPU can access three distinct address spaces:

- The Register File contains addresses for the general-purpose registers and the eZ8 CPU, peripheral, and general-purpose I/O port control registers.

- The Program Memory contains addresses for all memory locations having executable code and/or data.

- The Data Memory contains addresses for all memory locations that contain data only.

These three address spaces are covered briefly in the following subsections. For more detailed information regarding the eZ8 CPU and its address space, refer to eZ8 CPU Core User Manual (UM0128) available for download at www.zilog.com.

## **Register File**

The Register File address space in the Z8 Encore! XP<sup>®</sup> MCU is 4 KB (4096 bytes). The Register File is composed of two sections: control registers and general-purpose registers. When instructions are executed, registers defined as sources are read, and registers defined as destinations are written. The architecture of the eZ8 CPU allows all general-purpose registers to function as accumulators, address pointers, index registers, stack areas, or scratch pad memory.

The upper 256 bytes of the 4 KB Register File address space are reserved for control of the eZ8 CPU, the on-chip peripherals, and the I/O ports. These registers are located at addresses from F00H to FFFH. Some of the addresses within the 256 B control register section are reserved (unavailable). Reading from a reserved Register File address returns an undefined value. Writing to reserved Register File addresses is not recommended and can produce unpredictable results.

The on-chip RAM always begins at address 000H in the Register File address space. Z8 Encore! XP F0823 Series devices contain 256 B-1 KB of on-chip RAM. Reading from Register File addresses outside the available RAM addresses (and not within the control register address space) returns an undefined value. Writing to these Register File addresses produces no effect.

## **Program Memory**

The eZ8 CPU supports 64 KB of Program Memory address space. Z8 Encore! XP F0823 Series devices contain 1 KB to 8 KB of on-chip Flash memory in the Program Memory address space. Reading from Program Memory addresses outside the available Flash

## Note:

This register is only reset during a Power-On Reset sequence. Other System Reset events do not affect it.

| Table 13. Power Control Register 0 (PWRCTL0) |  |

|----------------------------------------------|--|

| <b>č</b>                                     |  |

| BITS  | 7        | 6    | 5                      | 4   | 3        | 2   | 1    | 0        |

|-------|----------|------|------------------------|-----|----------|-----|------|----------|

| FIELD | Reserved | Rese | erved                  | VBO | Reserved | ADC | COMP | Reserved |

| RESET | 1        | 0    | 0                      | 0   | 0        | 0   | 0    | 0        |

| R/W   | R/W      | R/W  | /W R/W R/W R/W R/W R/W |     |          |     |      |          |

| ADDR  |          |      |                        | F8  | 0H       |     |      |          |

Reserved—Must be 1

Reserved-Must be 0

VBO—Voltage Brownout Detector Disable

This bit and the VBO\_AO Flash option bit must both enable the VBO for the VBO to be active.

0 = VBO enabled

1 = VBO disabled

ADC—Analog-to-Digital Converter Disable

0 = Analog-to-Digital Converter enabled

1 = Analog-to-Digital Converter disabled

COMP—Comparator Disable

0 =Comparator is enabled

1 =Comparator is disabled

Reserved-Must be 0

## **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6                       | 5   | 4            | 3     | 2        | 1        | 0    |  |

|-------|----------|-------------------------|-----|--------------|-------|----------|----------|------|--|

| FIELD | Reserved | T1I                     | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |  |

| RESET | 0        | 0 0 0 0 0 0 0           |     |              |       |          |          |      |  |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W |     |              |       |          |          |      |  |

| ADDR  |          | FC0H                    |     |              |       |          |          |      |  |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

## **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 35. Interrupt Request 1 Register (IRQ1)

| BITS  | 7     | 6                       | 5             | 4    | 3    | 2    | 1    | 0    |  |

|-------|-------|-------------------------|---------------|------|------|------|------|------|--|

| FIELD | PA7VI | PA6CI                   | PA5I          | PA4I | PA3I | PA2I | PA1I | PA0I |  |

| RESET | 0     | 0                       | 0 0 0 0 0 0 0 |      |      |      |      |      |  |

| R/W   | R/W   | R/W R/W R/W R/W R/W R/W |               |      |      |      |      |      |  |

| ADDR  |       | FC3H                    |               |      |      |      |      |      |  |

PA7VI—Port A7 Interrupt Request

0 = No interrupt request is pending for GPIO Port A

1 = An interrupt request from GPIO Port A

PA6CI—Port A6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator

1 = An interrupt request from GPIO Port A or Comparator

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin x

1 = An interrupt request from GPIO Port A pin x is awaiting service

where x indicates the specific GPIO Port pin number (0-5)

## **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 36) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL1 register clears indicating the timer interrupt is not because of an input capture event.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CAPTURE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is

| BITS  | 7   | 6 5 4 3 2 1 0              |  |       |      |  |  |  |  |

|-------|-----|----------------------------|--|-------|------|--|--|--|--|

| FIELD |     | PWML                       |  |       |      |  |  |  |  |

| RESET | 0   |                            |  |       |      |  |  |  |  |

| R/W   | R/W | /W R/W R/W R/W R/W R/W R/W |  |       |      |  |  |  |  |

| ADDR  |     |                            |  | F05H, | F0DH |  |  |  |  |

## Table 54. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## **Timer 0–1 Control Registers**

## Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input Capture event.

Table 55. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7       | 6          | 5                       | 4        | 3 | 2      | 1 | 0 |  |

|-------|---------|------------|-------------------------|----------|---|--------|---|---|--|

| FIELD | TMODEHI | TICONFIG   |                         | Reserved |   | INPCAP |   |   |  |

| RESET | 0       | 0          | 0                       | 0        | 0 | 0      | 0 | 0 |  |

| R/W   | R/W     | R/W        | R/W R/W R/W R/W R/W R/W |          |   |        |   |   |  |

| ADDR  |         | F06H, F0EH |                         |          |   |        |   |   |  |

#### TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value. See the TxCTL1 register description for more details.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

#### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

## **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

#### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

#### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1001 = Divide by 2

86

010 = Divide by 4 011 = Divide by 8 100 = Divide by 16 101 = Divide by 32 110 = Divide by 64 111 = Divide by 128

TMODE—Timer mode

This field along with the TMODEHI bit in TxCTL0 register determines the operating mode of the timer. TMODEHI is the most significant bit of the Timer mode selection value.

0000 = ONE-SHOT mode

0001 = CONTINUOUS mode

0010 = COUNTER mode

- 0011 = PWM SINGLE OUTPUT mode

- 0100 = CAPTURE mode

- 0101 = COMPARE mode

- 0110 = GATED mode

- 0111 = CAPTURE/COMPARE mode

- 1000 = PWM DUAL OUTPUT mode

- 1001 = CAPTURE RESTART mode

- 1010 = COMPARATOR COUNTER Mode

## **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

## **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

## **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte cannot contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

## **UART Data and Error Handling Procedure**

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

## **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data register (Table 63). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

## Table 63. UART Receive Data Register (U0RXD)

| BITS  | 7 | 6 5 4 3 2 1 0 |   |    |    |   |   |   |  |

|-------|---|---------------|---|----|----|---|---|---|--|

| FIELD |   | RXD           |   |    |    |   |   |   |  |

| RESET | Х | Х             | Х | Х  | Х  | Х | Х | Х |  |

| R/W   | R | R R R R R R R |   |    |    |   |   |   |  |

| ADDR  |   |               |   | F4 | 0H |   |   |   |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

## **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 64 and Table 65) identify the current UART operating configuration and status.

Table 64. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6             | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|---------------|----|----|------|------|-----|-----|

| FIELD | RDA | PE            | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0 0 0 0 1 1 X |    |    |      |      |     |     |

| R/W   | R   | R R R R R R R |    |    |      |      |     |     |

| ADDR  |     |               |    | F4 | 1H   |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty

1 = There is a byte in the UART Receive Data register

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred

1 = A parity error has occurred

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is

received and the UART Receive Data register has not been read. If the RDA bit is reset to 0, reading the UART Receive Data register clears this bit.

0 = No overrun error occurred

1 = An overrun error occurred

FE—Framing Error

This bit indicates that a framing error (no Stop bit following data reception) was detected. Reading the UART Receive Data register clears this bit.

0 = No framing error occurred

1 = A framing error occurred

#### BRKD-Break Detect

This bit indicates that a break occurred. If the data bits, parity/multiprocessor bit, and Stop bit(s) are all 0s this bit is set to 1. Reading the UART Receive Data register clears this bit.

0 = No break occurred

1 = A break occurred

TDRE—Transmitter Data Register Empty

This bit indicates that the UART Transmit Data register is empty and ready for additional data. Writing to the UART Transmit Data register resets this bit.

0 = Do not write to the UART Transmit Data register

1 = The UART Transmit Data register is ready to receive an additional byte to be transmitted

TXE—Transmitter Empty

This bit indicates that the transmit shift register is empty and character transmission is finished.

0 = Data is currently transmitting

1 = Transmission is complete

## $CTS \longrightarrow \overline{CTS}$ signal

When this bit is read it returns the level of the  $\overline{\text{CTS}}$  signal. This signal is active Low.

## **UART Status 1 Register**

This register contains multiprocessor control and status bits.

#### Table 65. UART Status 1 Register (U0STAT1)

| BITS  | 7 | 6 5 4 3 2 1 0        |  |    |    |  |  |  |  |

|-------|---|----------------------|--|----|----|--|--|--|--|

| FIELD |   | Reserved NEWFRM MPRX |  |    |    |  |  |  |  |

| RESET | 0 | 0 0 0 0 0 0 0        |  |    |    |  |  |  |  |

| R/W   | R | R R R R/W R/W R R    |  |    |    |  |  |  |  |

| ADDR  |   |                      |  | F4 | 4H |  |  |  |  |

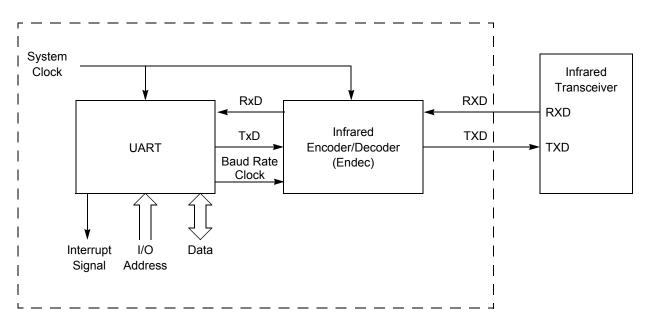

# **Infrared Encoder/Decoder**

Z8 Encore! XP<sup>®</sup> F0823 Series products contain a fully-functional, high-performance UART with Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

## Architecture

Figure 16 displays the architecture of the Infrared Endec.

Figure 16. Infrared Data Communication System Block Diagram

## Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared

| 150 |

|-----|

|-----|

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

## Table 97. Randomized Lot ID Locations (Continued)

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

## **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

## **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. The features of IPO include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

## Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

Power down this block for minimum system power. By default, the oscillator is configured through the Flash Option bits. However, the user code can override these trim values as described in Trim Bit Address Space on page 146.

Select one of the two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 165.

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

## Example 1

If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

## Table 103. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, s | src) |

|------------------------|-----|------|-----|-------------|------|

| Object Code            | 04  | 08   | 43  | (OPC src, d | lst) |

#### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

## Table 104. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 105.

| 184 |  |

|-----|--|

|-----|--|

| Assembly<br>Mnemonic                              | Symbolic Operation                                              | Address Mode<br>Opcode(s) |             | Fla        | igs |   |              | – Fetch | Instr |   |          |   |

|---------------------------------------------------|-----------------------------------------------------------------|---------------------------|-------------|------------|-----|---|--------------|---------|-------|---|----------|---|

|                                                   |                                                                 | dst                       | src         | (Hex)      | С   | Ζ | S            | v       | D     | н | Cycles C |   |

| OR dst, src                                       | $dst \gets dst \ OR \ src$                                      | r                         | r           | 42         | _   | * | *            | 0       | _     | _ | 2        | 3 |

|                                                   |                                                                 | r                         | lr          | 43         | -   |   |              |         |       |   | 2        | 4 |

|                                                   |                                                                 | R                         | R           | 44         | -   |   |              |         |       |   | 3        | 3 |

|                                                   |                                                                 | R                         | IR          | 45         | _   |   |              |         |       |   | 3        | 4 |

|                                                   |                                                                 | R                         | IM          | 46         | -   |   |              |         |       |   | 3        | 3 |

|                                                   |                                                                 | IR                        | IM          | 47         | -   |   |              |         |       |   | 3        | 4 |

| ORX dst, src                                      | $dst \gets dst \: OR \: src$                                    | ER                        | ER          | 48         | -   | * | *            | 0       | _     | - | 4        | 3 |

|                                                   |                                                                 | ER                        | IM          | 49         | _   |   |              |         |       |   | 4        | 3 |

| POP dstdst $\leftarrow$ @SPSP $\leftarrow$ SP + 1 |                                                                 | R                         |             | 50         | _   | _ | _            | _       | _     | _ | 2        | 2 |

|                                                   | $SP \leftarrow SP + 1$                                          | IR                        |             | 51         | -   |   |              |         |       |   | 2        | 3 |

| POPX dst                                          | dst ← @SP<br>SP ← SP + 1                                        | ER                        |             | D8         | _   | _ | _            | _       | _     | - | 3        | 2 |

| PUSH src                                          | $SP \leftarrow SP - 1$                                          | R                         |             | 70         | _   | _ | _            | _       | _     | _ | 2        | 2 |

|                                                   | $@SP \leftarrow src$                                            | IR                        |             | 71         | -   |   |              |         |       |   | 2        | 3 |

|                                                   |                                                                 | IM                        |             | IF70       | _   |   |              |         |       |   | 3        | 2 |

| PUSHX src                                         | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER                        |             | C8         | _   | _ | _            | _       | _     | _ | 3        | 2 |

| RCF                                               | C ← 0                                                           |                           |             | CF         | 0   | _ | -            | _       | _     | _ | 1        | 2 |

| RET                                               | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |                           |             | AF         | _   | - | -            | _       | _     | _ | 1        | 4 |

| RL dst                                            |                                                                 | R                         |             | 90         | *   | * | *            | *       | -     | _ | 2        | 2 |

|                                                   | C D7 D6 D5 D4 D3 D2 D1 D0<br>dst                                | IR                        |             | 91         | -   |   |              |         |       |   | 2        | 3 |

| RLC dst                                           |                                                                 | R                         |             | 10         | *   | * | *            | *       | _     | _ | 2        | 2 |

|                                                   | C D7 D6 D5 D4 D3 D2 D1 D0 dst                                   | IR                        |             | 11         | _   |   |              |         |       |   | 2        | 3 |

| Flags Notation:                                   | * = Value is a function of t<br>– = Unaffected<br>X = Undefined | he resu                   | It of the c | operation. |     |   | ese<br>et to |         | 0     |   |          |   |

## Table 115. eZ8 CPU Instruction Summary (Continued)

186

| Assembly<br>Mnemonic           | Symbolic Operation                                                                          | Address Mode<br>Opcode(s) |             | Fla       | igs |              |   | – Fetch | Instr |   |   |        |

|--------------------------------|---------------------------------------------------------------------------------------------|---------------------------|-------------|-----------|-----|--------------|---|---------|-------|---|---|--------|

|                                |                                                                                             | dst                       | src         | (Hex)     | С   | Ζ            | S | v       | D     | Н |   | Cycles |

| SUBX dst, src                  | $dst \gets dst - src$                                                                       | ER                        | ER          | 28        | *   | *            | * | *       | 1     | * | 4 | 3      |

|                                |                                                                                             | ER                        | IM          | 29        | _   |              |   |         |       |   | 4 | 3      |

| SWAP dst dst[7                 | $dst[7:4] \leftrightarrow dst[3:0]$                                                         | R                         |             | F0        | Х   | *            | * | Х       | _     | _ | 2 | 2      |

|                                |                                                                                             | IR                        |             | F1        | _   |              |   |         |       |   | 2 | 3      |

| TCM dst, src (NOT dst) AND src | r                                                                                           | r                         | 62          | _         | *   | *            | 0 | _       | _     | 2 | 3 |        |

|                                |                                                                                             | r                         | lr          | 63        |     |              |   |         |       |   | 2 | 4      |

|                                |                                                                                             | R                         | R           | 64        | _   |              |   |         |       |   | 3 | 3      |

|                                |                                                                                             | R                         | IR          | 65        |     |              |   |         |       |   | 3 | 4      |

|                                |                                                                                             | R                         | IM          | 66        | _   |              |   |         |       |   | 3 | 3      |

|                                |                                                                                             | IR                        | IM          | 67        | _   |              |   |         |       |   | 3 | 4      |

| TCMX dst, src (NOT dst) AND s  | (NOT dst) AND src                                                                           | ER                        | ER          | 68        | _   | *            | * | 0       | _     | _ | 4 | 3      |

|                                |                                                                                             | ER                        | IM          | 69        | _   |              |   |         |       |   | 4 | 3      |

| TM dst, src dst AND src        | dst AND src                                                                                 | r                         | r           | 72        | _   | *            | * | 0       | -     | - | 2 | 3      |

|                                |                                                                                             | r                         | lr          | 73        | _   |              |   |         |       |   | 2 | 4      |

|                                |                                                                                             | R                         | R           | 74        | _   |              |   |         |       |   | 3 | 3      |

|                                |                                                                                             | R                         | IR          | 75        |     |              |   |         |       |   | 3 | 4      |

|                                |                                                                                             | R                         | IM          | 76        |     |              |   |         |       |   | 3 | 3      |

|                                |                                                                                             | IR                        | IM          | 77        | _   |              |   |         |       |   | 3 | 4      |

| TMX dst, src dst ANE           | dst AND src                                                                                 | ER                        | ER          | 78        | _   | *            | * | 0       | _     | - | 4 | 3      |

|                                |                                                                                             | ER                        | IM          | 79        | _   |              |   |         |       |   | 4 | 3      |

| TRAP Vector                    | $SP \leftarrow SP - 2$<br>@SP ← PC<br>$SP \leftarrow SP - 1$<br>@SP ← FLAGS<br>PC ← @Vector |                           | Vector      | F2        | _   | -            | - | -       | _     | _ | 2 | 6      |

| WDT                            |                                                                                             |                           |             | 5F        | _   | _            | _ | _       | _     | - | 1 | 2      |

| Flags Notation:                | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                | f the resu                | It of the o | peration. |     | = Re<br>= Se |   |         | 0     |   |   |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

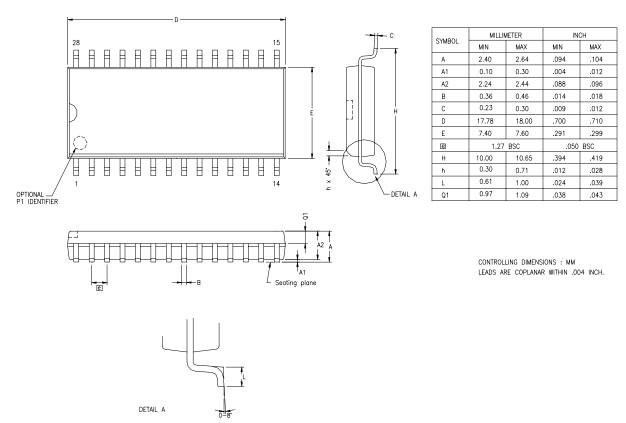

# Figure 41 displays the 28-pin Small Outline Integrated Circuit package (SOIC) available in Z8 Encore! XP F0823 Series devices.

Figure 41. 28-Pin Small Outline Integrated Circuit Package (SOIC)