Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | •                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | •                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423sb005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

## **Reset Controller**

Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series products can be reset using the  $\overline{RESET}$  pin, POR, WDT time-out, STOP mode exit, or Voltage Brownout warning signal. The  $\overline{RESET}$  pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

## **On-Chip Debugger**

Z8 Encore! XP F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD.

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 33. Trap and Interrupt Vectors in Order of Priority (Continued)

## Architecture

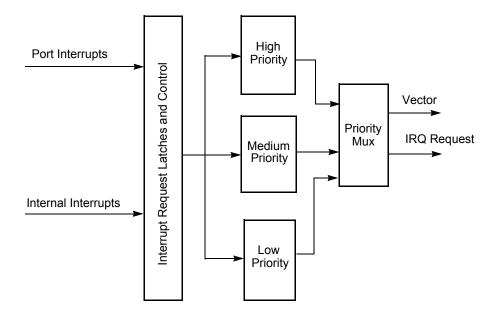

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

#### **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an Enable Interrupt (EI) instruction

- Execution of an Return from Interrupt (IRET) instruction

| BITS  | 7   | 6    | 5     | 4   | 3    | 2    | 1    | 0    |

|-------|-----|------|-------|-----|------|------|------|------|

| FIELD |     | Rese | erved |     | PC3I | PC2I | PC1I | PC0I |

| RESET | 0   | 0    | 0     | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W | R/W  | R/W   | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  |     | FC6H |       |     |      |      |      |      |

#### Table 36. Interrupt Request 2 Register (IRQ2)

Reserved—Must be 0

PCxI—Port C Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port C pin x

1 = An interrupt request from GPIO Port C pin x is awaiting service

where x indicates the specific GPIO Port C pin number (0-3)

### **IRQ0 Enable High and Low Bit Registers**

Table 37 describes the priority control for IRQ0. The IRQ0 Enable High and Low Bit registers (Table 38 and Table 39) form a priority encoded enabling for interrupts in the Interrupt Request 0 register. Priority is generated by setting bits in each register.

| -          |            |          |             |

|------------|------------|----------|-------------|

| IRQ0ENH[x] | IRQ0ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

|            |            |          |             |

where x indicates the register bits from 0–7.

#### Table 38. IRQ0 Enable High Bit Register (IRQ0ENH)

| BITS  | 7        | 6                           | 5     | 4      | 3      | 2        | 1        | 0      |

|-------|----------|-----------------------------|-------|--------|--------|----------|----------|--------|

| FIELD | Reserved | T1ENH                       | T0ENH | U0RENH | U0TENH | Reserved | Reserved | ADCENH |

| RESET | 0        | 0                           | 0     | 0      | 0      | 0        | 0        | 0      |

| R/W   | R/W      | R/W R/W R/W R/W R/W R/W R/W |       |        |        |          |          |        |

| ADDR  | FC1H     |                             |       |        |        |          |          |        |

Reserved—Must be 0

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

#### Table 39. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |

| ADDR  |          | FC2H  |              |               |               |          |          |        |

Reserved—0 when read

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

#### **IRQ1 Enable High and Low Bit Registers**

Table 40 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 41 and Table 42) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register.

|            |            | -        |             |

|------------|------------|----------|-------------|

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 40. IRQ1 Enable and Priority Encoding

where x indicates the register bits from 0–7.

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

## **Timer Operating Modes**

The timers can be configured to operate in the following modes:

#### **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control register to the start value before enabling ONE-SHOT mode. After starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode

- Set the prescale value

- Set the initial output level (High or Low) if using the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

# **Timer Control Register Definitions**

## Timer 0–1 High and Low Byte Registers

The Timer 0–1 High and Low Byte (TxH and TxL) registers (Table 49 and Table 50) contain the current 16-bit timer count value. When the timer is enabled, a read from TxH causes the value in TxL to be stored in a temporary holding register. A read from TxL always returns this temporary register when the timers are enabled. When the timer is disabled, reads from the TxL reads the register directly.

Writing to the Timer High and Low Byte registers while the timer is enabled is not recommended. There are no temporary holding registers available for write operations, so simultaneous 16-bit writes are not possible. If either the Timer High or Low Byte registers are written during counting, the 8-bit written value is placed in the counter (High or Low Byte) at the next clock edge. The counter continues counting from the new value.

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | TH         |     |     |     |     |     |     |     |

| RESET | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F00H, F08H |     |     |     |     |     |     |     |

Table 49. Timer 0–1 High Byte Register (TxH)

#### Table 50. Timer 0–1 Low Byte Register (TxL)

| BITS  | 7          | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | TL         |     |     |     |     |     |     |     |

| RESET | 0          | 0   | 0   | 0   | 0   | 0   | 0   | 1   |

| R/W   | R/W        | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | F01H, F09H |     |     |     |     |     |     |     |

TH and TL—Timer High and Low Bytes

These 2 bytes, {TH[7:0], TL[7:0]}, contain the current 16-bit timer count value

## **Timer Reload High and Low Byte Registers**

The Timer 0–1 Reload High and Low Byte (TxRH and TxRL) registers (Table 51 and Table 52) store a 16-bit Reload value, {TRH[7:0], TRL[7:0]}. Values written to the Timer Reload High Byte register are stored in a temporary holding register. When a write to the Timer Reload Low Byte register occurs, the temporary holding register value is written to the Timer High Byte register. This operation allows simultaneous updates of the 16-bit Timer Reload value.

#### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte cannot contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

#### 118

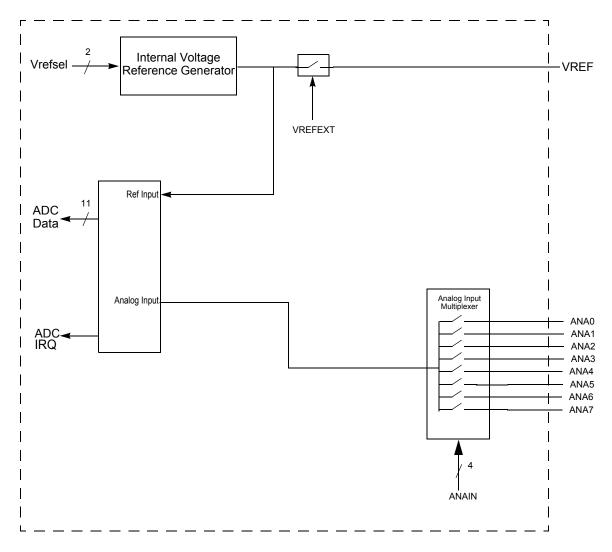

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

### **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

# **Oscillator Control**

Z8 Encore! XP<sup>®</sup> F0823 Series devices uses three possible clocking schemes, each user-selectable:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, Z8 Encore! XP F0823 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

## **System Clock Selection**

The oscillator control block selects from the available clocks. Table 101 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                 | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>           | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                   |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 101. Oscillator Configuration and Selection

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

|                   |                               |         | 40 °C to +<br>therwise | 105 °C<br>specified) |       |                                                                                 |  |

|-------------------|-------------------------------|---------|------------------------|----------------------|-------|---------------------------------------------------------------------------------|--|

| Symbol            | Parameter                     | Minimum | Typical                | Maximum              | Units | Conditions                                                                      |  |

| V <sub>OH2</sub>  | High Level Output<br>Voltage  | 2.4     | _                      | _                    | V     | I <sub>OH</sub> = -20 mA; V <sub>DD</sub> = 3.3 V<br>High Output Drive enabled. |  |

| IIH               | Input Leakage<br>Current      | -       | <u>+</u> 0.002         | <u>+</u> 5           | μA    | $V_{IN} = V_{DD}$<br>$V_{DD} = 3.3 V;$                                          |  |

| IIL               | Input Leakage<br>Current      | -       | <u>+</u> 0.007         | <u>+</u> 5           | μA    | $V_{IN} = V_{SS}$<br>$V_{DD} = 3.3 V;$                                          |  |

| I <sub>TL</sub>   | Tristate Leakage<br>Current   | -       | -                      | <u>+</u> 5           | μA    |                                                                                 |  |

| I <sub>LED</sub>  | Controlled Current            | 1.8     | 3                      | 4.5                  | mA    | {AFS2,AFS1} = {0,0}                                                             |  |

|                   | Drive                         | 2.8     | 7                      | 10.5                 | mA    | {AFS2,AFS1} = {0,1}                                                             |  |

|                   |                               | 7.8     | 13                     | 19.5                 | mA    | {AFS2,AFS1} = {1,0}                                                             |  |

|                   |                               | 12      | 20                     | 30                   | mA    | {AFS2,AFS1} = {1,1}                                                             |  |

| C <sub>PAD</sub>  | GPIO Port Pad<br>Capacitance  | -       | 8.0 <sup>2</sup>       | -                    | pF    |                                                                                 |  |

| C <sub>XIN</sub>  | XIN Pad<br>Capacitance        | -       | 8.0 <sup>2</sup>       | _                    | pF    |                                                                                 |  |

| C <sub>XOUT</sub> | XOUT Pad<br>Capacitance       | -       | 9.5 <sup>2</sup>       | -                    | pF    |                                                                                 |  |

| I <sub>PU</sub>   | Weak Pull-up<br>Current       | 30      | 100                    | 350                  | μA    | V <sub>DD</sub> = 3.0 V–3.6 V                                                   |  |

| V <sub>RAM</sub>  | RAM Data<br>Retention Voltage | TBD     |                        |                      | V     | Voltage at which RAM retains static values; no reading or writing is allowed.   |  |

#### Table 118. DC Characteristics (Continued)

Notes

1. This condition excludes all pins that have on-chip pull-ups, when driven Low.

2. These values are provided for design guidance only and are not tested in production.

200

|                                               | $T_A = -$ | = 2.7 V to<br>40 °C to +<br>otherwis | 105 °C  | Units  |                                                                                                                                                                   |  |

|-----------------------------------------------|-----------|--------------------------------------|---------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Parameter                                     | Minimum   | Typical                              | Maximum |        | Notes                                                                                                                                                             |  |

| Flash Byte Read Time                          | 100       | -                                    | -       | ns     |                                                                                                                                                                   |  |

| Flash Byte Program Time                       | 20        | -                                    | 40      | μs     |                                                                                                                                                                   |  |

| Flash Page Erase Time                         | 10        | -                                    | -       | ms     |                                                                                                                                                                   |  |

| Flash Mass Erase Time                         | 200       | -                                    | _       | ms     |                                                                                                                                                                   |  |

| Writes to Single Address<br>Before Next Erase | -         | -                                    | 2       |        |                                                                                                                                                                   |  |

| Flash Row Program Time                        | _         | -                                    | 8       | ms     | Cumulative program time for<br>single row cannot exceed limit<br>before next erase. This<br>parameter is only an issue<br>when bypassing the Flash<br>Controller. |  |

| Data Retention                                | 100       | _                                    | -       | years  | 25 °C                                                                                                                                                             |  |

| Endurance                                     | 10,000    | _                                    | _       | cycles | Program/erase cycles                                                                                                                                              |  |

#### Table 123. Flash Memory Electrical Characteristics and Timing

#### Table 124. Watchdog Timer Electrical Characteristics and Timing

|                     |                          | $T_A = -4$ | = 2.7 V to<br>40 °C to +<br>otherwise | 105 °C      |       |                                                                        |  |

|---------------------|--------------------------|------------|---------------------------------------|-------------|-------|------------------------------------------------------------------------|--|

| Symbol              | Parameter                | Minimum    | Minimum Typical Maximum L             |             | Units | Conditions                                                             |  |

| F <sub>WDT</sub>    | WDT Oscillator Frequency |            | 10                                    |             | kHz   |                                                                        |  |

| F <sub>WDT</sub>    | WDT Oscillator Error     |            |                                       | <u>+</u> 50 | %     |                                                                        |  |

| T <sub>WDTCAL</sub> | WDT Calibrated Timeout   | 0.98       | 1                                     | 1.02        | S     | V <sub>DD</sub> = 3.3 V;<br>T <sub>A</sub> = 30 °C                     |  |

|                     |                          | 0.70       | 1                                     | 1.30        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = 0 °C to 70 °C     |  |

|                     |                          | 0.50       | 1                                     | 1.50        | S     | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |  |

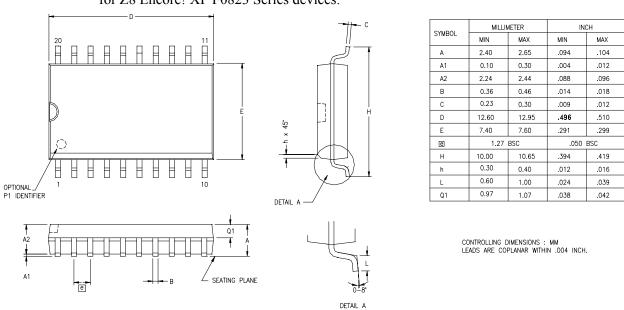

Figure 38 displays the 20-pin Small Outline Integrated Circuit Package (SOIC) available for Z8 Encore! XP F0823 Series devices.

Figure 38. 20-Pin Small Outline Integrated Circuit Package (SOIC)

Figure 39 displays the 20-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

Figure 39. 20-Pin Small Shrink Outline Package (SSOP)

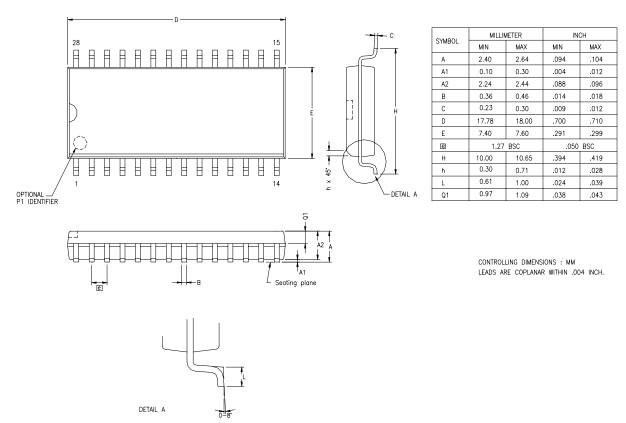

# Figure 41 displays the 28-pin Small Outline Integrated Circuit package (SOIC) available in Z8 Encore! XP F0823 Series devices.

Figure 41. 28-Pin Small Outline Integrated Circuit Package (SOIC)

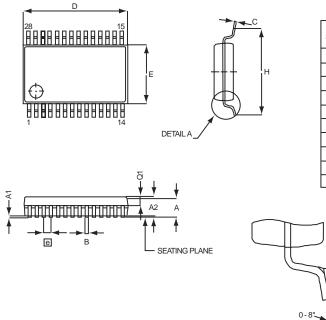

# Figure 42 displays the 28-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

|        |             | MILLIMETER | 2     | INCH       |       |       |  |  |

|--------|-------------|------------|-------|------------|-------|-------|--|--|

| SYMBOL | MIN NOM MAX |            | MAX   | MIN        | NOM   | MAX   |  |  |

| А      | 1.73        | 1.86       | 1.99  | 0.068      | 0.073 | 0.078 |  |  |

| A1     | 0.05        | 0.13       | 0.21  | 0.002      | 0.005 | 0.008 |  |  |

| A2     | 1.68        | 1.73       | 1.78  | 0.066      | 0.068 | 0.070 |  |  |

| В      | 0.25        |            | 0.38  | 0.010      |       | 0.015 |  |  |

| С      | 0.09        | -          | 0.20  | 0.004      | 0.006 | 0.008 |  |  |

| D      | 10.07       | 10.20      | 10.33 | 0.397      | 0.402 | 0.407 |  |  |

| E      | 5.20        | 5.30       | 5.38  | 0.205      | 0.209 | 0.212 |  |  |

| е      |             | 0.65 TYP   |       | 0.0256 TYP |       |       |  |  |

| н      | 7.65        | 7.80       | 7.90  | 0.301      | 0.307 | 0.311 |  |  |

| L      | 0.63        | 0.75       | 0.95  | 0.025      | 0.030 | 0.037 |  |  |

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

Figure 42. 28-Pin Small Shrink Outline Package (SSOP)

| Part Number                              | F           |           | ines      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|------------------------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part                                     | Flash       | RAM       | I/O Lines | Inter      | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |

| Z8 Encore! XP with 8                     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur                      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0813PB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu                       | re: -40 °C  | to 105 °( | 0         |            |                        |                     |                |                     |

| Z8F0813PB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |             |           |           |            |                        |                     |                |                     |

218

| Jaquing<br>Trad<br>Z8 Encore! XP <sup>®</sup> F0823 S | Flash | W W W W W W W W W W W W W W W W W W W                       | t I/O Lines | ∓<br>Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description |

|-------------------------------------------------------|-------|-------------------------------------------------------------|-------------|-----------------|------------------------|---------------------|----------------|-------------|

| Z8F08A28100KITG                                       |       | Z8 Encore! XP F082A Series Development Kit (20- and 28-Pin) |             |                 |                        |                     |                |             |

| Z8F04A28100KITG                                       |       | Z8 Encore! XP F042A Series Development Kit (20- and 28-Pin) |             |                 |                        |                     |                |             |

| Z8F04A08100KITG                                       |       | Z8 Encore! XP F042A Series Development Kit (8-Pin)          |             |                 |                        |                     |                |             |

| ZUSBSC00100ZACG                                       |       | USB Smart Cable Accessory Kit                               |             |                 |                        |                     |                |             |

| ZUSBOPTSC01ZACG                                       |       | Opto-Isolated USB Smart Cable Accessory Kit                 |             |                 |                        |                     |                |             |

| ZENETSC0100ZACG                                       |       | Ethernet Smart Cable Accessory Kit                          |             |                 |                        |                     |                |             |

timing 205 OCD commands execute instruction (12H) 161 read data memory (0DH) 160 read OCD control register (05H) 158 read OCD revision (00H) 158 read OCD status register (02H) 158 read program counter (07H) 159 read program memory (0BH) 160 read program memory CRC (0EH) 161 read register (09H) 159 read runtime counter (03H) 158 step instruction (10H) 161 stuff instruction (11H) 161 write data memory (0CH) 160 write OCD control register (04H) 158 write program counter (06H) 159 write program memory (0AH) 159 write register (08H) 159 on-chip debugger (OCD) 151 on-chip debugger signals 10 ONE-SHOT mode 84 opcode map abbreviations 189 cell description 188 first 190 second after 1FH 191 Operational Description 21, 31, 35, 53, 67, 87, 93, 113, 117, 127, 129, 141, 151, 165, 169 OR 177 ordering information 217 **ORX 178**

status register 163

# Ρ

p 173 packaging 20-pin PDIP 211, 212 20-pin SSOP 212, 215 28-pin PDIP 213 28-pin SOIC 214 8-pin PDIP 209 8-pin SOIC 210

PDIP 214, 215 part selection guide 2 PC 174 PDIP 214, 215 peripheral AC and DC electrical characteristics 199 pin characteristics 10 Pin Descriptions 7 polarity 173 POP 177 pop using extended addressing 177 **POPX 177** port availability, device 35 port input timing (GPIO) 203 port output timing, GPIO 204 power supply signals 10 power-down, automatic (ADC) 118 Power-on and Voltage Brownout electrical characteristics and timing 199 Power-On Reset (POR) 23 program control instructions 178 program counter 174 program memory 13 **PUSH 177** push using extended addressing 177 PUSHX 177 PWM mode 84, 85 PxADDR register 44

## R

PxCTL register 45

R 173 r 173 RA register address 173 RCF 176 receive IrDA data 115 receiving UART data-interrupt-driven method 98 receiving UART data-polled method 97 register 173 ADC control (ADCCTL) 122, 124 232