# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 7x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423sh005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Flash Information Area                                        | . 130 |

|---------------------------------------------------------------|-------|

| Operation                                                     | . 131 |

| Flash Operation Timing Using the Flash Frequency Registers    |       |

| Flash Code Protection Against External Access                 |       |

| Flash Code Protection Against Accidental Program and Erasure  |       |

| Byte Programming                                              |       |

| Page Erase                                                    |       |

| Mass Erase                                                    |       |

| Flash Controller Bypass                                       |       |

| Flash Controller Behavior in DEBUG Mode                       |       |

| Flash Control Register Definitions                            |       |

| Flash Control Register                                        |       |

| Flash Status Register                                         |       |

| Flash Page Select Register      Flash Sector Protect Register |       |

| Flash Frequency High and Low Byte Registers                   |       |

|                                                               |       |

| Flash Option Bits                                             |       |

| Operation                                                     |       |

| Option Bit Configuration By Reset                             |       |

| Option Bit Types                                              |       |

| Reading the Flash Information Page                            |       |

| Flash Option Bit Control Register Definitions                 |       |

| Trim Bit Address Register                                     | -     |

| Trim Bit Data Register                                        |       |

| Flash Option Bit Address Space                                |       |

| Flash Program Memory Address 0000H                            |       |

| Flash Program Memory Address 0001H                            |       |

| Trim Bit Address Space                                        |       |

| Trim Bit Address 0000H—Reserved                               |       |

| Trim Bit Address 0001H—Reserved                               |       |

| Trim Bit Address 0002H                                        |       |

| Trim Bit Address 00031—Reserved                               |       |

|                                                               |       |

| Zilog Calibration Data                                        |       |

| Serialization Data                                            |       |

| Randomized Lot Identifier                                     |       |

|                                                               |       |

| On-Chip Debugger                                              |       |

| Architecture                                                  | . 151 |

|                                                               |       |

#### viii

- 2.7 V to 3.6 V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore! XP<sup>®</sup> F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

# Block Diagram

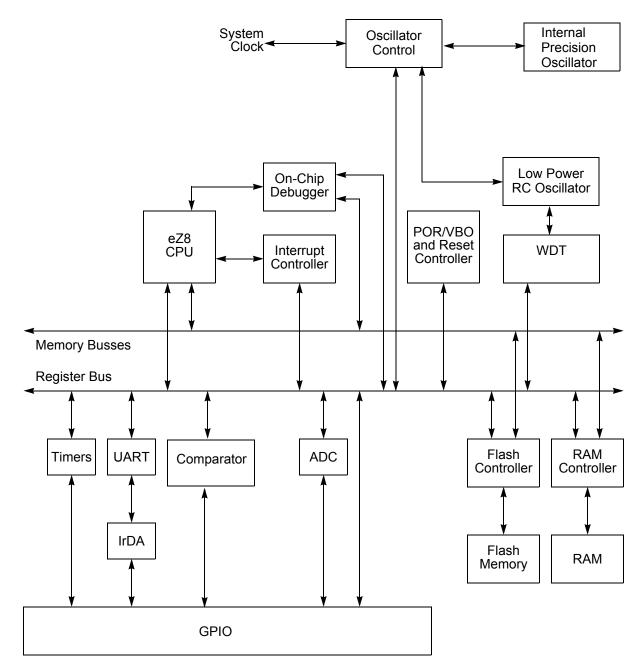

Figure 1 on page 3 displays the block diagram of the architecture of Z8 Encore! XP F0823 Series devices.

Figure 1. Z8 Encore! XP<sup>®</sup> F0823 Series Block Diagram

| Program Memory Address (Hex)                | Function                   |

|---------------------------------------------|----------------------------|

| 0002–0003                                   | Reset Vector               |

| 0004–0005                                   | WDT Interrupt Vector       |

| 0006–0007                                   | Illegal Instruction Trap   |

| 0008–0037                                   | Interrupt Vectors*         |

| 0038–003D                                   | Oscillator Fail Traps*     |

| 003E-03FF                                   | Program Memory             |

| ee Table 33 on page 54 for a list of the in | terrupt vectors and traps. |

Table 6. Z8 Encore! XP F0823 Series Program Memory Maps (Continued)

# **Data Memory**

Z8 Encore! XP<sup>®</sup> F0823 Series does not use the eZ8 CPU's 64 KB Data Memory address space.

# **Flash Information Area**

Table 7 lists the Z8 Encore! XP F0823 Series Flash Information Area. This 128 B Information Area is accessed by setting bit 7 of the Flash Page Select Register to 1. When access is enabled, the Flash Information Area is mapped into the Program Memory and overlays the 128 bytes at addresses FE00H to FF7FH. When the Information Area access is enabled, all reads from these Program Memory addresses return the Information Area data rather than the Program Memory data. Access to the Flash Information Area is read-only.

| Program Memory Address<br>(Hex) | Function                                                                                   |

|---------------------------------|--------------------------------------------------------------------------------------------|

| FE00–FE3F                       | Zilog Option Bits.                                                                         |

| FE40–FE53                       | Part Number.<br>20-character ASCII alphanumeric code<br>Left justified and filled with FH. |

| FE54–FE5F                       | Reserved.                                                                                  |

| FE60–FE7F                       | Zilog Calibration Data.                                                                    |

| FE80–FFFF                       | Reserved.                                                                                  |

Table 7. Z8 Encore! XP F0823 Series Flash Memory Information Area Map

## 17

# **Register Map**

Table 8 lists the address map for the Register File of the Z8 Encore! XP<sup>®</sup> F0823 Series devices. Not all devices and package styles in the Z8 Encore! XP F0823 Series support the ADC, or all GPIO ports. Consider registers for unimplemented peripherals as reserved.

| Address (Hex)  | Register Description              | Mnemonic      | Reset (Hex) | Page No   |

|----------------|-----------------------------------|---------------|-------------|-----------|

| General-Purpos | <u> </u>                          |               |             | 1 490 110 |

| Z8F0823/Z8F08  |                                   |               |             |           |

|                |                                   |               | ~~~         |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | _             | XX          |           |

| Z8F0423/Z8F04  |                                   |               |             |           |

| 000–3FF        | General-Purpose Register File RAM |               | XX          |           |

| 400–EFF        | Reserved                          | —             | XX          |           |

| Z8F0223/Z8F02  | 13 Devices                        |               |             |           |

| 000–1FF        | General-Purpose Register File RAM | —             | XX          |           |

| 200–EFF        | Reserved                          | —             | XX          |           |

| Z8F0123/Z8F01  | 13 Devices                        |               |             |           |

| 000–0FF        | General-Purpose Register File RAM | _             | XX          |           |

| 100–EFF        | Reserved                          | _             | XX          |           |

| Timer 0        |                                   |               |             |           |

| F00            | Timer 0 High Byte                 | ТОН           | 00          | 80        |

| F01            | Timer 0 Low Byte                  | TOL           | 01          | 80        |

| F02            | Timer 0 Reload High Byte          | TORH          | FF          | 81        |

| F03            | Timer 0 Reload Low Byte           | TORL          | FF          | 81        |

| F04            | Timer 0 PWM High Byte             | <b>T0PWMH</b> | 00          | 81        |

| F05            | Timer 0 PWM Low Byte              | TOPWML        | 00          | 82        |

| F06            | Timer 0 Control 0                 | TOCTLO        | 00          | 82        |

| F07            | Timer 0 Control 1                 | T0CTL1        | 00          | 83        |

| Timer 1        |                                   |               |             |           |

| F08            | Timer 1 High Byte                 | T1H           | 00          | 80        |

| F09            | Timer 1 Low Byte                  | T1L           | 01          | 80        |

| F0A            | Timer 1 Reload High Byte          | T1RH          | FF          | 81        |

| F0B            | Timer 1 Reload Low Byte           | T1RL          | FF          | 81        |

# Architecture

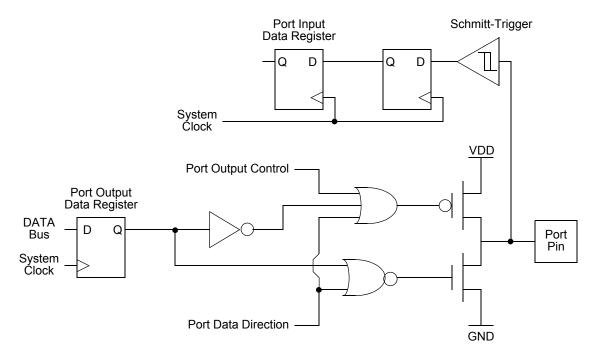

Figure 7 displays a simplified block diagram of a GPIO port pin. In this figure, the ability to accommodate alternate functions and variable port current drive strength is not displayed.

Figure 7. GPIO Port Pin Block Diagram

# **GPIO Alternate Functions**

Many of the GPIO port pins are used for general-purpose I/O and access to on-chip peripheral functions such as the timers and serial communication devices. The port A–D Alternate Function sub-registers configure these pins for either GPIO or alternate function operation. When a pin is configured for alternate function, control of the port pin direction (input/output) is passed from the Port A–D Data Direction registers to the alternate function assigned to this pin. Table 15 on page 39 lists the alternate functions possible with each port pin. The alternate function associated at a pin is defined through Alternate Function Sets sub-registers AFS1 and AFS2.

The crystal oscillator functionality is not controlled by the GPIO block. When the crystal oscillator is enabled in the oscillator control block, the GPIO functionality of PA0 and PA1 is overridden. In that case, those pins function as input and output for the crystal oscillator.

# **Interrupt Control Register Definitions**

For all interrupts other than the Watchdog Timer interrupt, the Primary Oscillator Fail Trap, and the Watchdog Timer Oscillator Fail Trap, the interrupt control registers enable individual interrupts, set interrupt priorities, and indicate interrupt requests.

## **Interrupt Request 0 Register**

The Interrupt Request 0 (IRQ0) register (Table 34) stores the interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ0 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 0 register to determine if any interrupt requests are pending.

| BITS  | 7        | 6    | 5   | 4            | 3     | 2        | 1        | 0    |

|-------|----------|------|-----|--------------|-------|----------|----------|------|

| FIELD | Reserved | T1I  | ТОІ | <b>U0RXI</b> | U0TXI | Reserved | Reserved | ADCI |

| RESET | 0        | 0    | 0   | 0            | 0     | 0        | 0        | 0    |

| R/W   | R/W      | R/W  | R/W | R/W          | R/W   | R/W      | R/W      | R/W  |

| ADDR  |          | FC0H |     |              |       |          |          |      |

Table 34. Interrupt Request 0 Register (IRQ0)

Reserved—Must be 0

T1I—Timer 1 Interrupt Request

- 0 = No interrupt request is pending for Timer 1

- 1 = An interrupt request from Timer 1 is awaiting service

T0I—Timer 0 Interrupt Request

- 0 = No interrupt request is pending for Timer 0

- 1 = An interrupt request from Timer 0 is awaiting service

U0RXI-UART 0 Receiver Interrupt Request

- 0 = No interrupt request is pending for the UART 0 receiver

- 1 = An interrupt request from the UART 0 receiver is awaiting service

U0TXI-UART 0 Transmitter Interrupt Request

- 0 = No interrupt request is pending for the UART 0 transmitter

- 1 = An interrupt request from the UART 0 transmitter is awaiting service

ADCI—ADC Interrupt Request

- 0 = No interrupt request is pending for the ADC

- 1 = An interrupt request from the ADC is awaiting service

Reserved—Must be 0

T1ENH—Timer 1 Interrupt Request Enable High Bit T0ENH—Timer 0 Interrupt Request Enable High Bit U0RENH—UART 0 Receive Interrupt Request Enable High Bit U0TENH—UART 0 Transmit Interrupt Request Enable High Bit ADCENH—ADC Interrupt Request Enable High Bit

#### Table 39. IRQ0 Enable Low Bit Register (IRQ0ENL)

| BITS  | 7        | 6     | 5            | 4             | 3             | 2        | 1        | 0      |  |

|-------|----------|-------|--------------|---------------|---------------|----------|----------|--------|--|

| FIELD | Reserved | T1ENL | <b>T0ENL</b> | <b>U0RENL</b> | <b>U0TENL</b> | Reserved | Reserved | ADCENL |  |

| RESET | 0        | 0     | 0            | 0             | 0             | 0        | 0        | 0      |  |

| R/W   | R        | R/W   | R/W          | R/W           | R/W           | R        | R        | R/W    |  |

| ADDR  |          | FC2H  |              |               |               |          |          |        |  |

Reserved—0 when read

T1ENL—Timer 1 Interrupt Request Enable Low Bit T0ENL—Timer 0 Interrupt Request Enable Low Bit U0RENL—UART 0 Receive Interrupt Request Enable Low Bit U0TENL—UART 0 Transmit Interrupt Request Enable Low Bit ADCENL—ADC Interrupt Request Enable Low Bit

### **IRQ1 Enable High and Low Bit Registers**

Table 40 describes the priority control for IRQ1. The IRQ1 Enable High and Low Bit registers (Table 41 and Table 42) form a priority encoded enabling for interrupts in the Interrupt Request 1 register. Priority is generated by setting bits in each register.

|            |            | -        |             |

|------------|------------|----------|-------------|

| IRQ1ENH[x] | IRQ1ENL[x] | Priority | Description |

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

| 1          | 1          | Level 3  | High        |

Table 40. IRQ1 Enable and Priority Encoding

where x indicates the register bits from 0–7.

#### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the hold-ing register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

#### **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

# **Infrared Encoder/Decoder**

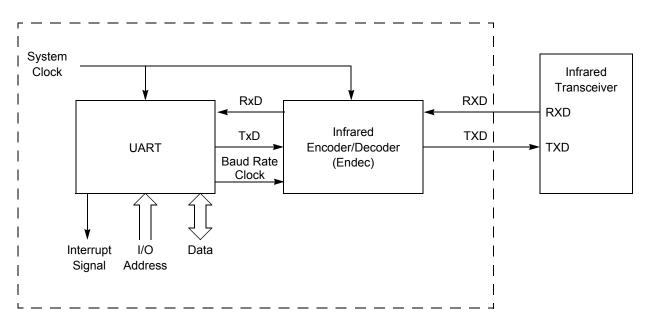

Z8 Encore! XP<sup>®</sup> F0823 Series products contain a fully-functional, high-performance UART with Infrared Encoder/Decoder (Endec). The Infrared Endec is integrated with an on-chip UART to allow easy communication between the Z8 Encore! XP and IrDA Physical Layer Specification, Version 1.3-compliant infrared transceivers. Infrared communication provides secure, reliable, low-cost, point-to-point communication between PCs, PDAs, cell phones, printers and other infrared enabled devices.

# Architecture

Figure 16 displays the architecture of the Infrared Endec.

Figure 16. Infrared Data Communication System Block Diagram

# Operation

When the Infrared Endec is enabled, the transmit data from the associated on-chip UART is encoded as digital signals in accordance with the IrDA standard and output to the infrared transceiver through the TXD pin. Similarly, data received from the infrared transceiver is passed to the Infrared Endec through the RXD pin, decoded by the Infrared

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP<sup>®</sup> F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

# Comparator

Z8 Encore! XP<sup>®</sup> F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The features of Comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see Power Control Register 0 on page 32.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts after comparator enabling. The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definitions**

### **Comparator Control Register**

The Comparator Control register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

#### Table 83. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | FFREQH |     |     |     |     |     |     |     |

| RESET | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | FFAH   |     |     |     |     |     |     |     |

FFREQH—Flash Frequency High Byte High byte of the 16-bit Flash Frequency value

### Table 84. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7      | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |  |

|-------|--------|------|---|---|---|---|---|---|--|--|--|

| FIELD | FFREQL |      |   |   |   |   |   |   |  |  |  |

| RESET | 0      |      |   |   |   |   |   |   |  |  |  |

| R/W   | R/W    |      |   |   |   |   |   |   |  |  |  |

| ADDR  |        | FFBH |   |   |   |   |   |   |  |  |  |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value

| 150 |

|-----|

|-----|

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

## Table 97. Randomized Lot ID Locations (Continued)

177

## Table 110. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |  |  |  |  |

|----------|----------|------------------------|--|--|--|--|

| SCF      | —        | Set Carry Flag         |  |  |  |  |

| SRP      | SrC      | Set Register Pointer   |  |  |  |  |

| STOP     | _        | STOP Mode              |  |  |  |  |

| WDT      | _        | Watchdog Timer Refresh |  |  |  |  |

## Table 111. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                    |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | SrC         | Push                                                                   |

| PUSHX    | SrC         | Push using Extended Addressing                                         |

# Table 112. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| СОМ      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

# UART Timing

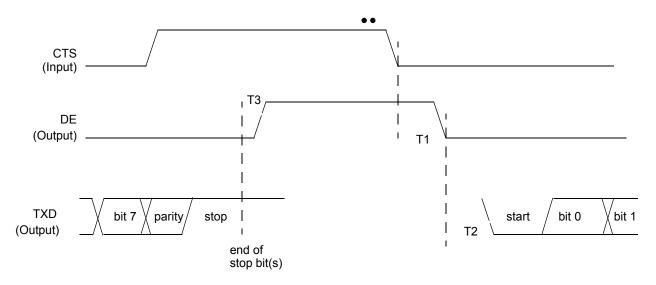

Figure 32 and Table 130 provide timing information for UART pins for the case where CTS is used for flow control. The CTS to DE assertion delay (T1) assumes the transmit data register has been loaded with data prior to CTS assertion.

Figure 32. UART Timing With CTS

|                |                                                   | Delay (ns)        |                                |  |  |

|----------------|---------------------------------------------------|-------------------|--------------------------------|--|--|

| Parameter      | Abbreviation                                      | Minimum           | Maximum                        |  |  |

| UART           |                                                   |                   |                                |  |  |

| T <sub>1</sub> | CTS Fall to DE output delay                       | 2 * XIN<br>period | 2 * XIN period<br>+ 1 bit time |  |  |

| T <sub>2</sub> | DE assertion to TXD falling edge (start bit) dela | y ± 5             |                                |  |  |

| T <sub>3</sub> | End of Stop Bit(s) to DE deassertion delay        | ± 5               |                                |  |  |

#### Table 130. UART Timing With CTS

| Part Number                              | F                                   |            | /O Lines | nterrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

|------------------------------------------|-------------------------------------|------------|----------|-----------|------------------------|---------------------|----------------|---------------------|--|--|

| Part                                     | Flash                               | RAM        | 10 L     | Inter     | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |  |  |

| Z8 Encore! XP with 1                     |                                     | , 10-Bit A | Analog   | j-to-D    | igital C               | onve                | erter          |                     |  |  |

| Standard Temperatur                      | Standard Temperature: 0 °C to 70 °C |            |          |           |                        |                     |                |                     |  |  |

| Z8F0123PB005SC                           | 1 KB                                | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005SC                           | 1 KB                                | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005SC                           | 1 KB                                | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005SC                           | 1 KB                                | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005SC                           | 1 KB                                | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005SC                           | 1 KB                                | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005SC                           | 1 KB                                | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005SC                           | 1 KB                                | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005SC                           | 1 KB                                | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperatur                      | e: -40 °C                           | to 105 °C  | ;        |           |                        |                     |                |                     |  |  |

| Z8F0123PB005EC                           | 1 KB                                | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005EC                           | 1 KB                                | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005EC                           | 1 KB                                | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005EC                           | 1 KB                                | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005EC                           | 1 KB                                | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005EC                           | 1 KB                                | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005EC                           | 1 KB                                | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005EC                           | 1 KB                                | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005EC                           | 1 KB                                | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Replace C with G for Lead-Free Packaging |                                     |            |          |           |                        |                     |                |                     |  |  |

223

| Jagen<br>N<br>Za Encorel XP <sup>®</sup> E0823 S | Flash                                                                                                                                | W W W W W W W W W W W W W W W W W W W       | I/O Lines | ∓<br>Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description                |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------|-----------------|------------------------|---------------------|----------------|----------------------------|

| Z8F08A28100KITG                                  | 8 Encore! XP <sup>®</sup> F0823 Series Development Kit<br>8F08A28100KITG Z8 Encore! XP F082A Series Development Kit (20- and 28-Pin) |                                             |           |                 |                        |                     |                |                            |

| Z8F04A28100KITG                                  |                                                                                                                                      | Z8 Enco                                     | re! XP    | F042            | A Serie                | es De               | velo           | pment Kit (20- and 28-Pin) |

| Z8F04A08100KITG                                  |                                                                                                                                      | Z8 Enco                                     | re! XP    | F042            | A Serie                | es De               | velo           | pment Kit (8-Pin)          |

| ZUSBSC00100ZACG                                  |                                                                                                                                      | USB Smart Cable Accessory Kit               |           |                 |                        |                     |                |                            |

| ZUSBOPTSC01ZACG                                  |                                                                                                                                      | Opto-Isolated USB Smart Cable Accessory Kit |           |                 |                        |                     |                |                            |

| ZENETSC0100ZACG                                  | Ethernet Smart Cable Accessory Kit                                                                                                   |                                             |           |                 |                        |                     |                |                            |

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

235

reset in STOP mode 89 time-out response 88 Watchdog Timer Control Register (WDTCTL) 90 WDTCTL register 90, 128, 167 WDTH register 91 WDTL register 91 WDTU register 91 working register 173 working register pair 173

# Χ

X 173 XOR 178 XORX 178

# Ζ

Z8 Encore! block diagram 3 features 1 part selection guide 2