### Zilog - Z8F0423SJ005SC Datasheet

#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 22                                                        |

| Program Memory Size        | 4KB (4K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 8x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0423sj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

## **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

## **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

### **CAPTURE/COMPARE Mode**

0 = Counting is started on the first rising edge of the Timer Input signal. The current count is captured on subsequent rising edges of the Timer Input signal.

1 = Counting is started on the first falling edge of the Timer Input signal. The current count is captured on subsequent falling edges of the Timer Input signal.

### **PWM DUAL OUTPUT Mode**

0 = Timer Output is forced Low (0) and Timer Output Complement is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload. When enabled, the Timer Output Complement is forced Low (0) upon PWM count match and forced High (1) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to High (1).

1 = Timer Output is forced High (1) and Timer Output Complement is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload. When enabled, the Timer Output Complement is forced High (1) upon PWM count match and forced Low (0) upon Reload. The PWMD field in TxCTL0 register is a programmable delay to control the number of cycles time delay before the Timer Output and the Timer Output Complement is forced to Low (0).

### **CAPTURE RESTART Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

### **COMPARATOR COUNTER Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

**Caution:** When the Timer Output alternate function TxOUT on a GPIO port pin is enabled, Tx-OUT changes to whatever state the TPOL bit is in. The timer does not need to be enabled for that to happen. Also, the port data direction sub register is not needed to be set to output on TxOUT. Changing the TPOL bit with the timer enabled and running does not immediately change the TxOUT.

### PRES—Prescale value.

The timer input clock is divided by  $2^{PRES}$ , where PRES can be set from 0 to 7. The prescaler is reset each time the Timer is disabled. This reset ensures proper clock division each time the Timer is restarted.

000 = Divide by 1 001 = Divide by 2

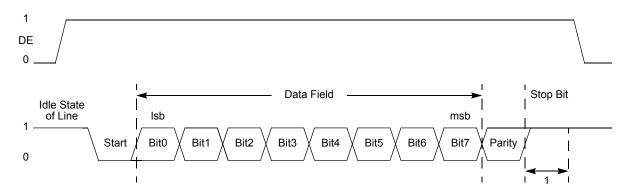

### **External Driver Enable**

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

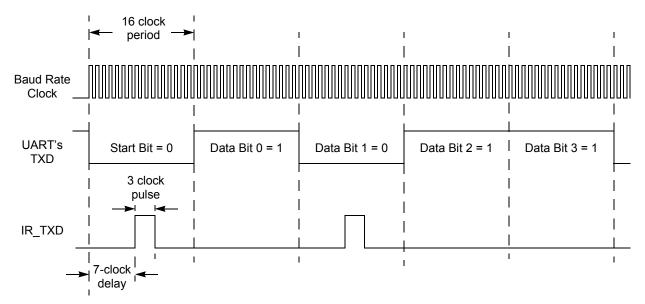

### **Transmitting IrDA Data**

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

## Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flowchart in Figure 21 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

| Table 78. Flash Code Pr | rotection Using  | the Flash O | ntion Bits |

|-------------------------|------------------|-------------|------------|

|                         | olection bailing | the mash o  |            |

| FWP | Flash Code Protection Description                                                                                                                                                              |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled for all of Flash Program Memory. In user code programming, Page Erase, and Mass Erase are all disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase, and Mass Erase are enabled for all of Flash Program Memory.                                                                                                           |

### Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to prevent accidental program or erasure of the Flash memory. To program or erase the Flash memory, first write the Page Select Register with the target page. Unlock the Flash Controller by making two consecutive writes to the Flash Control register with the values 73H and 8CH, sequentially. The Page Select Register must be rewritten with the same page previously stored there. If the two Page Select writes do not match, the controller reverts to a locked state. If the two writes match, the selected page becomes active. For more details, see Figure 21.

After unlocking a specific page, you can enable either Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the Flash Control register locks the Flash Controller. Mass Erase is not allowed in the user code but only in through the Debug Port.

After unlocking a specific page, you can also write to any byte on that page. After a byte is written, the page remains unlocked, allowing for subsequent writes to other bytes on the same page. Further writes to the Flash Control Register cause the active page to revert to a locked state.

### **Sector Based Flash Protection**

The final protection mechanism is implemented on a per-sector basis. The Flash memories of Z8 Encore! XP devices are divided into maximum number of 8 sectors. A sector is 1/8 of the total size of the Flash memory, unless this value is smaller than the page size, in which case the sector and page sizes are equal.

The Sector Protect Register controls the protection state of each Flash sector. This register is shared with the Page Select Register. It is accessed by writing 73H followed by 5EH to the Flash controller. The next write to the Flash Control Register targets the Sector Protect Register.

The Sector Protect Register is initialized to 0 on reset, putting each sector into an unprotected state. When a bit in the Sector Protect Register is written to 1, the corresponding sector can no longer be written or erased by the CPU. External Flash programming through the OCD or via the Flash Controller Bypass mode are unaffected. After

### Table 83. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7      | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|--------|-----|-----|-----|-----|-----|-----|-----|

| FIELD | FFREQH |     |     |     |     |     |     |     |

| RESET | 0      | 0   | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W    | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | FFAH   |     |     |     |     |     |     |     |

FFREQH—Flash Frequency High Byte High byte of the 16-bit Flash Frequency value

### Table 84. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7      | 6    | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|--------|------|---|---|---|---|---|---|

| FIELD | FFREQL |      |   |   |   |   |   |   |

| RESET | 0      |      |   |   |   |   |   |   |

| R/W   | R/W    |      |   |   |   |   |   |   |

| ADDR  |        | FFBH |   |   |   |   |   |   |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

### Flash Program Memory Address 0001H

### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6           | 5            | 4        | 3   | 2    | 1     | 0   |

|------------|----------------------|-------------|--------------|----------|-----|------|-------|-----|

| FIELD      |                      | Reserved    |              | XTLDIS   |     | Rese | erved |     |

| RESET      | U                    | U           | U            | U        | U   | U    | U     | U   |

| R/W        | R/W                  | R/W         | R/W          | R/W      | R/W | R/W  | R/W   | R/W |

| ADDR       | Program Memory 0001H |             |              |          |     |      |       |     |

| Note:    = | Inchanged b          | V Reset R/M | = Read/Write | <b>`</b> |     |      |       |     |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

• **Read Program Memory CRC (0EH)**—The Read Program Memory Cyclic Redundancy Check (CRC) command computes and returns the CRC of Program Memory using the 16-bit CRC-CCITT polynomial. If the device is not in DEBUG mode, this command returns FFFFH for the CRC value. Unlike most other OCD Read commands, there is a delay from issuing of the command until the OCD returns the data. The OCD reads the Program Memory, calculates the CRC value, and returns the result. The delay is a function of the Program Memory size and is approximately equal to the system clock period multiplied by the number of bytes in the Program Memory.

```

DBG \leftarrow 0EH

DBG \rightarrow CRC[15:8]

DBG \rightarrow CRC[7:0]

```

• Step Instruction (10H)—The Step Instruction command steps one assembly instruction at the current Program Counter (PC) location. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

DBG  $\leftarrow$  10H

• Stuff Instruction (11H)—The Stuff Instruction command steps one assembly instruction and allows specification of the first byte of the instruction. The remaining 0-4 bytes of the instruction are read from Program Memory. This command is useful for stepping over instructions where the first byte of the instruction has been overwritten by a Breakpoint. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, the OCD ignores this command.

```

DBG \leftarrow 11H

DBG \leftarrow opcode[7:0]

```

• Execute Instruction (12H)—The Execute Instruction command allows sending an entire instruction to be executed to the eZ8 CPU. This command can also step over breakpoints. The number of bytes to send for the instruction depends on the opcode. If the device is not in DEBUG mode or the Flash Read Protect Option bit is enabled, this command reads and discards one byte.

```

DBG \leftarrow 12H

DBG \leftarrow 1-5 byte opcode

```

## **On-Chip Debugger Control Register Definitions**

### **OCD Control Register**

The OCD Control register controls the state of the OCD. This register is used to enter or exit DEBUG mode and to enable the BRK instruction. It also resets Z8 Encore!  $XP^{\mbox{\ensuremath{\mathbb{R}}}}$  F0823 Series device.

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

### **Clock Failure Detection and Recovery**

### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

## **Assembly Language Syntax**

For proper instruction execution, eZ8 CPU assembly language syntax requires that the operands be written as 'destination, source'. After assembly, the object code usually has the operands in the order 'source, destination', but ordering is opcode-dependent. The following instruction examples illustrate the format of some basic assembly instructions and the resulting object code produced by the assembler. You must follow this binary format if you prefer manual program coding or intend to implement your own assembler.

### Example 1

If the contents of Registers 43H and 08H are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 103. Assembly Language Syntax Example 1

| Assembly Language Code | ADD | 43H, | 08H | (ADD dst, s  | rc) |

|------------------------|-----|------|-----|--------------|-----|

| Object Code            | 04  | 08   | 43  | (OPC src, da | st) |

### Example 2

In general, when an instruction format requires an 8-bit register address, that address can specify any register location in the range 0–255 or, using Escaped Mode Addressing, a Working Register R0–R15. If the contents of Register 43H and Working Register R8 are added and the result is stored in 43H, the assembly syntax and resulting object code is:

### Table 104. Assembly Language Syntax Example 2

| Assembly Language Code | ADD | 43H, | R8 | (ADD dst, src) |

|------------------------|-----|------|----|----------------|

| Object Code            | 04  | E8   | 43 | (OPC src, dst) |

See the device-specific Product Specification to determine the exact register file range available. The register file size varies, depending on the device type.

## eZ8 CPU Instruction Notation

In the eZ8 CPU Instruction Summary and Description sections, the operands, condition codes, status flags, and address modes are represented by a notational shorthand that is described in Table 105.

178

Table 112. Logical Instructions (Continued)

| Mnemonic | Operands | Instruction                                    |

|----------|----------|------------------------------------------------|

| ORX      | dst, src | Logical OR using Extended Addressing           |

| XOR      | dst, src | Logical Exclusive OR                           |

| XORX     | dst, src | Logical Exclusive OR using Extended Addressing |

### Table 113. Program Control Instructions

| Mnemonic | Operands        | Instruction                   |

|----------|-----------------|-------------------------------|

| BRK      | _               | On-Chip Debugger Break        |

| BTJ      | p, bit, src, DA | Bit Test and Jump             |

| BTJNZ    | bit, src, DA    | Bit Test and Jump if Non-Zero |

| BTJZ     | bit, src, DA    | Bit Test and Jump if Zero     |

| CALL     | dst             | Call Procedure                |

| DJNZ     | dst, src, RA    | Decrement and Jump Non-Zero   |

| IRET     | _               | Interrupt Return              |

| JP       | dst             | Jump                          |

| JP cc    | dst             | Jump Conditional              |

| JR       | DA              | Jump Relative                 |

| JR cc    | DA              | Jump Relative Conditional     |

| RET      | —               | Return                        |

| TRAP     | vector          | Software Trap                 |

### Table 114. Rotate and Shift Instructions

| Mnemonic | Operands | Instruction                |

|----------|----------|----------------------------|

| BSWAP    | dst      | Bit Swap                   |

| RL       | dst      | Rotate Left                |

| RLC      | dst      | Rotate Left through Carry  |

| RR       | dst      | Rotate Right               |

| RRC      | dst      | Rotate Right through Carry |

| 184 |  |

|-----|--|

|-----|--|

| Assembly        | Symbolic Operation                                              | Address Mode<br>Opcode(s) |     |       | Flags |   |   |                                |   |   | - Fetch | Inetr |  |  |

|-----------------|-----------------------------------------------------------------|---------------------------|-----|-------|-------|---|---|--------------------------------|---|---|---------|-------|--|--|

| Mnemonic        |                                                                 | dst                       | src | (Hex) | С     | Ζ | S | v                              | D | н | Cycles  |       |  |  |

| OR dst, src     | $dst \gets dst \ OR \ src$                                      | r                         | r   | 42    | _     | * | * | 0                              | _ | _ | 2       | 3     |  |  |

|                 |                                                                 | r                         | lr  | 43    | -     |   |   |                                |   |   | 2       | 4     |  |  |

|                 |                                                                 | R                         | R   | 44    | -     |   |   |                                |   |   | 3       | 3     |  |  |

|                 |                                                                 | R                         | IR  | 45    | _     |   |   |                                |   |   | 3       | 4     |  |  |

|                 |                                                                 | R                         | IM  | 46    | -     |   |   |                                |   |   | 3       | 3     |  |  |

|                 |                                                                 | IR                        | IM  | 47    | -     |   |   |                                |   |   | 3       | 4     |  |  |

| ORX dst, src    | $dst \gets dst \: OR \: src$                                    | ER                        | ER  | 48    | -     | * | * | 0                              | _ | _ | 4       | 3     |  |  |

|                 |                                                                 | ER                        | IM  | 49    | _     |   |   |                                |   |   | 4       | 3     |  |  |

| POP dst         | dst ← @SP                                                       | R                         |     | 50    | _     | _ |   | _                              | _ | _ | 2       | 2     |  |  |

|                 | $SP \leftarrow SP + 1$                                          | IR                        |     | 51    | -     |   |   |                                |   |   | 2       | 3     |  |  |

| POPX dst        | dst ← @SP<br>SP ← SP + 1                                        | ER                        |     | D8    | _     | _ | _ | _                              | _ | - | 3       | 2     |  |  |

| PUSH src        | $SP \leftarrow SP - 1$<br>@SP $\leftarrow$ src                  | R                         |     | 70    | _     | _ | _ | _                              | - | _ | 2       | 2     |  |  |

|                 |                                                                 | IR                        |     | 71    | -     |   |   |                                |   |   | 2       | 3     |  |  |

|                 |                                                                 | IM                        |     | IF70  | _     |   |   |                                |   |   | 3       | 2     |  |  |

| PUSHX src       | $SP \leftarrow SP - 1$<br>@SP ← src                             | ER                        |     | C8    | _     | _ | _ | _                              | _ | _ | 3       | 2     |  |  |

| RCF             | C ← 0                                                           |                           |     | CF    | 0     | _ | - | _                              | _ | _ | 1       | 2     |  |  |

| RET             | $PC \leftarrow @SP$<br>$SP \leftarrow SP + 2$                   |                           |     | AF    | _     | - | - | _                              | _ | _ | 1       | 4     |  |  |

| RL dst          |                                                                 | R                         |     | 90    | *     | * | * | *                              | - | _ | 2       | 2     |  |  |

|                 | C D7 D6 D5 D4 D3 D2 D1 D0<br>dst                                | IR                        |     | 91    | -     |   |   |                                |   |   | 2       | 3     |  |  |

| RLC dst         |                                                                 | R                         |     | 10    | *     | * | * | *                              | _ | _ | 2       | 2     |  |  |

|                 | C D7D6D5D4D3D2D1D0                                              | IR                        |     | 11    | _     |   |   |                                |   |   | 2       | 3     |  |  |

| Flags Notation: | * = Value is a function of t<br>– = Unaffected<br>X = Undefined |                           |     |       |       |   |   | 0 = Reset to 0<br>1 = Set to 1 |   |   |         |       |  |  |

### Table 115. eZ8 CPU Instruction Summary (Continued)

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

192

### Table 119. Power Consumption

|                           |                                                                               | V <sub>DI</sub>      | <sub>o</sub> = 2.7 V to 3 | 3.6 V                |       |                                                                   |  |

|---------------------------|-------------------------------------------------------------------------------|----------------------|---------------------------|----------------------|-------|-------------------------------------------------------------------|--|

|                           |                                                                               |                      | Maximum <sup>2</sup>      | Maximum <sup>3</sup> | -     |                                                                   |  |

| Symbol                    | Parameter                                                                     | Typical <sup>1</sup> | Std Temp                  | Ext Temp             | Units | Conditions                                                        |  |

| I <sub>DD</sub> Stop      | Supply Current in STOP<br>Mode                                                | 0.1                  | 2                         | 7.5                  | μA    | No peripherals enabled. All pins driven to $V_{DD}$ or $V_{SS}$ . |  |

| I <sub>DD</sub> Halt      | Supply Current in HALT<br>Mode (with all<br>peripherals disabled)             | 35                   | 55                        | 65                   | μA    | 32 kHz                                                            |  |

|                           |                                                                               | 520                  | 630                       | 700                  | μA    | 5.5 MHz                                                           |  |

| I <sub>DD</sub>           | Supply Current in<br>ACTIVE Mode (with all<br>peripherals disabled)           | 2.8                  | 4.5                       | 4.8                  | mA    | 32 kHz                                                            |  |

|                           |                                                                               | 4.5                  | 5.2                       | 5.2                  | mA    | 5.5 MHz                                                           |  |

| I <sub>DD</sub> WDT       | Watchdog Timer Supply<br>Current                                              | 0.9                  | 1.0                       | 1.1                  | μA    |                                                                   |  |

| I <sub>DD</sub> IPO       | Internal Precision<br>Oscillator Supply<br>Current                            | 350                  | 500                       | 550                  | μA    |                                                                   |  |

| I <sub>DD</sub> VBO       | Voltage Brownout<br>Supply Current                                            | 50                   |                           |                      | μA    | For 20-/28-pin devices (VBO only); see Note 4                     |  |

|                           |                                                                               |                      |                           |                      |       | For 8-pin devices; See<br>Note 4                                  |  |

| I <sub>DD</sub> ADC       | Analog-to-Digital<br>Converter Supply<br>Current (with External<br>Reference) | 2.8                  | 3.1                       | 3.2                  | mA    | 32 kHz                                                            |  |

|                           |                                                                               | 3.1                  | 3.6                       | 3.7                  | mA    | 5.5 MHz                                                           |  |

|                           |                                                                               | 3.3                  | 3.7                       | 3.8                  | mA    | 10 MHz                                                            |  |

|                           |                                                                               | 3.7                  | 4.2                       | 4.3                  | mA    | 20 MHz                                                            |  |

| I <sub>DD</sub><br>ADCRef | ADC Internal Reference<br>Supply Current                                      | 0                    |                           |                      | μA    | See Note 4                                                        |  |

| I <sub>DD</sub> CMP       | Comparator supply<br>Current                                                  | 150                  | 180                       | 190                  | μA    | See Note 4                                                        |  |

| Part Number                                                       | E     |       | /O Lines | nterrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |  |

|-------------------------------------------------------------------|-------|-------|----------|-----------|------------------------|---------------------|----------------|---------------------|--|--|

| Part                                                              | Flash | RAM   | ĬÕ L     | Inter     | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |  |  |

| Z8 Encore! XP with 1 KB Flash, 10-Bit Analog-to-Digital Converter |       |       |          |           |                        |                     |                |                     |  |  |

| Standard Temperature: 0 °C to 70 °C                               |       |       |          |           |                        |                     |                |                     |  |  |

| Z8F0123PB005SC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005SC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005SC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005SC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005SC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005SC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005SC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005SC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005SC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Extended Temperature: -40 °C to 105 °C                            |       |       |          |           |                        |                     |                |                     |  |  |

| Z8F0123PB005EC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |  |

| Z8F0123QB005EC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |  |

| Z8F0123SB005EC                                                    | 1 KB  | 256 B | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |  |

| Z8F0123SH005EC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |  |

| Z8F0123HH005EC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |  |

| Z8F0123PH005EC                                                    | 1 KB  | 256 B | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |  |

| Z8F0123SJ005EC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |  |

| Z8F0123HJ005EC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |  |

| Z8F0123PJ005EC                                                    | 1 KB  | 256 B | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |  |

| Replace C with G for Lead-Free Packaging                          |       |       |          |           |                        |                     |                |                     |  |  |

223

Index

**COMPARE 84** compare - extended addressing 175 COMPARE mode 84 compare with carry 175 compare with carry - extended addressing 175 complement 177 complement carry flag 176 condition code 173 continuous conversion (ADC) 120 CONTINUOUS mode 84 control register definition, UART 104 Control Registers 13, 17 **COUNTER modes 84** CP 175 **CPC 175 CPCX 175** CPU and peripheral overview 4 CPU control instructions 176 **CPX 175** Customer Support 237

## D

DA 173, 175 data memory 15 DC characteristics 194 debugger, on-chip 151 **DEC 175** decimal adjust 175 decrement 175 decrement and jump non-zero 178 decrement word 175 **DECW 175** destination operand 174 device, port availability 35 DI 176 direct address 173 disable interrupts 176 **DJNZ 178** dst 174

## Ε

EI 176

electrical characteristics 193 ADC 201 flash memory and timing 200 GPIO input data sample timing 202 Watchdog Timer 200, 202 enable interrupt 176 ER 173 extended addressing register 173 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 174 eZ8 CPU instruction notation 172 eZ8 CPU instruction set 171 eZ8 CPU instruction set 171

## F

FCTL register 137, 143, 144 features, Z8 Encore! 1 first opcode map 190 FLAGS 174 flags register 174 flash controller 4 option bit address space 144 option bit configuration - reset 141 program memory address 0000H 144 program memory address 0001H 145 flash memory 129 arrangement 130 byte programming 135 code protection 133 configurations 129 control register definitions 137, 143 controller bypass 136 electrical characteristics and timing 200 flash control register 137, 143, 144 flash option bits 134 flash status register 137 flow chart 132 frequency high and low byte registers 139 mass erase 135 operation 131 operation timing 133

228

### Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

231

L LD 177 LDC 177 LDCI 176, 177 LDE 177 LDEI 176, 177 LDX 177 LEA 177 load 177 load constant 176 load constant to/from program memory 177 load constant with auto-increment addresses 177 load effective address 177 load external data 177 load external data to/from data memory and auto-increment addresses 176 load external to/from data memory and auto-increment addresses 177 load instructions 177 load using extended addressing 177 logical AND 177 logical AND/extended addressing 177 logical exclusive OR 178 logical exclusive OR/extended addressing 178 logical instructions 177 logical OR 177 logical OR/extended addressing 178 low power modes 31

## Μ

master interrupt enable 55 memory data 15 program 13 mode CAPTURE 84, 85 CAPTURE/COMPARE 85 CONTINUOUS 84 COUNTER 84 GATED 84 ONE-SHOT 84 PWM 84, 85 modes 84 MULT 175 multiply 175 MULTIPROCESSOR mode, UART 99

## Ν

NOP (no operation) 176 notation b 173 cc 173 DA 173 ER 173 IM 173 IR 173 Ir 173 **IRR 173** Irr 173 p 173 R 173 r 173 RA 173 RR 173 rr 173 vector 173 X 173 notational shorthand 173

### O OCD

architecture 151 auto-baud detector/generator 154 baud rate limits 155 block diagram 151 breakpoints 156 commands 157 control register 161 data format 154 DBG pin to RS-232 Interface 152 DEBUG mode 153 debugger break 178 interface 152 serial errors 155