# E·XFL

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813hh005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Pin Description**

Z8 Encore! XP<sup>®</sup> F0823 Series products are available in a variety of package styles and pin configurations. This chapter describes the signals and pin configurations available for each of the package styles. For information on physical package specifications, see Packaging on page 209.

## **Available Packages**

Table 2 lists the package styles that are available for each device in the Z8 Encore! XP F0823 Series product line.

| Part<br>Number | ADC | 8-pin<br>PDIP | 8-pin<br>SOIC | 20-pin<br>PDIP | 20-pin<br>SOIC | 20-pin<br>SSOP | 28-pin<br>PDIP | 28-pin<br>SOIC | 28-pin<br>SSOP | 8-pin QFN/<br>MLF-S |

|----------------|-----|---------------|---------------|----------------|----------------|----------------|----------------|----------------|----------------|---------------------|

| Z8F0823        | Yes | X             | X             | X              | X              | X              | X              | X              | X              | X                   |

| Z8F0813        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0423        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0413        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0223        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0213        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0123        | Yes | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

| Z8F0113        | No  | Х             | Х             | Х              | Х              | Х              | Х              | Х              | Х              | Х                   |

Table 2. Z8 Encore! XP F0823 Series Package Options

## **Pin Configurations**

Figure 2 through Figure 4 displays the pin configurations for all packages available in the Z8 Encore! XP F0823 Series. For description of signals, see Table 3. The analog input alternate functions (ANA*x*) are not available on the Z8F0x13 devices. The analog supply pins (AV<sub>DD</sub> and AV<sub>SS</sub>) are also not available on these parts, and are replaced by PB6 and PB7.

At reset, all pins of Ports A, B, and C default to an input state. In addition, any alternate functionality is not enabled, so the pins function as general-purpose input ports until programmed otherwise.

clock and reset signals, the required reset duration can be as short as three clock periods and as long as four. A reset pulse three clock cycles in duration might trigger a reset; a pulse four cycles in duration always triggers a reset.

While the RESET input pin is asserted Low, the Z8 Encore! XP F0823 Series devices remain in the Reset state. If the RESET pin is held Low beyond the System Reset timeout, the device exits the Reset state on the system clock rising edge following RESET pin deassertion. Following a System Reset initiated by the external RESET pin, the EXT status bit in the WDT Control (WDTCTL) register is set to 1.

#### **External Reset Indicator**

During System Reset or when enabled by the GPIO logic (see Port A–C Control Registers on page 44), the RESET pin functions as an open-drain (active Low) reset mode indicator in addition to the input functionality. This reset output feature allows an Z8 Encore! XP F0823 Series device to reset other components to which it is connected, even if that reset is caused by internal sources such as POR, VBO, or WDT events.

After an internal reset event occurs, the internal circuitry begins driving the  $\overline{\text{RESET}}$  pin Low. The  $\overline{\text{RESET}}$  pin is held Low by the internal circuitry until the appropriate delay listed in Table 9 has elapsed.

#### **On-Chip Debugger Initiated Reset**

A POR is initiated using the On-Chip Debugger by setting the RST bit in the OCD Control register. The OCD block is not reset but the rest of the chip goes through a normal system reset. The RST bit automatically clears during the System Reset. Following the System Reset, the POR bit in the Reset Status (RSTSTAT) register is set.

## **Stop Mode Recovery**

The device enters into STOP mode when eZ8 CPU executes a STOP instruction. For more details on STOP mode, see Low-Power Modes on page 31. During Stop Mode Recovery, the CPU is held in reset for 66 IPO cycles if the crystal oscillator is disabled or 5000 cycles if it is enabled. The SMR delay also included the time required to start up the IPO.

Stop Mode Recovery does not affect on-chip registers other than the Watchdog Timer Control register (WDTCTL) and the Oscillator Control register (OSCCTL). After any Stop Mode Recovery, the IPO is enabled and selected as the system clock. If another system clock source is required or IPO disabling is required, the Stop Mode Recovery code must reconfigure the oscillator control block such that the correct system clock source is enabled and selected.

The eZ8 CPU fetches the Reset vector at Program Memory addresses 0002H and 0003H and loads that value into the Program Counter. Program execution begins at the Reset

# **GPIO Interrupts**

Many of the GPIO port pins are used as interrupt sources. Some port pins are configured to generate an interrupt request on either the rising edge or falling edge of the pin input signal. Other port pin interrupt sources generate an interrupt when any edge occurs (both rising and falling). For more information about interrupts using the GPIO pins, see Interrupt Controller on page 53.

# **GPIO Control Register Definitions**

Four registers for each Port provide access to GPIO control, input data, and output data. Table 17 lists these Port registers. Use the Port A–D Address and Control registers together to provide access to sub-registers for Port configuration and control.

| Port Register<br>Mnemonic     | Port Register Name                                           |

|-------------------------------|--------------------------------------------------------------|

| PxADDR                        | Port A–C Address Register (Selects sub-registers)            |

| PxCTL                         | Port A–C Control Register (Provides access to sub-registers) |

| PxIN                          | Port A–C Input Data Register                                 |

| PxOUT                         | Port A–C Output Data Register                                |

| Port Sub-Register<br>Mnemonic | Port Register Name                                           |

| P <i>x</i> DD                 | Data Direction                                               |

| PxAF                          | Alternate Function                                           |

| PxOC                          | Output Control (Open-Drain)                                  |

| PxHDE                         | High Drive Enable                                            |

| PxSMRE                        | Stop Mode Recovery Source Enable                             |

| PxPUE                         | Pull-up Enable                                               |

| PxAFS1                        | Alternate Function Set 1                                     |

| PxAFS2                        | Alternate Function Set 2                                     |

#### Table 17. GPIO Port Registers and Sub-Registers

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled.

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

### Port A–C Pull-up Enable Sub-Registers

The Port A–C Pull-up Enable sub-register (Table 25) is accessed through the Port A–C Control register by writing 06H to the Port A–C Address register. Setting the bits in the Port A–C Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

Table 25. Port A–C Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |  |  |  |  |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|--|--|--|--|

| FIELD | PPUE7    | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |  |  |  |  |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |  |  |  |  |

| R/W   | R/W      | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |  |  |  |  |

| ADDR  | lf 06H i | If 06H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |  |  |  |  |  |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

### Port A–C Alternate Function Set 1 Sub-Registers

The Port A–C Alternate Function Set1 sub-register (Table 26) is accessed through the Port A–C Control register by writing 07H to the Port A–C Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 36.

Note:

*Alternate function selection on port pins must also be enabled as described in* Port A–C Alternate Function Sub-Registers *on page 45*.

| BITS  | 7    | 6 | 5 | 4  | 3        | 2 | 1 | 0 |

|-------|------|---|---|----|----------|---|---|---|

| FIELD | IRQE |   |   |    | Reserved |   |   |   |

| RESET | 0    | 0 | 0 | 0  | 0        | 0 | 0 | 0 |

| R/W   | R/W  | R | R | R  | R        | R | R | R |

| ADDR  |      |   |   | FC | FH       |   |   |   |

## Table 48. Interrupt Control Register (IRQCTL)

IRQE—Interrupt Request Enable

This bit is set to 1 by executing an EI (Enable Interrupts) or IRET (Interrupt Return) instruction, or by a direct register write of a 1 to this bit. It is reset to 0 by executing a DI instruction, eZ8 CPU acknowledgement of an interrupt request, reset or by a direct register write of a 0 to this bit.

0 = Interrupts are disabled

1 = Interrupts are enabled

Reserved—0 when read

timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Follow the steps below to configure a timer for COMPARE mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for Compare mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In COMPARE mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

$COMPARE Mode Time (s) = \frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### GATED Mode

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer Reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

# **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

### **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7 | 6 | 5 | 4  | 3  | 2 | 1 | 0 |

|-------|---|---|---|----|----|---|---|---|

| FIELD |   |   |   | Tک | (D |   |   |   |

| RESET | Х | Х | Х | Х  | Х  | Х | Х | Х |

| R/W   | W | W | W | W  | W  | W | W | W |

| ADDR  |   |   |   | F4 | 0H |   |   |   |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

#### 118

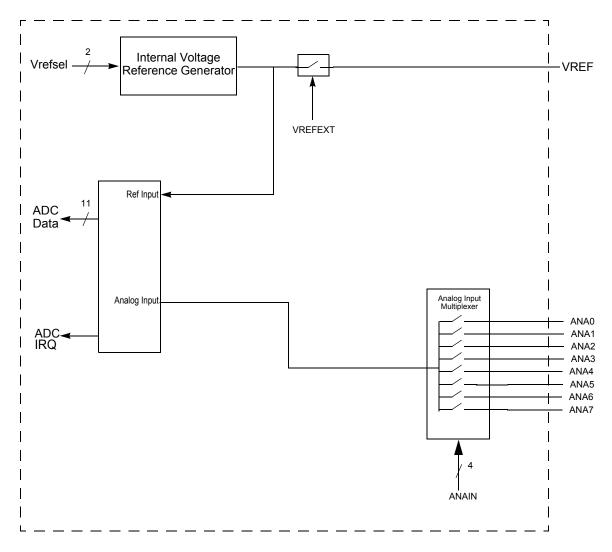

Figure 19. Analog-to-Digital Converter Block Diagram

## Operation

### **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

#### **Software Compensation Procedure**

The value read from the ADC high and low byte registers are uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following formula yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) * GAINCAL)/2^{16}$

where GAINCAL is the gain calibration byte, OFFCAL is the offset calibration byte and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. The OFFCAL value is in two's complement format, as are the compensated and uncompensated ADC values.

- Note: The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits. Also note that in the second term, the multiplication must be performed before the division by 2<sup>16</sup>. Otherwise, the second term evaluates to zero incorrectly.

- **Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

# **ADC Control Register Definitions**

The following sections define the ADC control registers.

### **ADC Control Register 0**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6       | 5      | 4    | 3          | 2   | 1   | 0   |  |  |

|-------|-----|---------|--------|------|------------|-----|-----|-----|--|--|

| FIELD | CEN | REFSELL | REFEXT | CONT | ANAIN[3:0] |     |     |     |  |  |

| RESET | 0   | 0       | 0      | 0    | 0 0 0      |     |     |     |  |  |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W        | R/W | R/W | R/W |  |  |

| ADDR  |     |         |        | F7   | 0H         |     |     |     |  |  |

Table 72. ADC Control Register 0 (ADCCTL0)

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

# Comparator

Z8 Encore! XP<sup>®</sup> F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The features of Comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

## Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see Power Control Register 0 on page 32.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts after comparator enabling. The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

## **Comparator Control Register Definitions**

#### **Comparator Control Register**

The Comparator Control register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

Reserved—0 when read

FSTAT—Flash Controller Status 000000 = Flash Controller locked 000001 = First unlock command received (73H written) 000010 = Second unlock command received (8CH written) 000011 = Flash Controller unlocked 000100 = Sector protect register selected 001xxx = Program operation in progress 010xxx = Page erase operation in progress 100xxx = Mass erase operation in progress

### Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Protect Register. Unless the Flash controller is unlocked and written with 5EH, writes to this address target the Flash Page Select Register.

The register is used to select one of the eight available Flash memory pages to be programmed or erased. Each Flash Page contains 512 bytes of Flash memory. During a Page Erase operation, all Flash memory having addresses with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6   | 5   | 4   | 3    | 2   | 1   | 0   |

|-------|---------|-----|-----|-----|------|-----|-----|-----|

| FIELD | INFO_EN |     |     |     | PAGE |     |     |     |

| RESET | 0       | 0   | 0   | 0   | 0    | 0   | 0   | 0   |

| R/W   | R/W     | R/W | R/W | R/W | R/W  | R/W | R/W | R/W |

| ADDR  |         |     |     | FF  | 9H   |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN—Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The Information Area is mapped into the Program Memory address space at addresses FE00H through FFFFH.

#### PAGE—Page Select

This 7-bit field identifies the Flash memory page for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE[6:0]. For the Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0.

Reserved— Altering this register may result in incorrect device operation.

## Trim Bit Address 0002H

#### Table 91. Trim Option Bits at 0002H (TIPO)

| BITS      | 7           | 6            | 5            | 4           | 3           | 2    | 1 | 0 |

|-----------|-------------|--------------|--------------|-------------|-------------|------|---|---|

| FIELD     |             |              |              | IPO_        | TRIM        |      |   |   |

| RESET     |             |              |              | ι           | J           |      |   |   |

| R/W       |             |              |              | R           | W           |      |   |   |

| ADDR      |             |              | Infor        | mation Page | e Memory 00 | )22H |   |   |

| Note: U = | Unchanged b | y Reset. R/W | = Read/Write | <b>.</b>    |             |      |   |   |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

## Trim Bit Address 0003H—Reserved

### Trim Bit Address 0004H—Reserved

# **Zilog Calibration Data**

## **ADC Calibration Data**

#### Table 92. ADC Calibration Bits

| BITS      | 7                                         | 6   | 5         | 4          | 3          | 2       | 1   | 0   |  |  |  |  |

|-----------|-------------------------------------------|-----|-----------|------------|------------|---------|-----|-----|--|--|--|--|

| FIELD     |                                           |     |           | ADC        | _CAL       |         |     |     |  |  |  |  |

| RESET     | U                                         | U   | U         | U          | U          | U       | U   | U   |  |  |  |  |

| R/W       | R/W                                       | R/W | R/W       | R/W        | R/W        | R/W     | R/W | R/W |  |  |  |  |

| ADDR      |                                           |     | Informati | on Page Me | mory 0060H | I-007DH |     |     |  |  |  |  |

| Note: U = | U = Unchanged by Reset. R/W = Read/Write. |     |           |            |            |         |     |     |  |  |  |  |

ADC CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Assembly        |                                                                                                                       | Addre       | ss Mode    | - Opcode(s) | Fla | ıgs |               |   |   |   | – Fetch | Instr. |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|-------------|------------|-------------|-----|-----|---------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                                                                                    | dst         | src        | (Hex)       | С   | z   | S             | v | D | Н |         | Cycles |

| HALT            | HALT Mode                                                                                                             |             |            | 7F          | -   | _   | -             | _ | - | - | 1       | 2      |

| INC dst         | $dst \leftarrow dst + 1$                                                                                              | R           |            | 20          | -   | *   | *             | _ | - | - | 2       | 2      |

|                 |                                                                                                                       | IR          |            | 21          | -   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | r           |            | 0E-FE       | _   |     |               |   |   |   | 1       | 2      |

| INCW dst        | $dst \leftarrow dst + 1$                                                                                              | RR          |            | A0          | -   | *   | *             | * | - | - | 2       | 5      |

|                 |                                                                                                                       | IRR         |            | A1          | -   |     |               |   |   |   | 2       | 6      |

| IRET            | $FLAGS \leftarrow @SP \\ SP \leftarrow SP + 1 \\ PC \leftarrow @SP \\ SP \leftarrow SP + 2 \\ IRQCTL[7] \leftarrow 1$ |             |            | BF          | *   | *   | *             | * | * | * | 1       | 5      |

| JP dst          | $PC \gets dst$                                                                                                        | DA          |            | 8D          | _   | _   | _             | _ | _ | _ | 3       | 2      |

|                 |                                                                                                                       | IRR         |            | C4          | -   |     |               |   |   |   | 2       | 3      |

| JP cc, dst      | if cc is true<br>PC $\leftarrow$ dst                                                                                  | DA          |            | 0D-FD       | -   | _   | -             | _ | _ | - | 3       | 2      |

| JR dst          | $PC \leftarrow PC + X$                                                                                                | DA          |            | 8B          | -   | _   | _             | _ | - | - | 2       | 2      |

| JR cc, dst      | if cc is true<br>PC $\leftarrow$ PC + X                                                                               | DA          |            | 0B-FB       | -   | _   | _             | _ | _ | - | 2       | 2      |

| LD dst, rc      | $dst \gets src$                                                                                                       | r           | IM         | 0C-FC       | -   | _   | -             | - | - | - | 2       | 2      |

|                 |                                                                                                                       | r           | X(r)       | C7          | -   |     |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | X(r)        | r          | D7          | _   |     |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | r           | lr         | E3          | _   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | R           | R          | E4          | _   |     |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | R           | IR         | E5          | _   |     |               |   |   |   | 3       | 4      |

|                 |                                                                                                                       | R           | IM         | E6          | -   |     |               |   |   |   | 3       | 2      |

|                 |                                                                                                                       | IR          | IM         | E7          | -   |     |               |   |   |   | 3       | 3      |

|                 |                                                                                                                       | lr          | r          | F3          | -   |     |               |   |   |   | 2       | 3      |

|                 |                                                                                                                       | IR          | R          | F5          | -   |     |               |   |   |   | 3       | 3      |

| Flags Notation: | * = Value is a function o<br>– = Unaffected<br>X = Undefined                                                          | f the resul | t of the o | peration.   |     |     | eset<br>et to |   | 0 |   |         |        |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

| Assembly        |                                                                  | Addre   | ss Mode     | - Opcode(s) | Fla | ıgs |              |   |   |   | – Fetch | Instr. |

|-----------------|------------------------------------------------------------------|---------|-------------|-------------|-----|-----|--------------|---|---|---|---------|--------|

| Mnemonic        | Symbolic Operation                                               | dst     | src         | (Hex)       | С   | Ζ   | S            | v | D | Н |         | Cycles |

| RR dst          |                                                                  | R       |             | E0          | *   | *   | *            | * | _ | - | 2       | 2      |

|                 | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C<br>dst                             | IR      |             | E1          | -   |     |              |   |   |   | 2       | 3      |

| RRC dst         |                                                                  | R       |             | C0          | *   | *   | *            | * | _ | - | 2       | 2      |

|                 | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR      |             | C1          | _   |     |              |   |   |   | 2       | 3      |

| SBC dst, src    | $dst \gets dst - src - C$                                        | r       | r           | 32          | *   | *   | *            | * | 1 | * | 2       | 3      |

|                 |                                                                  | r       | lr          | 33          | _   |     |              |   |   |   | 2       | 4      |

|                 |                                                                  | R       | R           | 34          |     |     |              |   |   |   | 3       | 3      |

|                 |                                                                  | R       | IR          | 35          | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                                  | R       | IM          | 36          |     |     |              |   |   |   | 3       | 3      |

|                 |                                                                  | IR      | IM          | 37          |     |     |              |   |   |   | 3       | 4      |

| SBCX dst, src   | $dst \gets dst - src - C$                                        | ER      | ER          | 38          | *   | *   | *            | * | 1 | * | 4       | 3      |

|                 |                                                                  | ER      | IM          | 39          | _   |     |              |   |   |   | 4       | 3      |

| SCF             | C ← 1                                                            |         |             | DF          | 1   | -   | -            | _ | _ | - | 1       | 2      |

| SRA dst         | <b>*</b> *                                                       | R       |             | D0          | *   | *   | *            | 0 | _ | - | 2       | 2      |

|                 | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR      |             | D1          |     |     |              |   |   |   | 2       | 3      |

| SRL dst         |                                                                  | R       |             | 1F C0       | *   | *   | 0            | * | _ | - | 3       | 2      |

|                 | dst                                                              | IR      |             | 1F C1       |     |     |              |   |   |   | 3       | 3      |

| SRP src         | $RP \leftarrow src$                                              |         | IM          | 01          | _   | _   | _            | _ | _ | _ | 2       | 2      |

| STOP            | STOP Mode                                                        |         |             | 6F          | _   | _   | _            | _ | _ | - | 1       | 2      |

| SUB dst, src    | $dst \gets dst - src$                                            | r       | r           | 22          | *   | *   | *            | * | 1 | * | 2       | 3      |

|                 |                                                                  | r       | lr          | 23          | _   |     |              |   |   |   | 2       | 4      |

|                 |                                                                  | R       | R           | 24          | _   |     |              |   |   |   | 3       | 3      |

|                 |                                                                  | R       | IR          | 25          | _   |     |              |   |   |   | 3       | 4      |

|                 |                                                                  | R       | IM          | 26          | -   |     |              |   |   |   | 3       | 3      |

|                 |                                                                  | IR      | IM          | 27          | _   |     |              |   |   |   | 3       | 4      |

| Flags Notation: | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu | It of the o | peration.   |     |     | ese<br>et to |   | 0 |   |         |        |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

| Abbreviation | Description                           | Abbreviation                                   | Description            |  |  |

|--------------|---------------------------------------|------------------------------------------------|------------------------|--|--|

| b            | Bit position                          | IRR                                            | Indirect Register Pair |  |  |

| СС           | Condition code                        | р                                              | Polarity (0 or 1)      |  |  |

| X            | 8-bit signed index or<br>displacement | r                                              | 4-bit Working Register |  |  |

| DA           | Destination address                   | R                                              | 8-bit register         |  |  |

| ER           | Extended Addressing register          | r1, R1, Ir1, Irr1, IR1,<br>rr1, RR1, IRR1, ER1 | Destination address    |  |  |

| IM           | Immediate data value                  | r2, R2, Ir2, Irr2, IR2,<br>rr2, RR2, IRR2, ER2 | Source address         |  |  |

| Ir           | Indirect Working Register             | RA                                             | Relative               |  |  |

| IR           | Indirect register                     | rr                                             | Working Register Pair  |  |  |

| Irr          | Indirect Working Register Pair        | RR                                             | Register Pair          |  |  |

## Table 116. Opcode Map Abbreviations

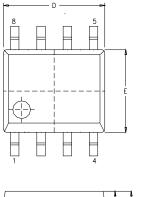

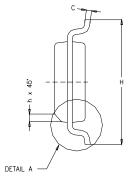

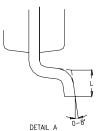

Figure 35 displays the 8-pin Small Outline Integrated Circuit package (SOIC) available for the Z8 Encore! XP F0823 Series devices.

e

| MILLIN | IETER                                                                               | INCH                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|--------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| MIN    | MAX                                                                                 | MIN                                                                                                                                                                                                                                                                          | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| 1.55   | 1.73                                                                                | 0.061                                                                                                                                                                                                                                                                        | 0.068                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.10   | 0.25                                                                                | 0.004                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.40   | 1.55                                                                                | 0.055                                                                                                                                                                                                                                                                        | 0.061                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.36   | 0.48                                                                                | 0.014                                                                                                                                                                                                                                                                        | 0.019                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.18   | 0.25                                                                                | 0.007                                                                                                                                                                                                                                                                        | 0.010                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 4.80   | 4.98                                                                                | 0.189                                                                                                                                                                                                                                                                        | 0.196                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 3.81   | 3.99                                                                                | 0.150                                                                                                                                                                                                                                                                        | 0.157                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 1.27   | BSC                                                                                 | .050 BSC                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| 5.84   | 6.15                                                                                | 0.230                                                                                                                                                                                                                                                                        | 0.242                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.25   | 0.40                                                                                | 0.010                                                                                                                                                                                                                                                                        | 0.016                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 0.46   | 0.81                                                                                | 0.018                                                                                                                                                                                                                                                                        | 0.032                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|        | MIN<br>1.55<br>0.10<br>1.40<br>0.36<br>0.18<br>4.80<br>3.81<br>1.27<br>5.84<br>0.25 | 1.55         1.73           0.10         0.25           1.40         1.55           0.36         0.48           0.18         0.25           4.80         4.98           3.81         3.99           1.27         BSC           5.84         6.15           0.25         0.40 | MIN         MAX         MIN           1.55         1.73         0.061           0.10         0.25         0.004           1.40         1.55         0.055           0.36         0.48         0.014           0.18         0.25         0.007           4.80         4.98         0.189           3.81         3.99         0.150           1.27         BSC         .050           5.84         6.15         0.230           0.25         0.40         0.010 |  |  |

CONTROLLING DIMENSIONS : MM LEADS ARE COPLANAR WITHIN .004 INCH.

A1 SEATING PLANE

Figure 35. 8-Pin Small Outline Integrated Circuit Package (SOIC)

|                                          |                                                                   |      |           |            |                        | annels              | ۷              |                     |

|------------------------------------------|-------------------------------------------------------------------|------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash                                                             | RAM  | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

| Z8 Encore! XP with 4                     | Z8 Encore! XP with 4 KB Flash, 10-Bit Analog-to-Digital Converter |      |           |            |                        |                     |                |                     |

| Standard Temperatur                      | Standard Temperature: 0 °C to 70 °C                               |      |           |            |                        |                     |                |                     |

| Z8F0423PB005SC                           | 4 KB                                                              | 1 KB | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005SC                           | 4 KB                                                              | 1 KB | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005SC                           | 4 KB                                                              | 1 KB | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005SC                           | 4 KB                                                              | 1 KB | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005SC                           | 4 KB                                                              | 1 KB | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005SC                           | 4 KB                                                              | 1 KB | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005SC                           | 4 KB                                                              | 1 KB | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005SC                           | 4 KB                                                              | 1 KB | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005SC                           | 4 KB                                                              | 1 KB | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C   |                                                                   |      |           |            |                        |                     |                |                     |

| Z8F0423PB005EC                           | 4 KB                                                              | 1 KB | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0423QB005EC                           | 4 KB                                                              | 1 KB | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0423SB005EC                           | 4 KB                                                              | 1 KB | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0423SH005EC                           | 4 KB                                                              | 1 KB | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0423HH005EC                           | 4 KB                                                              | 1 KB | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0423PH005EC                           | 4 KB                                                              | 1 KB | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0423SJ005EC                           | 4 KB                                                              | 1 KB | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0423HJ005EC                           | 4 KB                                                              | 1 KB | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0423PJ005EC                           | 4 KB                                                              | 1 KB | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |                                                                   |      |           |            |                        |                     |                |                     |

| mber                                     |          |            | S         | ts         | imers                  | 10-Bit A/D Channels | UART with IrDA | tion                |

|------------------------------------------|----------|------------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part Number                              | Flash    | RAM        | I/O Lines | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A            | UART w         | Description         |

| Z8 Encore! XP with 2                     | KB Flash | , 10-Bit A | Analog    | g-to-D     | igital C               | onve                | erter          |                     |

| Standard Temperature: 0 °C to 70 °C      |          |            |           |            |                        |                     |                |                     |

| Z8F0223PB005SC                           | 2 KB     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005SC                           | 2 KB     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005SC                           | 2 KB     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005SC                           | 2 KB     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005SC                           | 2 KB     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005SC                           | 2 KB     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005SC                           | 2 KB     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005SC                           | 2 KB     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005SC                           | 2 KB     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperature: -40 °C to 105 °C   |          |            |           |            |                        |                     |                |                     |

| Z8F0223PB005EC                           | 2 KB     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0223QB005EC                           | 2 KB     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0223SB005EC                           | 2 KB     | 512 B      | 6         | 12         | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0223SH005EC                           | 2 KB     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0223HH005EC                           | 2 KB     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0223PH005EC                           | 2 KB     | 512 B      | 16        | 18         | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0223SJ005EC                           | 2 KB     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0223HJ005EC                           | 2 KB     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0223PJ005EC                           | 2 KB     | 512 B      | 22        | 18         | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |          |            |           |            |                        |                     |                |                     |