Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | <u>.</u>                                                  |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            |                                                           |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SSOP (0.209", 5.30mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813hj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

- 2.7 V to 3.6 V operating voltage

- Up to thirteen 5 V-tolerant input pins

- 8-, 20-, and 28-pin packages

- 0 °C to +70 °C and -40 °C to +105 °C for operating temperature ranges

# **Part Selection Guide**

Table 1 lists the basic features and package styles available for each device within the Z8 Encore! XP<sup>®</sup> F0823 Series product line.

| Part<br>Number | Flash<br>(KB) | RAM<br>(B) | I/O  | ADC<br>Inputs | Packages             |

|----------------|---------------|------------|------|---------------|----------------------|

| Z8F0823        | 8             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0813        | 8             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0423        | 4             | 1024       | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0413        | 4             | 1024       | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0223        | 2             | 512        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0213        | 2             | 512        | 6–24 | 0             | 8-, 20-, and 28-pins |

| Z8F0123        | 1             | 256        | 6–22 | 4–8           | 8-, 20-, and 28-pins |

| Z8F0113        | 1             | 256        | 6–24 | 0             | 8-, 20-, and 28-pins |

Note:

\*Analog input alternate functions (ANA) are not available on the Z8F0x13 devices.

# **Signal Descriptions**

Table 3 lists the Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series signals. To determine the signals available for the specific package styles, see Pin Configurations on page 7.

### Table 3. Signal Descriptions

| Signal Mnemonic                                       | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C                                   | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                               | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                               | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                               | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| Note: PB6 and PB7 are<br>replaced by AV <sub>DI</sub> |         | /ailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                      |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                  | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                  | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                  | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                    | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                                |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                           | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT                                           | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                             | I       | Timer Input 0–1. These signals are used as the <u>capture</u> , gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                |

| Comparator                                            |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                             | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                  | 0       | Comparator Output. This is the output of the comparator.                                                                                                                                                                                                                                                |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

# Port A–C Address Registers

The Port A–C Address registers select the GPIO Port functionality accessible through the Port A–C Control registers. The Port A–C Address and Control registers combine to provide access to all GPIO Port controls (Table 18).

### Table 18. Port A–C GPIO Address Registers (PxADDR)

| BITS  | 7                | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------------------|-----------------------------|---|---|---|---|---|---|

| FIELD | PADDR[7:0]       |                             |   |   |   |   |   |   |

| RESET | 00H              |                             |   |   |   |   |   |   |

| R/W   | R/W              | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |

| ADDR  | FD0H, FD4H, FD8H |                             |   |   |   |   |   |   |

PADDR[7:0]—Port Address

The Port Address selects one of the sub-registers accessible through the Port Control register.

| PADDR[7:0] | Port Control Sub-register Accessible Using the Port A–C Control Registers      |

|------------|--------------------------------------------------------------------------------|

| 00H        | No function. Provides some protection against accidental Port reconfiguration. |

| 01H        | Data Direction.                                                                |

| 02H        | Alternate Function.                                                            |

| 03H        | Output Control (Open-Drain).                                                   |

| 04H        | High Drive Enable.                                                             |

| 05H        | Stop Mode Recovery Source Enable.                                              |

| 06H        | Pull-up Enable.                                                                |

| 07H        | Alternate Function Set 1.                                                      |

| 08H        | Alternate Function Set 2.                                                      |

| 09H–FFH    | No function.                                                                   |

# Port A–C Control Registers

The Port A–C Control registers set the GPIO port operation. The value in the corresponding Port A–C Address register determines which sub-register is read from or written to by a Port A–C Control register transaction (Table 19).

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period. If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

#### PWM Dual Output Mode

In PWM DUAL OUTPUT mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM Dual Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM Dual Output mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register

- Set the prescale value

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- 6. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to step 7. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 7. Write the UART Control 1 register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR mode is enabled,.

- 11. To transmit additional bytes, return to step 5.

### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow the steps below to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions, if MULTIPROCESSOR mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 7. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

Reserved—R/W bits must be 0 during writes; 0 when read.

NEWFRM—Status bit denoting the start of a new frame. Reading the UART Receive Data register resets this bit to 0.

0 = The current byte is not the first data byte of a new frame

1 = The current byte is the first data byte of a new frame

MPRX—Multiprocessor Receive

Returns the value of the most recent multiprocessor bit received. Reading from the UART Receive Data register resets this bit to 0.

### **UART Control 0 and Control 1 Registers**

The UART Control 0 and Control 1 registers (Table 66 and Table 67) configure the properties of the UART's transmit and receive operations. The UART Control registers must not be written while the UART is enabled.

#### Table 66. UART Control 0 Register (U0CTL0)

| BITS  | 7    | 6   | 5    | 4   | 3    | 2    | 1    | 0    |

|-------|------|-----|------|-----|------|------|------|------|

| FIELD | TEN  | REN | CTSE | PEN | PSEL | SBRK | STOP | LBEN |

| RESET | 0    | 0   | 0    | 0   | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W | R/W  | R/W | R/W  | R/W  | R/W  | R/W  |

| ADDR  | F42H |     |      |     |      |      |      |      |

TEN—Transmit Enable

This bit enables or disables the transmitter. The enable is also controlled by the  $\overline{\text{CTS}}$  signal and the CTSE bit. If the  $\overline{\text{CTS}}$  signal is low and the CTSE bit is 1, the transmitter is enabled.

0 = Transmitter disabled

1 = Transmitter enabled

REN—Receive Enable

This bit enables or disables the receiver.

0 =Receiver disabled

1 =Receiver enabled

CTSE—CTS Enable

$0 = \text{The }\overline{\text{CTS}}$  signal has no effect on the transmitter

1 = The UART recognizes the  $\overline{\text{CTS}}$  signal as an enable control from the transmitter

PEN—Parity Enable

This bit enables or disables parity. Even or odd is determined by the PSEL bit.

0 =Parity is disabled

1 = The transmitter sends data with an additional parity bit and the receiver receives an additional parity bit

The baud rate error relative to the acceptable baud rate is calculated using the following equation:

UART Baud Rate Error (%) =  $100 \times \left(\frac{\text{Actual Data Rate} - \text{Desired Data Rate}}{\text{Desired Data Rate}}\right)$

For reliable communication, the UART baud rate error must never exceed five percent. Table 71 provides information about data rate errors for 5.5296 MHz System Clock.

| 5.5296 MHz System Clock  |                          |                      |           |  |  |  |  |  |  |

|--------------------------|--------------------------|----------------------|-----------|--|--|--|--|--|--|

| Acceptable Rate<br>(kHz) | BRG Divisor<br>(Decimal) | Actual Rate<br>(kHz) | Error (%) |  |  |  |  |  |  |

| 1250.0                   | N/A                      | N/A                  | N/A       |  |  |  |  |  |  |

| 625.0                    | N/A                      | N/A                  | N/A       |  |  |  |  |  |  |

| 250.0                    | 1                        | 345.6                | 38.24     |  |  |  |  |  |  |

| 115.2                    | 3                        | 115.2                | 0.00      |  |  |  |  |  |  |

| 57.6                     | 6                        | 57.6                 | 0.00      |  |  |  |  |  |  |

| 38.4                     | 9                        | 38.4                 | 0.00      |  |  |  |  |  |  |

| 19.2                     | 18                       | 19.2                 | 0.00      |  |  |  |  |  |  |

| 9.60                     | 36                       | 9.60                 | 0.00      |  |  |  |  |  |  |

| 4.80                     | 72                       | 4.80                 | 0.00      |  |  |  |  |  |  |

| 2.40                     | 144                      | 2.40                 | 0.00      |  |  |  |  |  |  |

| 1.20                     | 288                      | 1.20                 | 0.00      |  |  |  |  |  |  |

| 0.60                     | 576                      | 0.60                 | 0.00      |  |  |  |  |  |  |

| 0.30                     | 1152                     | 0.30                 | 0.00      |  |  |  |  |  |  |

#### Table 71. UART Baud Rates

Endec, and passed to the UART. Communication is half-duplex, which means simultaneous data transmission and reception is not allowed.

The baud rate is set by the UART's baud rate generator and supports IrDA standard baud rates from 9600 baud to 115.2 kbaud. Higher baud rates are possible, but do not meet IrDA specifications. The UART must be enabled to use the Infrared Endec. The Infrared Endec data rate is calculated using the following equation:

Infrared Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

### **Transmitting IrDA Data**

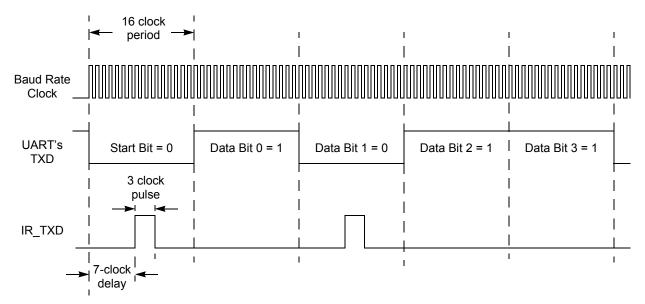

The data to be transmitted using the infrared transceiver is first sent to the UART. The UART's transmit signal (TXD) and baud rate clock are used by the IrDA to generate the modulation signal (IR\_TXD) that drives the infrared transceiver. Each UART/Infrared data bit is 16 clocks wide. If the data to be transmitted is 1, the IR\_TXD signal remains low for the full 16 clock period. If the data to be transmitted is 0, the transmitter first outputs a 7 clock low period, followed by a 3 clock high pulse. Finally, a 6 clock low pulse is output to complete the full 16 clock data period. Figure 17 displays IrDA data transmission. When the Infrared Endec is enabled, the UART's TXD signal is internal to Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_TXD signal is output through the TXD pin.

Figure 17. Infrared Data Transmission

- 5. When the conversion is complete, the ADC control logic performs the following operations:

- 11-bit two's-complement result written to {ADCD\_H[7:0], ADCD\_L[7:5]}.

- CEN resets to 0 to indicate the conversion is complete.

- 6. If the ADC remains idle for 160 consecutive system clock cycles, it is automatically powered-down.

### **Continuous Conversion**

When configured for continuous conversion, the ADC continuously performs an analogto-digital conversion on the selected analog input. Each new data value over-writes the previous value stored in the ADC Data registers. An interrupt is generated after each conversion.

**Caution:** In CONTINUOUS mode, ADC updates are limited by the input signal bandwidth of the ADC and the latency of the ADC and its digital filter. Step changes at the input are not detected at the next output from the ADC. The response of the ADC (in all modes) is limited by the input signal bandwidth and the latency.

Follow the steps below for setting up the ADC and initiating continuous conversion:

- 1. Enable the acceptable analog input by configuring the general-purpose I/O pins for alternate function. This action disables the digital input and output driver.

- 2. Write the ADC Control/Status Register 1 to configure the ADC:

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC for continuous conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Set CONT to 1 to select continuous conversion.

- If the internal VREF must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in ADC Control Register 0.

- Set CEN to 1 to start the conversions.

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- $0 = Crystal \ oscillator \ is \ enabled \ during \ reset, \ resulting \ in \ longer \ reset \ timing$

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

# **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

# Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS        | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD       | Reserved                                        |     |     |     |     |     |     |     |  |

| RESET       | U                                               |     |     |     |     |     |     |     |  |

| R/W         | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR        | Information Page Memory 0020H                   |     |     |     |     |     |     |     |  |

| Note: U = U | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |

Reserved—Altering this register may result in incorrect device operation.

### Trim Bit Address 0001H—Reserved

### Table 90. Trim Option Bits at 0001H

| BITS                                            | 7                             | 6               | 5   | 4   | 3   | 2   | 1   | 0   |

|-------------------------------------------------|-------------------------------|-----------------|-----|-----|-----|-----|-----|-----|

| FIELD                                           | Reserved                      |                 |     |     |     |     |     |     |

| RESET                                           | U                             | U U U U U U U U |     |     |     |     |     | U   |

| R/W                                             | R/W                           | R/W             | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR                                            | Information Page Memory 0021H |                 |     |     |     |     |     |     |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                               |                 |     |     |     |     |     |     |

# OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 157).

### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

### **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

# **Internal Precision Oscillator**

The internal precision oscillator (IPO) is designed for use without external components. You can either manually trim the oscillator for a non-standard frequency or use the automatic factory-trimmed version to achieve a 5.53 MHz frequency. The features of IPO include:

- On-chip RC oscillator that does not require external components

- Output frequency of either 5.53 MHz or 32.8 kHz (contains both a fast and a slow mode)

- Trimming possible through Flash option bits with user override

- Elimination of crystals or ceramic resonators in applications where high timing accuracy is not required

# Operation

An 8-bit trimming register, incorporated into the design, compensates for absolute variation of oscillator frequency. Once trimmed the oscillator frequency is stable and does not require subsequent calibration. Trimming is performed during manufacturing and is not necessary for you to repeat unless a frequency other than 5.53 MHz (fast mode) or 32.8 kHz (slow mode) is required. This trimming is done at +30 °C and a supply voltage of 3.3 V, so accuracy of this operating point is optimal.

Power down this block for minimum system power. By default, the oscillator is configured through the Flash Option bits. However, the user code can override these trim values as described in Trim Bit Address Space on page 146.

Select one of the two frequencies for the oscillator: 5.53 MHz and 32.8 kHz, using the OSCSEL bits in the Oscillator Control on page 165.

• Rotate and Shift

Tables 107 through Table 114 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |  |  |  |  |

|----------|----------|-----------------------------------------------|--|--|--|--|

|          | •        |                                               |  |  |  |  |

| ADC      | dst, src | Add with Carry                                |  |  |  |  |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |  |  |  |  |

| ADD      | dst, src | Add                                           |  |  |  |  |

| ADDX     | dst, src | Add using Extended Addressing                 |  |  |  |  |

| CP       | dst, src | Compare                                       |  |  |  |  |

| CPC      | dst, src | Compare with Carry                            |  |  |  |  |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |  |  |  |  |

| СРХ      | dst, src | Compare using Extended Addressing             |  |  |  |  |

| DA       | dst      | Decimal Adjust                                |  |  |  |  |

| DEC      | dst      | Decrement                                     |  |  |  |  |

| DECW     | dst      | Decrement Word                                |  |  |  |  |

| INC      | dst      | Increment                                     |  |  |  |  |

| INCW     | dst      | Increment Word                                |  |  |  |  |

| MULT     | dst      | Multiply                                      |  |  |  |  |

| SBC      | dst, src | Subtract with Carry                           |  |  |  |  |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |  |  |  |  |

| SUB      | dst, src | Subtract                                      |  |  |  |  |

| SUBX     | dst, src | Subtract using Extended Addressing            |  |  |  |  |

|          |          |                                               |  |  |  |  |

### **Table 107. Arithmetic Instructions**

177

### Table 110. CPU Control Instructions (Continued)

| Mnemonic | Operands | Instruction            |

|----------|----------|------------------------|

| SCF      | —        | Set Carry Flag         |

| SRP      | SrC      | Set Register Pointer   |

| STOP     | _        | STOP Mode              |

| WDT      | _        | Watchdog Timer Refresh |

### Table 111. Load Instructions

| Mnemonic | Operands    | Instruction                                                            |

|----------|-------------|------------------------------------------------------------------------|

| CLR      | dst         | Clear                                                                  |

| LD       | dst, src    | Load                                                                   |

| LDC      | dst, src    | Load Constant to/from Program Memory                                   |

| LDCI     | dst, src    | Load Constant to/from Program Memory and Auto-Increment<br>Addresses   |

| LDE      | dst, src    | Load External Data to/from Data Memory                                 |

| LDEI     | dst, src    | Load External Data to/from Data Memory and Auto-Increment<br>Addresses |

| LDWX     | dst, src    | Load Word using Extended Addressing                                    |

| LDX      | dst, src    | Load using Extended Addressing                                         |

| LEA      | dst, X(src) | Load Effective Address                                                 |

| POP      | dst         | Рор                                                                    |

| POPX     | dst         | Pop using Extended Addressing                                          |

| PUSH     | src         | Push                                                                   |

| PUSHX    | SrC         | Push using Extended Addressing                                         |

### Table 112. Logical Instructions

| Mnemonic | Operands | Instruction                           |

|----------|----------|---------------------------------------|

| AND      | dst, src | Logical AND                           |

| ANDX     | dst, src | Logical AND using Extended Addressing |

| СОМ      | dst      | Complement                            |

| OR       | dst, src | Logical OR                            |

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

192

| Part Number                              | ۶          |            | /O Lines | nterrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|------------------------------------------|------------|------------|----------|-----------|------------------------|---------------------|----------------|---------------------|

| Part                                     | Flash      | RAM        | ĬÕ L     | Inter     | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |

| Z8 Encore! XP with 1                     |            | , 10-Bit A | Analog   | j-to-D    | igital C               | onve                | erter          |                     |

| Standard Temperature: 0 °C to 70 °C      |            |            |          |           |                        |                     |                |                     |

| Z8F0123PB005SC                           | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0123QB005SC                           | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0123SB005SC                           | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0123SH005SC                           | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0123HH005SC                           | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0123PH005SC                           | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0123SJ005SC                           | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0123HJ005SC                           | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0123PJ005SC                           | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |

| Extended Temperatur                      | re: -40 °C | to 105 °C  | ;        |           |                        |                     |                |                     |

| Z8F0123PB005EC                           | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |

| Z8F0123QB005EC                           | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |

| Z8F0123SB005EC                           | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |

| Z8F0123SH005EC                           | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |

| Z8F0123HH005EC                           | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |

| Z8F0123PH005EC                           | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |

| Z8F0123SJ005EC                           | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |

| Z8F0123HJ005EC                           | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |

| Z8F0123PJ005EC                           | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |            |            |          |           |                        |                     |                |                     |

223

| Jaquing<br>Trad<br>Z8 Encore! XP <sup>®</sup> F0823 S | Flash                                                      | W W W W W W W W W W W W W W W W W W W | t I/O Lines | ∓<br>Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description                |

|-------------------------------------------------------|------------------------------------------------------------|---------------------------------------|-------------|-----------------|------------------------|---------------------|----------------|----------------------------|

| Z8F08A28100KITG                                       | · · · · · · · · · · · · · · · · · · ·                      |                                       |             |                 |                        |                     |                |                            |

| Z8F04A28100KITG                                       |                                                            | Z8 Enco                               | re! XP      | F042            | A Serie                | es De               | velo           | pment Kit (20- and 28-Pin) |

| Z8F04A08100KITG                                       |                                                            | Z8 Enco                               | re! XP      | F042            | A Serie                | es De               | velo           | pment Kit (8-Pin)          |

| ZUSBSC00100ZACG USB Smart Cable Accessory Kit         |                                                            |                                       |             |                 |                        |                     |                |                            |

| ZUSBOPTSC01ZACG                                       | USBOPTSC01ZACG Opto-Isolated USB Smart Cable Accessory Kit |                                       |             |                 |                        |                     |                | essory Kit                 |

| ENETSC0100ZACG Ethernet Smart Cable Accessory Kit     |                                                            |                                       |             |                 |                        |                     |                |                            |