Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813ph005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 1

# **Overview**

Zilog's Z8 Encore! XP<sup>®</sup> microcontroller unit (MCU) family of products are the first Zilog<sup>®</sup> microcontroller products based on the 8-bit eZ8 CPU core. Z8 Encore! XP F0823 Series products expand upon Zilog's extensive line of 8-bit microcontrollers. The Flash in-circuit programming capability allows for faster development time and program changes in the field. The new eZ8 CPU is upward compatible with existing Z8<sup>®</sup> instructions. The rich peripheral set of Z8 Encore! XP F0823 Series makes it suitable for a variety of applications including motor control, security systems, home appliances, personal electronic devices, and sensors.

## **Features**

The key features of Z8 Encore! XP F0823 Series include:

- 5 MHz eZ8 CPU

- 1 KB, 2 KB, 4 KB, or 8 KB Flash memory with in-circuit programming capability

- 256 B, 512 B, or 1 KB register RAM

- 6 to 24 I/O pins depending upon package

- Internal precision oscillator (IPO)

- Full-duplex UART

- The universal asynchronous receiver/transmitter (UART) baud rate generator (BRG) can be configured and used as a basic 16-bit timer

- Infrared data association (IrDA)-compliant infrared encoder/decoders, integrated with UART

- Two enhanced 16-bit timers with capture, compare, and PWM capability

- Watchdog Timer (WDT) with dedicated internal RC oscillator

- On-Chip Debugger (OCD)

- Optional 8-channel, 10-bit Analog-to-Digital Converter (ADC)

- On-Chip analog comparator

- Up to 20 vectored interrupts

- Direct LED drive with programmable drive strengths

- Voltage Brownout (VBO) protection

- Power-On Reset (POR)

|          | •                                   | •                                                                          |

|----------|-------------------------------------|----------------------------------------------------------------------------|

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source                                                   |

| Highest  | 0002H                               | Reset (not an interrupt)                                                   |

|          | 0004H                               | Watchdog Timer (see Watchdog Timer on page 87)                             |

|          | 003AH                               | Primary Oscillator Fail Trap (not an interrupt)                            |

|          | 003CH                               | Watchdog Timer Oscillator Fail Trap (not an interrupt)                     |

|          | 0006H                               | Illegal Instruction Trap (not an interrupt)                                |

|          | 0008H                               | Reserved                                                                   |

|          | 000AH                               | Timer 1                                                                    |

|          | 000CH                               | Timer 0                                                                    |

|          | 000EH                               | UART 0 receiver                                                            |

|          | 0010H                               | UART 0 transmitter                                                         |

|          | 0012H                               | Reserved                                                                   |

|          | 0014H                               | Reserved                                                                   |

|          | 0016H                               | ADC                                                                        |

|          | 0018H                               | Port A Pin 7, selectable rising or falling input edge                      |

|          | 001AH                               | Port A Pin 6, selectable rising or falling input edge or Comparator Output |

|          | 001CH                               | Port A Pin 5, selectable rising or falling input edge                      |

|          | 001EH                               | Port A Pin 4, selectable rising or falling input edge                      |

|          | 0020H                               | Port A Pin 3 or Port D Pin 3, selectable rising or falling input edge      |

|          | 0022H                               | Port A Pin 2 or Port D Pin 2, selectable rising or falling input edge      |

|          | 0024H                               | Port A Pin 1, selectable rising or falling input edge                      |

|          | 0026H                               | Port A Pin 0, selectable rising or falling input edge                      |

|          | 0028H                               | Reserved                                                                   |

|          | 002AH                               | Reserved                                                                   |

|          | 002CH                               | Reserved                                                                   |

|          | 002EH                               | Reserved                                                                   |

|          | 0030H                               | Port C Pin 3, both input edges                                             |

|          | 0032H                               | Port C Pin 2, both input edges                                             |

|          | 0034H                               | Port C Pin 1, both input edges                                             |

|          |                                     |                                                                            |

## Table 33. Trap and Interrupt Vectors in Order of Priority

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|

| FIELD | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| ADDR  |         | FC4H    |        |        |               |        |        |        |

### Table 41. IRQ1 Enable High Bit Register (IRQ1ENH)

PA7VENH—Port A Bit[7] Interrupt Request Enable High Bit PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit PAxENH—Port A Bit[x] Interrupt Request Enable High Bit For selection of Port A as the interrupt source, see Shared Interrupt Select Register on page 64.

#### Table 42. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|

| FIELD | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |

| ADDR  |         | FC5H    |        |        |               |        |        |        |

PA7VENH—Port A Bit[7] Interrupt Request Enable Low Bit PA6CENH—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

# **IRQ2 Enable High and Low Bit Registers**

Table 43 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers (Table 44 and Table 45) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register.

#### Table 43. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

63

### Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[x] | IRQ2ENL[ | x] Priority | Description |

|------------|----------|-------------|-------------|

| 1          | 1        | Level 3     | High        |

where x indicates the register bits from 0–7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0     |

|-------|-----|------|-------|-----|-------|-------|-------|-------|

| FIELD |     | Rese | erved |     | C3ENH | C2ENH | C1ENH | C0ENH |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |     |      |       | FC  | 7H    |       |       |       |

Reserved—Must be 0

C3ENH—Port C3 Interrupt Request Enable High Bit C2ENH—Port C2 Interrupt Request Enable High Bit C1ENH—Port C1 Interrupt Request Enable High Bit C0ENH—Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7        | 6    | 5   | 4   | 3     | 2     | 1     | 0     |

|-------|----------|------|-----|-----|-------|-------|-------|-------|

| FIELD | Reserved |      |     |     | C3ENL | C2ENL | C1ENL | C0ENL |

| RESET | 0        | 0    | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W      | R/W  | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |          | FC8H |     |     |       |       |       |       |

Reserved-Must be 0

C3ENL—Port C3 Interrupt Request Enable Low Bit C2ENL—Port C2 Interrupt Request Enable Low Bit C1ENL—Port C1 Interrupt Request Enable Low Bit C0ENL—Port C0 Interrupt Request Enable Low Bit

## Interrupt Edge Select Register

The Interrupt Edge Select (IRQES) register (Table 46) determines whether an interrupt is generated for the rising edge or falling edge on the selected GPIO Port A or Port D input pin.

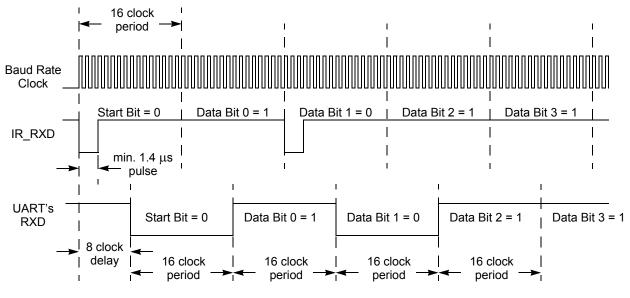

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the 1.4 μs minimum width pulses allowed by the IrDA standard.

### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

# **Analog-to-Digital Converter**

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

bits of resolution are lost because of a rounding error. As a result, the final value is an 11- bit number.

## Automatic Powerdown

If the ADC is idle (no conversions in progress) for 160 consecutive system clock cycles, portions of the ADC are automatically powered down. From this powerdown state, the ADC requires 40 system clock cycles to powerup. The ADC powers up when a conversion is requested by the ADC Control register.

## Single-Shot Conversion

When configured for single-shot conversion, the ADC performs a single analog-to-digital conversion on the selected analog input channel. After completion of the conversion, the ADC shuts down. Follow the steps below for setting up the ADC and initiating a single-shot conversion:

- 1. Enable the acceptable analog inputs by configuring the general-purpose I/O pins for alternate function. This configuration disables the digital input and output drivers.

- 2. Write the ADC Control/Status Register 1 to configure the ADC

- Write the REFSELH bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELH bit is contained in the ADC Control/Status Register 1.

- 3. Write to the ADC Control Register 0 to configure the ADC and begin the conversion. The bit fields in the ADC Control register can be written simultaneously:

- Write to the ANAIN[3:0] field to select from the available analog input sources (different input pins available depending on the device).

- Clear CONT to 0 to select a single-shot conversion.

- If the internal voltage reference must be output to a pin, set the REFEXT bit to 1. The internal voltage reference must be enabled in this case.

- Write the REFSELL bit of the pair {REFSELH, REFSELL} to select the internal voltage reference level or to disable the internal reference. The REFSELL bit is contained in the ADC Control Register 0.

- Set CEN to 1 to start the conversion.

- 4. CEN remains 1 while the conversion is in progress. A single-shot conversion requires 5129 system clock cycles to complete. If a single-shot conversion is requested from an ADC powered-down state, the ADC uses 40 additional clock cycles to power-up before beginning the 5129 cycle conversion.

# Comparator

Z8 Encore! XP<sup>®</sup> F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The features of Comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

# Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see Power Control Register 0 on page 32.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts after comparator enabling. The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

# **Comparator Control Register Definitions**

## **Comparator Control Register**

The Comparator Control register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flowchart in Figure 21 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

# Flash Sector Protect Register

The Flash Sector Protect (FPROT) register is shared with the Flash Page Select Register. When the Flash Control Register is written with 73H followed by 5EH, the next write to this address targets the Flash Sector Protect Register. In all other cases, it targets the Flash Page Select Register.

This register selects one of the 8 available Flash memory sectors to be protected. The reset state of each Sector Protect bit is an unprotected state. After a sector is protected by setting its corresponding register bit, it cannot be unprotected (the register bit cannot be cleared) without powering down the device.

| BITS  | 7      | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|-------|--------|--------|--------|--------|--------|--------|--------|--------|

| FIELD | SPROT7 | SPROT6 | SPROT5 | SPROT4 | SPROT3 | SPROT2 | SPROT1 | SPROT0 |

| RESET | 0      | 0      | 0      | 0      | 0      | 0      | 0      | 0      |

| R/W   | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    | R/W    |

| ADDR  |        | FF9H   |        |        |        |        |        |        |

Table 82. Flash Sector Protect Register (FPROT)

SPROT7-SPROT0—Sector Protection

Each bit corresponds to a 512 bytes Flash sector. For the Z8F08x3 devices, the upper 3 bits must be zero. For the Z8F04x3 devices all bits are used. For the Z8F02x3 devices, the upper 4 bits are unused. For the Z8F01x3 devices, the upper 6 bits are unused.

# Flash Frequency High and Low Byte Registers

The Flash Frequency High (FFREQH) and Low Byte (FFREQL) registers combine to form a 16-bit value, FFREQ, to control timing for Flash program and erase operations. The 16-bit binary Flash Frequency value must contain the system clock frequency (in kHz) and is calculated using the following equation:

```

FFREQ[15:0] = {FFREQH[7:0],FFREQL[7:0]} = System Clock Frequency

1000

```

**Caution:** The Flash Frequency High and Low Byte registers must be loaded with the correct value to ensure proper operation of the device. Also, Flash programming and erasure is not supported for system clock frequencies below 20 kHz or above 20 MHz.

## Table 95. Serialization Data Locations

| Info Page<br>Address | Memory Address | Usage                                    |

|----------------------|----------------|------------------------------------------|

| 1C                   | FE1C           | Serial Number Byte 3 (most significant)  |

| 1D                   | FE1D           | Serial Number Byte 2                     |

| 1E                   | FE1E           | Serial Number Byte 1                     |

| 1F                   | FE1F           | Serial Number Byte 0 (least significant) |

# **Randomized Lot Identifier**

## Table 96. Lot Identification Number (RAND\_LOT)

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD     | RAND_LOT                                        |     |     |     |     |     |     |     |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR      | Interspersed throughout Information Page Memory |     |     |     |     |     |     |     |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |

RAND LOT-Randomized Lot ID

The randomized lot ID is a 32 byte binary value that changes for each production lot.

### Table 97. Randomized Lot ID Locations

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

| 150 |

|-----|

|-----|

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 5C                   | FE5C              | Randomized Lot ID Byte 23                    |

| 5D                   | FE5D              | Randomized Lot ID Byte 22                    |

| 5E                   | FE5E              | Randomized Lot ID Byte 21                    |

| 5F                   | FE5F              | Randomized Lot ID Byte 20                    |

| 61                   | FE61              | Randomized Lot ID Byte 19                    |

| 62                   | FE62              | Randomized Lot ID Byte 18                    |

| 64                   | FE64              | Randomized Lot ID Byte 17                    |

| 65                   | FE65              | Randomized Lot ID Byte 16                    |

| 67                   | FE67              | Randomized Lot ID Byte 15                    |

| 68                   | FE68              | Randomized Lot ID Byte 14                    |

| 6A                   | FE6A              | Randomized Lot ID Byte 13                    |

| 6B                   | FE6B              | Randomized Lot ID Byte 12                    |

| 6D                   | FE6D              | Randomized Lot ID Byte 11                    |

| 6E                   | FE6E              | Randomized Lot ID Byte 10                    |

| 70                   | FE70              | Randomized Lot ID Byte 9                     |

| 71                   | FE71              | Randomized Lot ID Byte 8                     |

| 73                   | FE73              | Randomized Lot ID Byte 7                     |

| 74                   | FE74              | Randomized Lot ID Byte 6                     |

| 76                   | FE76              | Randomized Lot ID Byte 5                     |

| 77                   | FE77              | Randomized Lot ID Byte 4                     |

| 79                   | FE79              | Randomized Lot ID Byte 3                     |

| 7A                   | FE7A              | Randomized Lot ID Byte 2                     |

| 7C                   | FE7C              | Randomized Lot ID Byte 1                     |

| 7D                   | FE7D              | Randomized Lot ID Byte 0 (least significant) |

## Table 97. Randomized Lot ID Locations (Continued)

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP<sup>®</sup> F0823 Series products. When this option is enabled, several of the OCD commands are disabled. Table 99 on page 162 is a summary of the OCD commands. Each OCD command is described in further detail in the bulleted list following this table. Table 99 on page 162 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|----------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                                                                                                                                                         |

| Reserved                   | 01H             | _                                     | -                                                                                                                                                                         |

| Read OCD Status Register   | 02H             | Yes                                   | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H             | _                                     | -                                                                                                                                                                         |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                                                                                                                                                 |

| Read OCD Control Register  | 05H             | Yes                                   | -                                                                                                                                                                         |

| Write Program Counter      | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter       | 07H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Register             | 08H             | _                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register              | 09H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory       | 0AH             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory        | 0BH             | _                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory          | 0CH             | _                                     | Yes.                                                                                                                                                                      |

| Read Data Memory           | 0DH             | -                                     | -                                                                                                                                                                         |

| Read Program Memory CRC    | OEH             | -                                     | -                                                                                                                                                                         |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                         |

| Step Instruction           | 10H             | _                                     | Disabled.                                                                                                                                                                 |

# **Oscillator Control**

Z8 Encore! XP<sup>®</sup> F0823 Series devices uses three possible clocking schemes, each user-selectable:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, Z8 Encore! XP F0823 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

## **System Clock Selection**

The oscillator control block selects from the available clocks. Table 101 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                 | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>           | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                   |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 101. Oscillator Configuration and Selection

### Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing (Continued)

|                  |                     | T <sub>A</sub> = | = 3.0 V to<br>0 °C to +<br>otherwise | 70 °C           |       |                                      |  |

|------------------|---------------------|------------------|--------------------------------------|-----------------|-------|--------------------------------------|--|

| Symbol Parameter |                     | Minimum          | Typical                              | Maximum         | Units | Conditions                           |  |

| Zin              | Input Impedance     | -                | 150                                  |                 | kΩ    | In unbuffered mode at 20 $\rm MHz^5$ |  |

|                  |                     |                  |                                      |                 |       |                                      |  |

| Vin              | Input Voltage Range | 0                |                                      | V <sub>DD</sub> | V     | Unbuffered Mode                      |  |

|                  |                     |                  |                                      |                 |       |                                      |  |

Notes

1. Analog source impedance affects the ADC offset voltage (because of pin leakage) and input settling time.

Devices are factory calibrated at V<sub>DD</sub> = 3.3 V and T<sub>A</sub> = +30 °C, so the ADC is maximally accurate under these conditions.

3. LSBs are defined assuming 10-bit resolution.

4. This is the maximum recommended resistance seen by the ADC input pin.

5. The input impedance is inversely proportional to the system clock frequency.

| Table 126. | Comparator | Electrical | Characteristics |

|------------|------------|------------|-----------------|

|------------|------------|------------|-----------------|

|                   |                                            |                 | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C |                    |       |                    |  |

|-------------------|--------------------------------------------|-----------------|------------------------------------------------------------------------|--------------------|-------|--------------------|--|

| Symbol            | Parameter                                  | Minimum         | linimum Typical Maximum                                                |                    | Units | Conditions         |  |

| V <sub>OS</sub>   | Input DC Offset                            |                 | 5                                                                      |                    | mV    |                    |  |

|                   | Programmable Internal<br>Reference Voltage |                 | <u>+</u> 5                                                             |                    | %     | 20-/28-pin devices |  |

|                   |                                            |                 | <u>+</u> 3                                                             |                    | %     | 8-pin devices      |  |

| T <sub>PROP</sub> | Propagation Delay                          |                 | 200                                                                    |                    | ns    |                    |  |

| V <sub>HYS</sub>  | Input Hysteresis                           |                 | 4                                                                      |                    | mV    |                    |  |

| V <sub>IN</sub>   | Input Voltage Range                        | V <sub>SS</sub> |                                                                        | V <sub>DD</sub> -1 | V     |                    |  |

## General Purpose I/O Port Input Data Sample Timing

Figure 29 displays timing of the GPIO Port input sampling. The input value on a GPIO Port pin is sampled on the rising edge of the system clock. The Port value is available to the eZ8 CPU on the second rising clock edge following the change of the Port value.

211

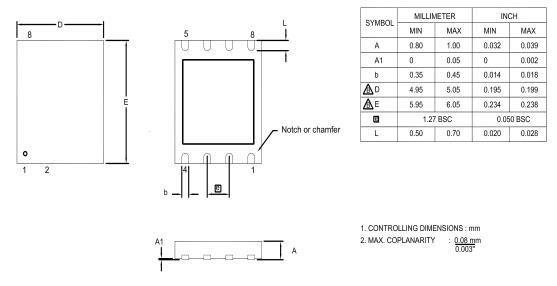

Figure 36 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F0823 Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 36. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

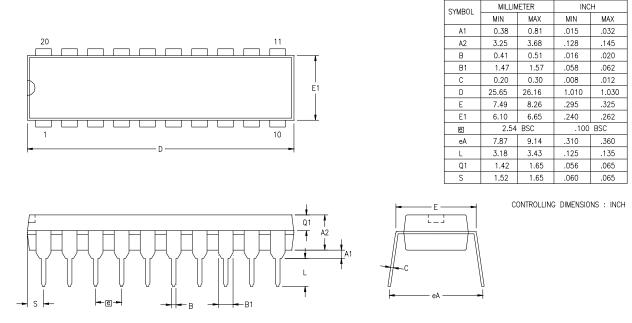

Figure 37 displays the 20-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Figure 37. 20-Pin Plastic Dual Inline Package (PDIP)

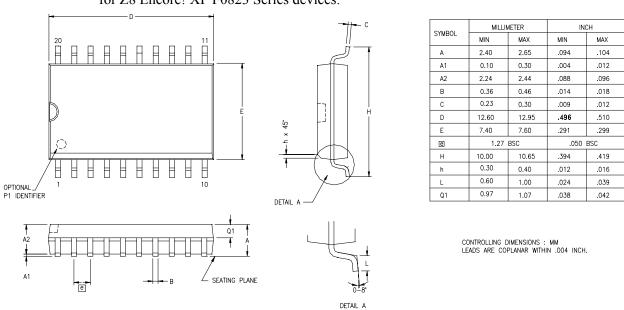

Figure 38 displays the 20-pin Small Outline Integrated Circuit Package (SOIC) available for Z8 Encore! XP F0823 Series devices.

Figure 38. 20-Pin Small Outline Integrated Circuit Package (SOIC)

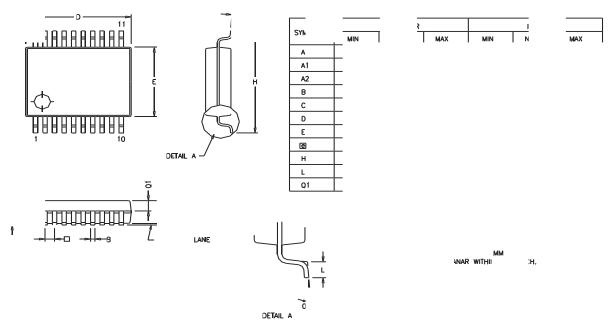

Figure 39 displays the 20-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

Figure 39. 20-Pin Small Shrink Outline Package (SSOP)

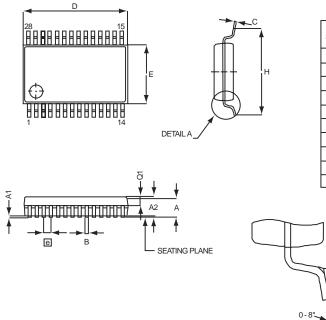

# Figure 42 displays the 28-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

|        | MILLIMETER |          |       | INCH  |            |          |

|--------|------------|----------|-------|-------|------------|----------|

| SYMBOL | MIN        | NOM      | MAX   | MIN   | NOM        | MAX      |

| А      | 1.73       | 1.86     | 1.99  | 0.068 | 0.073      | 0.078    |

| A1     | 0.05       | 0.13     | 0.21  | 0.002 | 0.005      | 0.008    |

| A2     | 1.68       | 1.73     | 1.78  | 0.066 | 0.068      | 0.070    |

| В      | 0.25       |          | 0.38  | 0.010 |            | 0.015    |

| С      | 0.09       | -        | 0.20  | 0.004 | 0.006      | 0.008    |

| D      | 10.07      | 10.20    | 10.33 | 0.397 | 0.402      | 0.407    |

| E      | 5.20       | 5.30     | 5.38  | 0.205 | 0.209      | 0.212    |

| е      |            | 0.65 TYP |       |       | 0.0256 TYF | <b>b</b> |

| н      | 7.65       | 7.80     | 7.90  | 0.301 | 0.307      | 0.311    |

| L      | 0.63       | 0.75     | 0.95  | 0.025 | 0.030      | 0.037    |

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

Figure 42. 28-Pin Small Shrink Outline Package (SSOP)

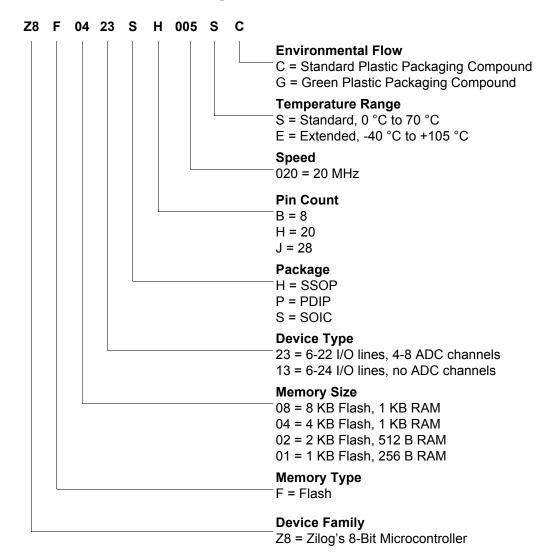

## Part Number Suffix Designations

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

236