Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Through Hole                                              |

| Package / Case             | 20-DIP (0.300", 7.62mm)                                   |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813ph005sc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Operation                                               | 152 |

|---------------------------------------------------------|-----|

| OCD Interface                                           |     |

|                                                         |     |

| OCD Data FormatOCD Data Format                          |     |

| OCD Serial Errors                                       |     |

| OCD Unlock Sequence (8-Pin Devices Only)                |     |

| Breakpoints                                             |     |

| Runtime Counter                                         | 156 |

| On-Chip Debugger Commands                               | 157 |

| On-Chip Debugger Control Register Definitions           | 161 |

| OCD Control Register                                    |     |

| OCD Status Register                                     | 163 |

| Oscillator Control                                      |     |

| Operation                                               |     |

| System Clock Selection                                  |     |

| Clock Failure Detection and Recovery                    |     |

| Oscillator Control Register Definitions                 |     |

| Internal Precision Oscillator                           |     |

| Operation                                               |     |

| eZ8 CPU Instruction Set                                 |     |

| Assembly Language Programming Introduction              |     |

| Assembly Language Syntax                                |     |

| eZ8 CPU Instruction Notation                            |     |

| eZ8 CPU Instruction Classes                             |     |

| eZ8 CPU Instruction Summary                             |     |

| Opcode Maps                                             |     |

| Electrical Characteristics                              | 193 |

| Absolute Maximum Ratings                                | 193 |

| DC Characteristics                                      |     |

| AC Characteristics                                      | 197 |

| On-Chip Peripheral AC and DC Electrical Characteristics |     |

| General Purpose I/O Port Input Data Sample Timing       |     |

| General Purpose I/O Port Output Timing                  |     |

|                                                         |     |

| Packaging                                               |     |

|                                                         |     |

Table of Contents

The pin configurations listed are preliminary and subject to change based on manufacturing limitations.

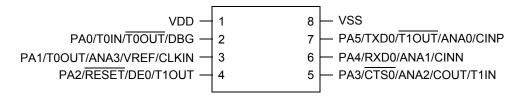

#### Figure 2. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 8-Pin SOIC, QFN/MLF-S, or PDIP Package\*

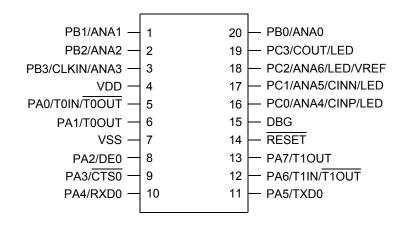

### Figure 3. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 20-Pin SOIC, SSOP or PDIP Package\*

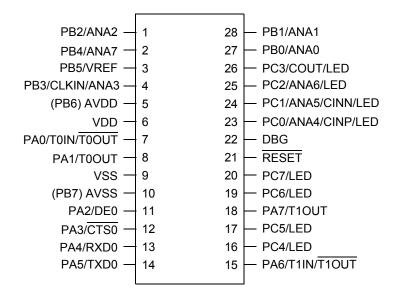

Figure 4. Z8F08x3, Z8F04x3, F02x3 and Z8F01x3 in 28-Pin SOIC, SSOP or PDIP Package\*

10

| Signal Mnemonic                                      | I/O | Description                                                                                                                                                                                                           |

|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog                                               |     |                                                                                                                                                                                                                       |

| ANA[7:0]                                             | Ι   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |

| VREF                                                 | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |

| Clock Input                                          |     |                                                                                                                                                                                                                       |

| CLKIN                                                | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |

| LED Drivers                                          |     |                                                                                                                                                                                                                       |

| LED                                                  | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |

| On-Chip Debugger                                     |     |                                                                                                                                                                                                                       |

| DBG                                                  | I/O | Debug. This signal is the control and data input and output to and from the OCD.                                                                                                                                      |

|                                                      |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull                                                                                                                                               |

|                                                      |     | up resistor to ensure proper operation.                                                                                                                                                                               |

| Reset                                                |     |                                                                                                                                                                                                                       |

| RESET                                                | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |

| Power Supply                                         |     |                                                                                                                                                                                                                       |

| V <sub>DD</sub>                                      | I   | Digital Power Supply.                                                                                                                                                                                                 |

| AV <sub>DD</sub>                                     | Ι   | Analog Power Supply.                                                                                                                                                                                                  |

| V <sub>SS</sub>                                      | I   | Digital Ground.                                                                                                                                                                                                       |

| AV <sub>SS</sub>                                     | I   | Analog Ground.                                                                                                                                                                                                        |

| Note: The AV <sub>DD</sub> and A<br>PB7 on 28-pin pa |     | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and without ADC.                                                                                                                        |

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

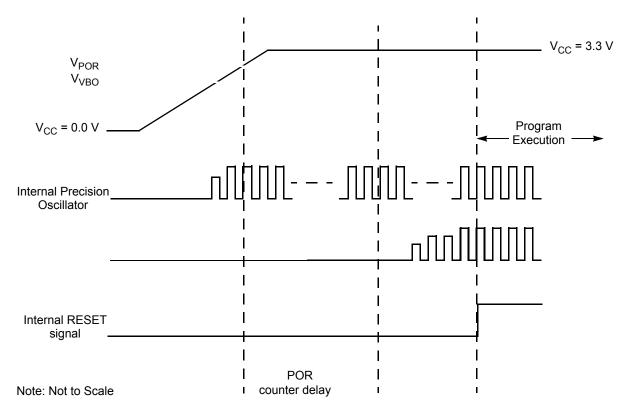

Figure 5. Power-On Reset Operation

## Voltage Brownout Reset

The devices in the Z8 Encore! XP F0823 Series provide low VBO protection. The VBO circuit senses when the supply voltage drops to an unsafe level (below the VBO threshold voltage) and forces the device into the Reset state. While the supply voltage remains below the POR voltage threshold ( $V_{POR}$ ), the VBO block holds the device in the Reset.

After the supply voltage again exceeds the Power-On Reset voltage threshold, the device progresses through a full System Reset sequence, as described in the POR section. Following POR, the POR status bit in the Reset Status (RSTSTAT) register is set to 1. Figure 6 displays Voltage Brownout operation. For the VBO and POR threshold voltages ( $V_{VBO}$  and  $V_{POR}$ ), see Electrical Characteristics on page 193.

The VBO circuit can be either enabled or disabled during STOP mode. Operation during STOP mode is set by the VBO\_AO Flash Option bit. For information on configuring VBO\_AO, see Flash Option Bits on page 141.

PSMRE[7:0]—Port Stop Mode Recovery Source Enabled.

0 = The Port pin is not configured as a Stop Mode Recovery source. Transitions on this pin during STOP mode do not initiate Stop Mode Recovery.

1 = The Port pin is configured as a Stop Mode Recovery source. Any logic transition on this pin during STOP mode initiates Stop Mode Recovery.

## Port A–C Pull-up Enable Sub-Registers

The Port A–C Pull-up Enable sub-register (Table 25) is accessed through the Port A–C Control register by writing 06H to the Port A–C Address register. Setting the bits in the Port A–C Pull-up Enable sub-registers enables a weak internal resistive pull-up on the specified Port pins.

Table 25. Port A–C Pull-Up Enable Sub-Registers (PxPUE)

| BITS  | 7        | 6                                                                                     | 5     | 4     | 3     | 2     | 1     | 0     |  |

|-------|----------|---------------------------------------------------------------------------------------|-------|-------|-------|-------|-------|-------|--|

| FIELD | PPUE7    | PPUE6                                                                                 | PPUE5 | PPUE4 | PPUE3 | PPUE2 | PPUE1 | PPUE0 |  |

| RESET | 0        | 0                                                                                     | 0     | 0     | 0     | 0     | 0     | 0     |  |

| R/W   | R/W      | R/W                                                                                   | R/W   | R/W   | R/W   | R/W   | R/W   | R/W   |  |

| ADDR  | lf 06H i | If 06H in Port A–C Address Register, accessible through the Port A–C Control Register |       |       |       |       |       |       |  |

PPUE[7:0]—Port Pull-up Enabled

0 = The weak pull-up on the Port pin is disabled.

1 = The weak pull-up on the Port pin is enabled.

## Port A–C Alternate Function Set 1 Sub-Registers

The Port A–C Alternate Function Set1 sub-register (Table 26) is accessed through the Port A–C Control register by writing 07H to the Port A–C Address register. The Alternate Function Set 1 sub-registers selects the alternate function available at a port pin. Alternate Functions selected by setting or clearing bits of this register are defined in GPIO Alternate Functions on page 36.

Note:

*Alternate function selection on port pins must also be enabled as described in* Port A–C Alternate Function Sub-Registers *on page 45*.

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |  |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|--|--|

| FIELD | PA7VENH | PA6CENH | PA5ENH | PA4ENH | <b>PA3ENH</b> | PA2ENH | PA1ENH | PA0ENH |  |  |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |  |

| ADDR  |         | FC4H    |        |        |               |        |        |        |  |  |

#### Table 41. IRQ1 Enable High Bit Register (IRQ1ENH)

PA7VENH—Port A Bit[7] Interrupt Request Enable High Bit PA6CENH—Port A Bit[7] or Comparator Interrupt Request Enable High Bit PAxENH—Port A Bit[x] Interrupt Request Enable High Bit For selection of Port A as the interrupt source, see Shared Interrupt Select Register on page 64.

#### Table 42. IRQ1 Enable Low Bit Register (IRQ1ENL)

| BITS  | 7       | 6       | 5      | 4      | 3             | 2      | 1      | 0      |  |

|-------|---------|---------|--------|--------|---------------|--------|--------|--------|--|

| FIELD | PA7VENL | PA6CENL | PA5ENL | PA4ENL | <b>PA3ENL</b> | PA2ENL | PA1ENL | PA0ENL |  |

| RESET | 0       | 0       | 0      | 0      | 0             | 0      | 0      | 0      |  |

| R/W   | R/W     | R/W     | R/W    | R/W    | R/W           | R/W    | R/W    | R/W    |  |

| ADDR  | FC5H    |         |        |        |               |        |        |        |  |

PA7VENH—Port A Bit[7] Interrupt Request Enable Low Bit PA6CENH—Port A Bit[6] or Comparator Interrupt Request Enable Low Bit PAxENL—Port A Bit[x] Interrupt Request Enable Low Bit

## **IRQ2 Enable High and Low Bit Registers**

Table 43 describes the priority control for IRQ2. The IRQ2 Enable High and Low Bit registers (Table 44 and Table 45) form a priority encoded enabling for interrupts in the Interrupt Request 2 register. Priority is generated by setting bits in each register.

#### Table 43. IRQ2 Enable and Priority Encoding

| IRQ2ENH[x] | IRQ2ENL[x] | Priority | Description |

|------------|------------|----------|-------------|

| 0          | 0          | Disabled | Disabled    |

| 0          | 1          | Level 1  | Low         |

| 1          | 0          | Level 2  | Nominal     |

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

- 0x = Timer Interrupt occurs on all defined Reload, Compare and Input Events

- 10 = Timer Interrupt only on defined Input Capture/Deassertion Events

- 11 = Timer Interrupt only on defined Reload/Compare Events

Reserved-Must be 0

#### PWMD—PWM Delay value

This field is a programmable delay to control the number of system clock cycles delay before the Timer Output and the Timer Output Complement are forced to their active state.

000 = No delay 001 = 2 cycles delay 010 = 4 cycles delay 011 = 8 cycles delay 100 = 16 cycles delay 101 = 32 cycles delay 110 = 64 cycles delay111 = 128 cycles delay

INPCAP—Input Capture Event

This bit indicates if the most recent timer interrupt is caused by a Timer Input Capture Event.

0 = Previous timer interrupt is not a result of Timer Input Capture Event

1 = Previous timer interrupt is a result of Timer Input Capture Event

#### Timer 0–1 Control Register 1

The Timer 0–1 Control (TxCTL1) registers enable/disable the timers, set the prescaler value, and determine the timer operating mode.

| BITS  | 7          | 6    | 5   | 4    | 3   | 2     | 1   | 0   |

|-------|------------|------|-----|------|-----|-------|-----|-----|

| FIELD | TEN        | TPOL |     | PRES |     | TMODE |     |     |

| RESET | 0          | 0    | 0   | 0    | 0   | 0     | 0   | 0   |

| R/W   | R/W        | R/W  | R/W | R/W  | R/W | R/W   | R/W | R/W |

| ADDR  | F07H, F0FH |      |     |      |     |       |     |     |

Table 56. Timer 0–1 Control Register 1 (TxCTL1)

TEN—Timer Enable

0 = Timer is disabled

1 = Timer enabled to count

TPOL—Timer Input/Output Polarity

Operation of this bit is a function of the current operating mode of the timer

## Operation

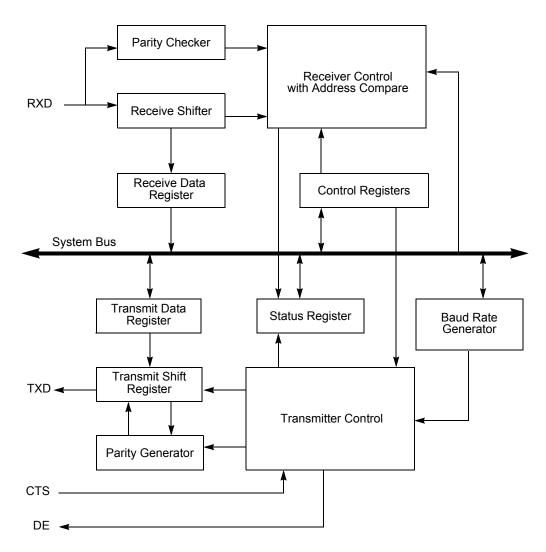

### **Data Format**

The UART always transmits and receives data in an 8-bit data format, least-significant bit (lsb) first. An even or odd parity bit can be added to the data stream. Each character begins with an active Low Start bit and ends with either 1 or 2 active High Stop bits. Figure 11 and Figure 12 display the asynchronous data format employed by the UART without parity and with parity, respectively.

- 6. Check the TDRE bit in the UART Status 0 register to determine if the Transmit Data register is empty (indicated by a 1). If empty, continue to step 7. If the Transmit Data register is full (indicated by a 0), continue to monitor the TDRE bit until the Transmit Data register becomes available to receive new data.

- 7. Write the UART Control 1 register to select the outgoing address bit.

- 8. Set the Multiprocessor Bit Transmitter (MPBT) if sending an address byte, clear it if sending a data byte.

- 9. Write the data byte to the UART Transmit Data register. The transmitter automatically transfers the data to the Transmit Shift register and transmits the data.

- 10. Make any changes to the Multiprocessor Bit Transmitter (MPBT) value, if appropriate and MULTIPROCESSOR mode is enabled,.

- 11. To transmit additional bytes, return to step 5.

#### Transmitting Data using the Interrupt-Driven Method

The UART Transmitter interrupt indicates the availability of the Transmit Data register to accept new data for transmission. Follow the steps below to configure the UART for interrupt-driven data transmission:

- 1. Write to the UART Baud Rate High and Low Byte registers to set the appropriate baud rate.

- 2. Enable the UART pin functions by configuring the associated GPIO port pins for alternate function operation.

- 3. Execute a DI instruction to disable interrupts.

- 4. Write to the Interrupt control registers to enable the UART Transmitter interrupt and set the acceptable priority.

- 5. Write to the UART Control 1 register to enable MULTIPROCESSOR (9-bit) mode functions, if MULTIPROCESSOR mode is appropriate.

- 6. Set the MULTIPROCESSOR Mode Select (MPEN) to Enable MULTIPROCESSOR mode.

- 7. Write to the UART Control 0 register to:

- Set the transmit enable bit (TEN) to enable the UART for data transmission.

- Enable parity, if appropriate and if MULTIPROCESSOR mode is not enabled, and select either even or odd parity.

- Set or clear CTSE to enable or disable control from the remote receiver using the  $\overline{\text{CTS}}$  pin.

- 8. Execute an EI instruction to enable interrupts.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01 = Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP<sup>®</sup> F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

| 1 | 28 |

|---|----|

| BITS  | 7      | 6      | 5   | 4   | 3    | 2     | 1   | 0   |  |

|-------|--------|--------|-----|-----|------|-------|-----|-----|--|

| FIELD | INPSEL | INNSEL |     | REF | Rese | erved |     |     |  |

| RESET | 0      | 0      | 0   | 1   | 0    | 1     | 0   | 0   |  |

| R/W   | R/W    | R/W    | R/W | R/W | R/W  | R/W   | R/W | R/W |  |

| ADDR  |        | F90H   |     |     |      |       |     |     |  |

#### Table 76. Comparator Control Register (CMP0)

INPSEL—Signal Select for Positive Input

0 = GPIO pin used as positive comparator input

1 = temperature sensor used as positive comparator input

INNSEL—Signal Select for Negative Input

0 = internal reference disabled, GPIO pin used as negative comparator input

1 = internal reference enabled as negative comparator input

REFLVL—Internal Reference Voltage Level

Note:

This reference is independent of the ADC voltage reference.

0000 = 0.0 V 0001 = 0.2 V 0010 = 0.4 V 0011 = 0.6 V 0100 = 0.8 V 0101 = 1.0 V (Default) 0110 = 1.2 V 0111 = 1.4 V 1000 = 1.6 V 1001 = 1.8 V1010-1111 = Reserved

Reserved—R/W bits must be 0 during writes; 0 when read

# Operation

The Flash Controller programs and erases Flash memory. The Flash Controller provides the proper Flash controls and timing for Byte Programming, Page Erase, and Mass Erase of Flash memory.

The Flash Controller contains several protection mechanisms to prevent accidental programming or erasure. These mechanism operate on the page, sector and full-memory levels.

The Flowchart in Figure 21 displays basic Flash Controller operation. The following subsections provide details about the various operations (Lock, Unlock, Byte Programming, Page Protect, Page Unprotect, Page Select Page Erase, and Mass Erase) displayed in Figure 21.

## **Trim Bit Data Register**

The Trim Bid Data (TRMDR) register contains the read or write data for access to the trim option bits.

Table 86. Trim Bit Data Register (TRMDR)

| BITS  | 7                     | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|-----------------------|-----|-----|-----|-----|-----|-----|-----|--|

| FIELD | TRMDR - Trim Bit Data |     |     |     |     |     |     |     |  |

| RESET | 0                     | 0   | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W                   | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  | FF7H                  |     |     |     |     |     |     |     |  |

# **Flash Option Bit Address Space**

The first two bytes of Flash program memory at addresses 0000H and 0001H are reserved for the user-programmable Flash option bits.

## Flash Program Memory Address 0000H

Table 87. Flash Option Bits at Program Memory Address 0000H

| BITS                                            | 7                    | 6      | 5       | 4     | 3      | 2   | 1        | 0   |  |  |

|-------------------------------------------------|----------------------|--------|---------|-------|--------|-----|----------|-----|--|--|

| FIELD                                           | WDT_RES              | WDT_AO | Rese    | erved | VBO_AO | FRP | Reserved | FWP |  |  |

| RESET                                           | U                    | U      | U U     |       | U      | U   | U        | U   |  |  |

| R/W                                             | R/W                  | R/W    | R/W R/W |       | R/W    | R/W | R/W      | R/W |  |  |

| ADDR                                            | Program Memory 0000H |        |         |       |        |     |          |     |  |  |

| Note: U = Unchanged by Reset. R/W = Read/Write. |                      |        |         |       |        |     |          |     |  |  |

WDT RES—Watchdog Timer Reset

0 = Watchdog Timer time-out generates an interrupt request. Interrupts must be globally enabled for the eZ8 CPU to acknowledge the interrupt request.

1 = Watchdog Timer time-out causes a system reset. This setting is the default for unprogrammed (erased) Flash.

WDT\_AO—Watchdog Timer Always ON

0 = Watchdog Timer is automatically enabled upon application of system power. Watchdog Timer can not be disabled.

1 = Watchdog Timer is enabled upon execution of the WDT instruction. Once enabled, the

is not in DEBUG mode or if the Flash Read Protect Option bit is enabled, the data is discarded.

DBG  $\leftarrow$  0AH DBG  $\leftarrow$  Program Memory Address[15:8] DBG  $\leftarrow$  Program Memory Address[7:0] DBG  $\leftarrow$  Size[15:8] DBG  $\leftarrow$  Size[7:0] DBG  $\leftarrow$  1-65536 data bytes

• **Read Program Memory (0BH)**—The Read Program Memory command reads data from Program Memory. This command is equivalent to the LDC and LDCI instructions. Data can be read 1–65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, this command returns FFH for the data.

```

DBG \leftarrow 0BH

DBG \leftarrow Program Memory Address[15:8]

DBG \leftarrow Program Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

• Write Data Memory (0CH)—The Write Data Memory command writes data to Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be written 1–65536 bytes at a time (65536 bytes can be written by setting size to 0). If the device is not in DEBUG mode or if the Flash Read Protect Option Bit is enabled, the data is discarded.

```

DBG \leftarrow 0CH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \leftarrow 1-65536 data bytes

```

• **Read Data Memory (0DH)**—The Read Data Memory command reads from Data Memory. This command is equivalent to the LDE and LDEI instructions. Data can be read 1 to 65536 bytes at a time (65536 bytes can be read by setting size to 0). If the device is not in DEBUG mode, this command returns FFH for the data.

```

DBG \leftarrow 0DH

DBG \leftarrow Data Memory Address[15:8]

DBG \leftarrow Data Memory Address[7:0]

DBG \leftarrow Size[15:8]

DBG \leftarrow Size[7:0]

DBG \rightarrow 1-65536 data bytes

```

## **OCD Status Register**

The OCD Status register reports status information about the current state of the debugger and the system.

Table 100. OCD Status Register (OCDSTAT)

| BITS  | 7   | 6    | 5      | 4        | 3 | 2 | 1 | 0 |  |  |  |  |  |

|-------|-----|------|--------|----------|---|---|---|---|--|--|--|--|--|

| FIELD | DBG | HALT | FRPENB | Reserved |   |   |   |   |  |  |  |  |  |

| RESET | 0   | 0    | 0      | 0        | 0 | 0 | 0 | 0 |  |  |  |  |  |

| R/W   | R   | R    | R      | R        | R | R | R | R |  |  |  |  |  |

DBG—Debug Status 0 = NORMAL mode 1 = DEBUG mode

HALT—HALT Mode 0 = Not in HALT mode 1 = In HALT mode

FRPENB—Flash Read Protect Option Bit Enable

0 = FRP bit enabled, that allows disabling of many OCD commands

1 = FRP bit has no effect

Reserved—0 when read

• Rotate and Shift

Tables 107 through Table 114 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |

|----------|----------|-----------------------------------------------|

|          | •        |                                               |

| ADC      | dst, src | Add with Carry                                |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |

| ADD      | dst, src | Add                                           |

| ADDX     | dst, src | Add using Extended Addressing                 |

| CP       | dst, src | Compare                                       |

| CPC      | dst, src | Compare with Carry                            |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |

| СРХ      | dst, src | Compare using Extended Addressing             |

| DA       | dst      | Decimal Adjust                                |

| DEC      | dst      | Decrement                                     |

| DECW     | dst      | Decrement Word                                |

| INC      | dst      | Increment                                     |

| INCW     | dst      | Increment Word                                |

| MULT     | dst      | Multiply                                      |

| SBC      | dst, src | Subtract with Carry                           |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |

| SUB      | dst, src | Subtract                                      |

| SUBX     | dst, src | Subtract using Extended Addressing            |

|          |          |                                               |

#### **Table 107. Arithmetic Instructions**

| Assembly             |                                                                                                                            | Address Mode |     | Opcode(s) | Fla | ıgs |               |   | - Fetch | Instr. |   |        |

|----------------------|----------------------------------------------------------------------------------------------------------------------------|--------------|-----|-----------|-----|-----|---------------|---|---------|--------|---|--------|

| Mnemonic             | Symbolic Operation                                                                                                         | dst          | src | (Hex)     | С   | z   | S             | v | D       | Н      |   | Cycles |

| AND dst, src         | $dst \gets dst \ AND \ src$                                                                                                | r            | r   | 52        | -   | *   | *             | 0 | -       | _      | 2 | 3      |

|                      |                                                                                                                            | r            | lr  | 53        | -   |     |               |   |         |        | 2 | 4      |

|                      |                                                                                                                            | R            | R   | 54        | -   |     |               |   |         |        | 3 | 3      |

|                      |                                                                                                                            | R            | IR  | 55        | -   |     |               |   |         |        | 3 | 4      |

|                      |                                                                                                                            | R            | IM  | 56        | -   |     |               |   |         |        | 3 | 3      |

|                      |                                                                                                                            | IR           | IM  | 57        | -   |     |               |   |         |        | 3 | 4      |

| ANDX dst, src        | $dst \gets dst \ AND \ src$                                                                                                | ER           | ER  | 58        | -   | *   | *             | 0 | -       | _      | 4 | 3      |

|                      |                                                                                                                            | ER           | IM  | 59        | -   |     |               |   |         |        | 4 | 3      |

| ATM                  | Block all interrupt and<br>DMA requests during<br>execution of the next 3<br>instructions                                  |              |     | 2F        | _   | _   | _             | _ | _       | _      | 1 | 2      |

| BCLR bit, dst        | dst[bit] ← 0                                                                                                               | r            |     | E2        | _   | _   | _             | _ | _       | _      | 2 | 2      |

| BIT p, bit, dst      | dst[bit] ← p                                                                                                               | r            |     | E2        | -   | -   | -             | 0 | -       | -      | 2 | 2      |

| BRK                  | Debugger Break                                                                                                             |              |     | 00        | _   | _   | _             | _ | _       | _      | 1 | 1      |

| BSET bit, dst        | dst[bit] ← 1                                                                                                               | r            |     | E2        | _   | _   | _             | 0 | _       | _      | 2 | 2      |

| BSWAP dst            | dst[7:0] ← dst[0:7]                                                                                                        | R            |     | D5        | Х   | *   | *             | 0 | _       | _      | 2 | 2      |

| BTJ p, bit, src, dst | if src[bit] = p<br>PC ← PC + X                                                                                             |              | r   | F6        | _   | _   | _             | _ | _       | _      | 3 | 3      |

|                      |                                                                                                                            |              | lr  | F7        | -   |     |               |   |         |        | 3 | 4      |

| BTJNZ bit, src, dst  |                                                                                                                            |              | r   | F6        | -   | _   | _             | _ | -       | _      | 3 | 3      |

|                      | $PC \leftarrow PC + X$                                                                                                     |              | lr  | F7        | _   |     |               |   |         |        | 3 | 4      |

| BTJZ bit, src, dst   | if src[bit] = 0                                                                                                            |              | r   | F6        | _   | _   | _             | _ | _       | _      | 3 | 3      |

|                      | $PC \leftarrow PC + X$                                                                                                     |              | lr  | F7        | -   |     |               |   |         |        | 3 | 4      |

| CALL dst             | $SP \leftarrow SP - 2$                                                                                                     | IRR          |     | D4        | _   | _   | _             | _ | _       | _      | 2 | 6      |

|                      | $ @SP \leftarrow PC \\ PC \leftarrow dst $                                                                                 | DA           |     | D6        | -   |     |               |   |         |        | 3 | 3      |

| CCF                  | C ← ~C                                                                                                                     |              |     | EF        | *   | _   | _             | _ | _       |        | 1 | 2      |

| CLR dst              | dst ← 00H                                                                                                                  | R            |     | B0        | _   | _   | _             | _ | _       | _      | 2 | 2      |

|                      |                                                                                                                            | IR           |     | B1        | -   |     |               |   |         |        | 2 | 3      |

| Flags Notation:      | <ul> <li>* = Value is a function of the result of the operation.</li> <li>- = Unaffected</li> <li>X = Undefined</li> </ul> |              |     |           |     |     | eset<br>et to |   | 0       |        |   |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

208