Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-VDFN Exposed Pad                                        |

| Supplier Device Package    | 8-QFN (5x6)                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813qb005sc |

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| On-Chip Debugger Initiated Reset                    | 26 |

|-----------------------------------------------------|----|

| Stop Mode Recovery                                  |    |

| Stop Mode Recovery Using Watchdog Timer Time-Out    |    |

| Stop Mode Recovery Using a GPIO Port Pin Transition |    |

| Stop Mode Recovery Using the External RESET Pin     |    |

| Reset Register Definitions                          |    |

| Low-Power Modes                                     |    |

| STOP Mode                                           |    |

| HALT Mode                                           |    |

| Peripheral-Level Power Control                      | 32 |

| Power Control Register Definitions                  | 32 |

| General-Purpose Input/Output                        | 35 |

| GPIO Port Availability By Device                    | 35 |

| Architecture                                        | 36 |

| GPIO Alternate Functions                            | 36 |

| Direct LED Drive                                    | 37 |

| Shared Reset Pin                                    | 37 |

| Shared Debug Pin                                    | 37 |

| Crystal Oscillator Override                         | 38 |

| 5 V Tolerance                                       |    |

| External Clock Setup                                |    |

| GPIO Interrupts                                     |    |

| GPIO Control Register Definitions                   |    |

| Port A–C Address Registers                          |    |

| Port A–C Control Registers                          |    |

| Port A–C Data Direction Sub-Registers               | 45 |

| Port A–C Alternate Function Sub-Registers           |    |

| Port A–C Input Data Registers                       |    |

| Port A–C Output Data Register                       |    |

| LED Drive Enable Register                           |    |

| LED Drive Level Low Register                        |    |

| Interrupt Controller                                |    |

| Interrupt Vector Listing                            |    |

| Architecture                                        |    |

|                                                     |    |

| Operation                                           |    |

|                                                     | 00 |

| Signal Mnemonic                                      | I/O | Description                                                                                                                                                                                                           |  |  |  |

|------------------------------------------------------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Analog                                               |     |                                                                                                                                                                                                                       |  |  |  |

| ANA[7:0]                                             | Ι   | Analog port. These signals are used as inputs to the ADC. The ANA0, ANA1, and ANA2 pins can also access the inputs and output of the integrated transimpedance amplifier.                                             |  |  |  |

| VREF                                                 | I/O | Analog-to-Digital Converter reference voltage input.                                                                                                                                                                  |  |  |  |

| Clock Input                                          |     |                                                                                                                                                                                                                       |  |  |  |

| CLKIN                                                | Ι   | Clock Input Signal. This pin can be used to input a TTL-level signal to be used as the system clock.                                                                                                                  |  |  |  |

| LED Drivers                                          |     |                                                                                                                                                                                                                       |  |  |  |

| LED                                                  | 0   | Direct LED drive capability. All port C pins have the capability to drive an LED without any other external components. These pins have programmable drive strengths set by the GPIO block.                           |  |  |  |

| On-Chip Debugger                                     |     |                                                                                                                                                                                                                       |  |  |  |

| DBG                                                  | I/O | Debug. This signal is the control and data input and output to and from the OCD.                                                                                                                                      |  |  |  |

|                                                      |     | <b>Caution:</b> The DBG pin is open-drain and requires an external pull                                                                                                                                               |  |  |  |

|                                                      |     | up resistor to ensure proper operation.                                                                                                                                                                               |  |  |  |

| Reset                                                |     |                                                                                                                                                                                                                       |  |  |  |

| RESET                                                | I/O | RESET. Generates a reset when asserted (driven Low). Also serves as a reset indicator; the Z8 Encore! XP forces this pin Low when in reset. This pin is open-drain and features an enabled internal pull-up resistor. |  |  |  |

| Power Supply                                         |     |                                                                                                                                                                                                                       |  |  |  |

| V <sub>DD</sub>                                      | I   | Digital Power Supply.                                                                                                                                                                                                 |  |  |  |

| AV <sub>DD</sub>                                     | Ι   | Analog Power Supply.                                                                                                                                                                                                  |  |  |  |

| V <sub>SS</sub>                                      | I   | Digital Ground.                                                                                                                                                                                                       |  |  |  |

| AV <sub>SS</sub>                                     | I   | Analog Ground.                                                                                                                                                                                                        |  |  |  |

| Note: The AV <sub>DD</sub> and A<br>PB7 on 28-pin pa |     | nals are available only in 28-pin packages with ADC. They are replaced by PB6 and without ADC.                                                                                                                        |  |  |  |

# **Pin Characteristics**

Table 4 provides detailed information about the characteristics for each pin available on Z8 Encore! XP F0823 Series 20- and 28-pin devices. Data in Table 4 is sorted alphabetically by the pin symbol mnemonic.

#### STOP—Stop Mode Recovery Indicator

If this bit is set to 1, a Stop Mode Recovery is occurred. If the STOP and WDT bits are both set to 1, the Stop Mode Recovery occurred because of a WDT time-out. If the STOP bit is 1 and the WDT bit is 0, the Stop Mode Recovery was not caused by a WDT time-out. This bit is reset by a POR or a WDT time-out that occurred while not in STOP mode. Reading this register also resets this bit.

WDT-Watchdog Timer time-out Indicator

If this bit is set to 1, a WDT time-out occurred. A POR resets this pin. A Stop Mode Recovery from a change in an input pin also resets this bit. Reading this register resets this bit. This read must occur before clearing the WDT interrupt.

#### EXT-External Reset Indicator

If this bit is set to 1, a Reset initiated by the external  $\overline{\text{RESET}}$  pin occurred. A Power-On Reset or a Stop Mode Recovery from a change in an input pin resets this bit. Reading this register resets this bit.

Reserved-0 when read

PA0 and PA6 contain two different timer functions, a timer input and a complementary timer output. Both of these functions require the same GPIO configuration, the selection between the two is based on the timer mode. For more details, see Timers on page 67.

**Caution:** For pin with multiple alternate functions, it is recommended to write to the AFS1 and AFS2 sub-registers before enabling the alternate function via the AF sub-register. This prevents spurious transitions through unwanted alternate function modes.

## **Direct LED Drive**

The Port C pins provide a current sinked output capable of driving an LED without requiring an external resistor. The output sinks current at programmable levels of 3 mA, 7 mA, 13 mA, and 20 mA. This mode is enabled through the Alternate Function sub-register AFS1 and is programmable through the LED control registers. The LED Drive Enable (LEDEN) register turns on the drivers. The LED Drive Level (LEDLVLH and LEDLVLL) registers select the sink current.

For correct function, the LED anode must be connected to  $V_{DD}$  and the cathode to the GPIO pin. Using all Port C pins in LED drive mode with maximum current can result in excessive total current. For the maximum total current for the applicable package, see Electrical Characteristics on page 193.

## **Shared Reset Pin**

On the 8-pin product versions, the reset pin is shared with PA2, but the pin is not limited to output-only when in GPIO mode.

**Caution:** If PA2 on the 8-pin product is reconfigured as an input, take care that no external stimulus drives the pin Low during any reset sequence. Since PA2 returns to its RESET alternate function during system resets, driving it Low holds the chip in a reset state until the pin is released.

## **Shared Debug Pin**

On the 8-pin version of this device only, the Debug pin shares function with the PA0 GPIO pin. This pin performs as a general purpose input pin on power-up, but the debug logic monitors this pin during the reset sequence to determine if the unlock sequence occurs. If the unlock sequence is present, the debug function is unlocked and the pin no longer func-

| Port   | Pin | Mnemonic    | Alternate Function Description          | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------|-----------------------------------------|-----------------------------------------|

| Port A | PA0 | T0IN/T0OUT* | Timer 0 Input/Timer 0 Output Complement | N/A                                     |

|        |     | Reserved    |                                         | -                                       |

|        | PA1 | TOOUT       | Timer 0 Output                          | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA2 | DE0         | UART 0 Driver Enable                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA3 | CTS0        | UART 0 Clear to Send                    | -                                       |

|        |     | Reserved    |                                         | -                                       |

|        | PA4 | RXD0/IRRX0  | UART 0 / IrDA 0 Receive Data            | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA5 | TXD0/IRTX0  | UART 0 / IrDA 0 Transmit Data           | -                                       |

|        |     | Reserved    |                                         |                                         |

|        | PA6 | T1IN/T1OUT* | Timer 1 Input/Timer 1 Output Complement |                                         |

|        |     | Reserved    |                                         |                                         |

|        | PA7 | T1OUT       | Timer 1 Output                          | _                                       |

|        |     | Reserved    |                                         |                                         |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts)

**Note:** Because there is only a single alternate function for each Port A pin, the Alternate Function Set registers are not implemented for Port A. Enabling alternate function selections as described in Port A–C Alternate Function Sub-Registers automatically enables the associated alternate function.

\* Whether PA0/PA6 take on the timer input or timer output complement function depends on the timer configuration as described in Timer Pin Signal Operation on page 79.

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

### **COUNTER Mode**

In COUNTER mode, the timer counts input transitions from a GPIO port pin. The timer input is taken from the GPIO port pin Timer Input alternate function. The TPOL bit in the Timer Control register selects whether the count occurs on the rising edge or the falling edge of the timer input signal. In COUNTER mode, the prescaler is disabled.

**Caution:** *The input frequency of the timer input signal must not exceed one-fourth the system clock frequency.*

Upon reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COUNTER mode.

- Select either the rising edge or falling edge of the Timer Input signal for the count. This selection also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This only affects the first pass in COUNTER mode. After the first timer Reload in COUNTER mode, counting always begins at the reset value of 0001H. In COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer.

In COUNTER mode, the number of Timer Input transitions since the timer start is given by the following equation:

COUNTER Mode Timer Input Transitions = Current Count Value – Start Value

### **COMPARATOR COUNTER Mode**

In COMPARATOR COUNTER mode, the timer counts input transitions from the analog comparator output. The TPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the falling edge of the comparator output signal. In COMPARATOR COUNTER mode, the prescaler is disabled.

**Caution:** *The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.*

After reaching the Reload value stored in the Timer Reload High and Low Byte registers, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer Reload.

Follow the steps below for configuring a timer for COMPARATOR COUNTER mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for COMPARATOR COUNTER mode.

- Select either the rising edge or falling edge of the comparator output signal for the count. This also sets the initial logic level (High or Low) for the Timer Output alternate function. However, the Timer Output function is not required to be enabled.

- 2. Write to the Timer High and Low Byte registers to set the starting count value. This action only affects the first pass in COMPARATOR COUNTER mode. After the first timer Reload in COMPARATOR COUNTER mode, counting always begins at the reset value of 0001H. Generally, in COMPARATOR COUNTER mode the Timer High and Low Byte registers must be written with the value 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions = Current Count Value – Start Value

- Configure the timer for CAPTURE/COMPARE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.By default, the timer interrupt are generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Counting begins on the first appropriate transition of the Timer Input signal. No interrupt is generated by this first edge.

In CAPTURE/COMPARE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

## **Reading the Timer Count Values**

The current count value in the timers can be read while counting (enabled). This capability has no effect on timer operation. When the timer is enabled and the Timer High Byte register is read, the contents of the Timer Low Byte register are placed in a holding register. A subsequent read from the Timer Low Byte register returns the value in the hold-ing register. This operation allows accurate reads of the full 16-bit timer count value while enabled. When the timers are not enabled, a read from the Timer Low Byte register returns the actual value in the counter.

### **Timer Pin Signal Operation**

Timer Output is a GPIO port pin alternate function. The Timer Output is toggled every time the counter is reloaded.

The timer input can be used as a selectable counting source. It shares the same pin as the complementary timer output. When selected by the GPIO Alternate Function Registers, this pin functions as a timer input in all modes except for the DUAL PWM OUTPUT mode. For this mode, there is no timer input available.

#### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 =Count occurs on the rising edge of the Timer Input signal

- 1 = Count occurs on the falling edge of the Timer Input signal

#### **PWM SINGLE OUTPUT Mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARE Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### GATED Mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

in hardware, software or some combination of the two, depending on the multiprocessor configuration bits. In general, the address compare feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to other devices on the multi-node network. The following three MULTIPROCESSOR modes are available in hardware:

- Interrupt on all address bytes

- Interrupt on matched address bytes and correctly framed data bytes

- Interrupt only on correctly framed data bytes

These modes are selected with MPMD[1:0] in the UART Control 1 Register. For all multiprocessor modes, bit MPEN of the UART Control 1 Register must be set to 1.

The first scheme is enabled by writing 01b to MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, while data bytes never cause an interrupt. The interrupt service routine must manually check the address byte that caused triggered the interrupt. If it matches the UART address, the software clears MPMD[0]. Each new incoming byte interrupts the CPU. The software is responsible for determining the end of the frame. It checks for the end-of-frame by reading the MPRX bit of the UART Status 1 Register for each incoming byte. If MPRX=1, a new frame has begun. If the address of this new frame is different from the UART's address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive until the next address byte. If the new frame's address matches the UART's, the data in the new frame is processed as well.

The second scheme requires the following: set MPMD[1:0] to 10B and write the UART's address into the UART Address Compare register. This mode introduces additional hardware control, interrupting only on frames that match the UART's address. When an incoming address byte does not match the UART's address, it is ignored. All successive data bytes in this frame are also ignored. When a matching address byte occurs, an interrupt is issued and further interrupts now occur on each successive data byte. When the first data byte in the frame is read, the NEWFRM bit of the UART Status 1 Register is asserted. All successive data bytes have NEWFRM=0. When the next address byte occurs, the hardware compares it to the UART's address. If there is a match, the interrupts continues and the NEWFRM bit is set for the first byte of the new frame. If there is no match, the UART ignores all incoming bytes until the next address match.

The third scheme is enabled by setting MPMD[1:0] to 11b and by writing the UART's address into the UART Address Compare Register. This mode is identical to the second scheme, except that there are no interrupts on address bytes. The first data byte of each frame remains accompanied by a NEWFRM assertion.

### **Transmitter Interrupts**

The transmitter generates a single interrupt when the Transmit Data Register Empty bit (TDRE) is set to 1. This indicates that the transmitter is ready to accept new data for transmission. The TDRE interrupt occurs after the Transmit shift register has shifted the first bit of data out. The Transmit Data register can now be written with the next character to send. This action provides 7 bit periods of latency to load the Transmit Data register before the Transmit shift register completes shifting the current character. Writing to the UART Transmit Data register clears the TDRE bit to 0.

#### **Receiver Interrupts**

The receiver generates an interrupt when any of the following occurs:

• A data byte is received and is available in the UART Receive Data register. This interrupt can be disabled independently of the other receiver interrupt sources. The received data interrupt occurs after the receive character has been received and placed in the Receive Data register. To avoid an overrun error, software must respond to this received data available condition before the next character is completely received.

**Note:** In MULTIPROCESSOR mode (MPEN = 1), the receive data interrupts are dependent on the multiprocessor configuration and the most recent address byte.

- A break is received

- An overrun is detected

- A data framing error is detected

#### **UART Overrun Errors**

When an overrun error condition occurs the UART prevents overwriting of the valid data currently in the Receive Data register. The Break Detect and Overrun status bits are not displayed until after the valid data has been read.

After the valid data has been read, the UART Status 0 register is updated to indicate the overrun condition (and Break Detect, if applicable). The RDA bit is set to 1 to indicate that the Receive Data register contains a data byte. However, because the overrun error occurred, this byte cannot contain valid data and must be ignored. The BRKD bit indicates if the overrun was caused by a break condition on the line. After reading the status byte indicating an overrun error, the Receive Data register must be read again to clear the error bits is the UART Status 0 register. Updates to the Receive Data register occur only when the next data word is received.

#### **UART Data and Error Handling Procedure**

Figure 15 displays the recommended procedure for use in UART receiver interrupt service routines.

(BRG[15:0]) that sets the data transmission rate (baud rate) of the UART. The UART data rate is calculated using the following equation:

UART Data Rate (bits/s) =  $\frac{\text{System Clock Frequency (Hz)}}{16 \times \text{UART Baud Rate Divisor Value}}$

When the UART is disabled, the Baud Rate Generator functions as a basic 16-bit timer with interrupt on time-out. Follow the steps below to configure the Baud Rate Generator as a timer with interrupt on time-out:

- 1. Disable the UART by clearing the REN and TEN bits in the UART Control 0 register to 0.

- 2. Load the acceptable 16-bit count value into the UART Baud Rate High and Low Byte registers.

- 3. Enable the Baud Rate Generator timer function and associated interrupt by setting the BIRQ bit in the UART Control 1 register to 1.

When configured as a general purpose timer, the interrupt interval is calculated using the following equation:

Interrupt Interval (s) = System Clock Period (s)  $\times$  BRG[15:0]

## **UART Control Register Definitions**

The UART control registers support the UART and the associated Infrared Encoder/ Decoders. For more information on the infrared operation, see Infrared Encoder/Decoder on page 113.

## **UART Transmit Data Register**

Data bytes written to the UART Transmit Data register (Table 62) are shifted out on the TXDx pin. The Write-only UART Transmit Data register shares a Register File address with the read-only UART Receive Data register.

Table 62. UART Transmit Data Register (U0TXD)

| BITS  | 7    | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-------|------|---|---|---|---|---|---|---|

| FIELD | TXD  |   |   |   |   |   |   |   |

| RESET | Х    | Х | Х | Х | Х | Х | Х | Х |

| R/W   | W    | W | W | W | W | W | W | W |

| ADDR  | F40H |   |   |   |   |   |   |   |

TXD—Transmit Data

UART transmitter data byte to be shifted out through the TXDx pin.

baud rate clocks to plus eight baud rate clocks around the expected time of an incoming pulse. If an incoming pulse is detected inside this window this process is repeated. If the incoming data is a logical 1 (no pulse), the Endec returns to the initial state and waits for the next falling edge. As each falling edge is detected, the Endec clock counter is reset, resynchronizing the Endec to the incoming signal, allowing the Endec to tolerate jitter and baud rate errors in the incoming datastream. Resynchronizing the Endec does not alter the operation of the UART, which ultimately receives the data. The UART is only synchronized to the incoming data stream when a Start bit is received.

## Infrared Encoder/Decoder Control Register Definitions

All Infrared Endec configuration and status information is set by the UART control registers as defined in Universal Asynchronous Receiver/Transmitter on page 93.

**Caution:** To prevent spurious signals during IrDA data transmission, set the IREN bit in the UART Control 1 register to 1 to enable the Infrared Encoder/Decoder before enabling the GPIO port alternate function for the corresponding pin.

# Comparator

Z8 Encore! XP<sup>®</sup> F0823 Series devices feature a general purpose comparator that compares two analog input signals. A GPIO (CINP) pin provides the positive comparator input. The negative input (CINN) can be taken from either an external GPIO pin or an internal reference. The output is available as an interrupt source or can be routed to an external pin using the GPIO multiplex. The features of Comparator include:

- Two inputs which can be connected up using the GPIO multiplex (MUX)

- One input can be connected to a programmable internal reference

- One input can be connected to the on-chip temperature sensor

- Output can be either an interrupt source or an output to an external pin

## Operation

One of the comparator inputs can be connected to an internal reference which is a user selectable reference that is user programmable with 200 mV resolution.

The comparator can be powered down to save on supply current. For details, see Power Control Register 0 on page 32.

**Caution:** Because of the propagation delay of the comparator, it is not recommended to enable the comparator without first disabling interrupts and waiting for the comparator output to settle. Doing so can result in spurious interrupts after comparator enabling. The following example shows how to safely enable the comparator:

```

di

ld cmp0

nop

; wait for output to settle

clr irq0 ; clear any spurious interrupts pending

ei

```

## **Comparator Control Register Definitions**

## **Comparator Control Register**

The Comparator Control register (CMPCTL) configures the comparator inputs and sets the value of the internal voltage reference.

## Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

130

Figure 20. Flash Memory Arrangement

# **Flash Information Area**

The Flash information area is separate from program memory and is mapped to the address range FE00H to FFFFH. Not all these addresses are accessible. Factory trim values for the analog peripherals are stored here. Factory calibration data for the ADC is also stored here.

### Table 95. Serialization Data Locations

| Info Page<br>Address | Memory Address | Usage                                    |

|----------------------|----------------|------------------------------------------|

| 1C                   | FE1C           | Serial Number Byte 3 (most significant)  |

| 1D                   | FE1D           | Serial Number Byte 2                     |

| 1E                   | FE1E           | Serial Number Byte 1                     |

| 1F                   | FE1F           | Serial Number Byte 0 (least significant) |

## **Randomized Lot Identifier**

## Table 96. Lot Identification Number (RAND\_LOT)

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|--|--|

| FIELD     | RAND_LOT                                        |     |     |     |     |     |     |     |  |  |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |  |  |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Interspersed throughout Information Page Memory |     |     |     |     |     |     |     |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |  |  |

RAND LOT-Randomized Lot ID

The randomized lot ID is a 32 byte binary value that changes for each production lot.

#### Table 97. Randomized Lot ID Locations

| Info Page<br>Address | Memory<br>Address | Usage                                        |

|----------------------|-------------------|----------------------------------------------|

| 3C                   | FE3C              | Randomized Lot ID Byte 31 (most significant) |

| 3D                   | FE3D              | Randomized Lot ID Byte 30                    |

| 3E                   | FE3E              | Randomized Lot ID Byte 29                    |

| 3F                   | FE3F              | Randomized Lot ID Byte 28                    |

| 58                   | FE58              | Randomized Lot ID Byte 27                    |

| 59                   | FE59              | Randomized Lot ID Byte 26                    |

| 5A                   | FE5A              | Randomized Lot ID Byte 25                    |

| 5B                   | FE5B              | Randomized Lot ID Byte 24                    |

### Table 119. Power Consumption (Continued)

|                    |                 | V <sub>DE</sub>      | <sub>o</sub> = 2.7 V to 3    | 3.6 V    |       |                        |  |  |  |

|--------------------|-----------------|----------------------|------------------------------|----------|-------|------------------------|--|--|--|

|                    |                 |                      | Maximum <sup>2</sup> Maximum |          |       |                        |  |  |  |

| Symbol             | Parameter       | Typical <sup>1</sup> | Std Temp                     | Ext Temp | Units | Conditions             |  |  |  |

| I <sub>DD</sub> BG | Band Gap Supply | 320                  | 480                          | 500      | μA    | For 20-/28-pin devices |  |  |  |

|                    | Current         |                      |                              |          |       | For 8-pin devices      |  |  |  |

| Notes              |                 |                      |                              |          |       |                        |  |  |  |

Typical conditions are defined as V<sub>DD</sub> = 3.3 V and +30 °C.

Standard temperature is defined as T<sub>A</sub> = 0 °C to +70 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

Extended temperature is defined as T<sub>A</sub> = -40 °C to +105 °C; these values not tested in production for worst case behavior, but are derived from product characterization and provided for design guidance only.

4. For this block to operate, the bandgap circuit is automatically turned on and must be added to the total supply current. This bandgap current is only added once, regardless of how many peripherals are using it.

# **AC Characteristics**

The section provides information about the AC characteristics and timing. All AC timing information assumes a standard load of 50 pF on all outputs.

|                                   |                                                                                                                                                                | V <sub>DD</sub> = 2.7 V to 3.6 V<br>T <sub>A</sub> = -40 °C to +105 °C<br>(unless otherwise<br>stated) |                   |       |                                           |  |  |  |  |  |

|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------------------|-------|-------------------------------------------|--|--|--|--|--|

| Symbol                            | Parameter                                                                                                                                                      | Minimum                                                                                                | Maximum           | Units | Conditions                                |  |  |  |  |  |

| F <sub>SYSCLK</sub>               | System Clock Frequency                                                                                                                                         | _                                                                                                      | 20.0 <sup>1</sup> | MHz   | Read-only from Flash memory               |  |  |  |  |  |

|                                   |                                                                                                                                                                | 0.032768                                                                                               | 20.0 <sup>1</sup> | MHz   | Program or erasure of the<br>Flash memory |  |  |  |  |  |

| T <sub>XIN</sub>                  | System Clock Period                                                                                                                                            | 50                                                                                                     | _                 | ns    | T <sub>CLK</sub> = 1/F <sub>sysclk</sub>  |  |  |  |  |  |

| T <sub>XINH</sub>                 | System Clock High Time                                                                                                                                         | 20                                                                                                     | 30                | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| T <sub>XINL</sub>                 | System Clock Low Time                                                                                                                                          | 20                                                                                                     | 30                | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| T <sub>XINR</sub>                 | System Clock Rise Time                                                                                                                                         | -                                                                                                      | 3                 | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| T <sub>XINF</sub>                 | System Clock Fall Time                                                                                                                                         | - 3                                                                                                    |                   | ns    | T <sub>CLK</sub> = 50 ns                  |  |  |  |  |  |

| <sup>1</sup> System 0<br>Table 12 | <sup>1</sup> System Clock Frequency is limited by the Internal Precision Oscillator on the Z8 Encore! XP <sup>®</sup> F0823 Series. See Table 121 on page 198. |                                                                                                        |                   |       |                                           |  |  |  |  |  |

#### Table 120. AC Characteristics

# Packaging

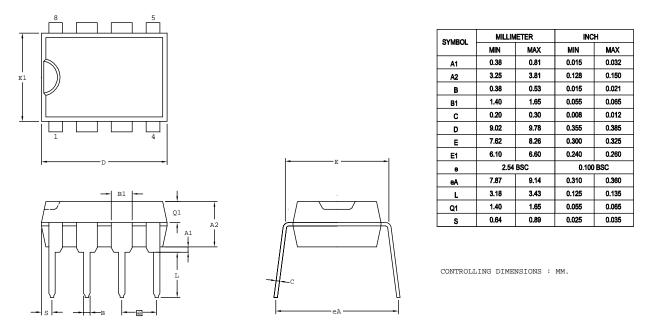

Figure 34 displays the 8-pin Plastic Dual Inline Package (PDIP) available for the Z8 Encore!  $XP^{\textcircled{R}}$  F0823 Series devices.

Figure 34. 8-Pin Plastic Dual Inline Package (PDIP)

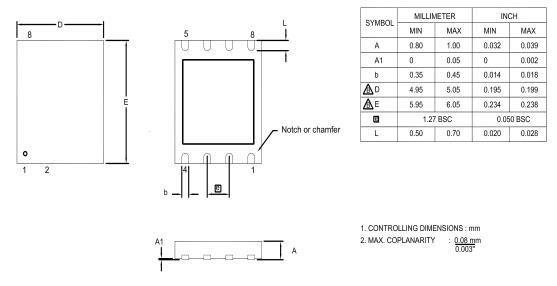

Figure 36 displays the 8-pin Quad Flat No-Lead package (QFN)/MLF-S available for the Z8 Encore! XP F0823 Series devices. This package has a footprint identical to that of the 8-pin SOIC, but with a lower profile.

Figure 36. 8-Pin Quad Flat No-Lead Package (QFN)/MLF-S

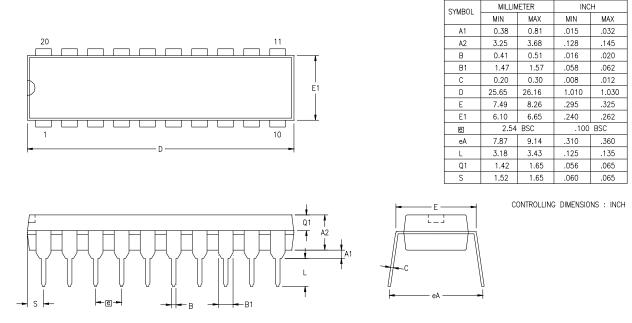

Figure 37 displays the 20-pin Plastic Dual Inline Package (PDIP) available for Z8 Encore! XP F0823 Series devices.

Figure 37. 20-Pin Plastic Dual Inline Package (PDIP)