Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |  |  |

|----------------------------|-----------------------------------------------------------|--|--|

| Product Status             | Obsolete                                                  |  |  |

| Core Processor             | eZ8                                                       |  |  |

| Core Size                  | 8-Bit                                                     |  |  |

| Speed                      | 5MHz                                                      |  |  |

| Connectivity               | IrDA, UART/USART                                          |  |  |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |  |  |

| Number of I/O              | 6                                                         |  |  |

| Program Memory Size        | 8KB (8K x 8)                                              |  |  |

| Program Memory Type        | FLASH                                                     |  |  |

| EEPROM Size                | -                                                         |  |  |

| RAM Size                   | 1K x 8                                                    |  |  |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |  |  |

| Data Converters            | -                                                         |  |  |

| Oscillator Type            | Internal                                                  |  |  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |  |  |

| Mounting Type              | Surface Mount                                             |  |  |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |  |  |

| Supplier Device Package    | -                                                         |  |  |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sb005sc |  |  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reflects a change to this document from its previous revision. For more details, refer to the corresponding pages and appropriate links in the table below.

| Date             | Revision<br>Level | Description                                                                                                                                                                                                       | Page No                              |

|------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|

| March<br>2008    | 14                | Changed title to Z8 Encore! XP F0823 Series and the contents to match the title.                                                                                                                                  | •                                    |

| December<br>2007 | 13                | Updated title from Z8 Encore! 8K and 4K Series to Z8<br>Encore! XP Z8F0823 Series. Updated Figure 3, Table<br>15, Table 35, Table 59 through Table 61, Table 119,<br>and Part Number Suffix Designations section. | 8, 39,<br>59, 91,<br>196, and<br>226 |

| August<br>2007   | 12                | Updated Table 1, Table 16, and Program Memory section.                                                                                                                                                            | 2, 42,<br>and 13                     |

| June 2007        | 11                | Updated to combine Z8 Encore! 8K and Z8 Encore! 4K Series.                                                                                                                                                        | All                                  |

| December<br>2006 | 10                | Updated Ordering Information chapter.                                                                                                                                                                             | 217                                  |

## **Internal Precision Oscillator**

The internal precision oscillator (IPO) is a trimmable clock source that requires no external components.

## 10-Bit Analog-to-Digital Converter

The optional analog-to-digital converter (ADC) converts an analog input signal to a 10-bit binary number. The ADC accepts inputs from eight different analog input pins in both single-ended and differential modes.

## **Analog Comparator**

The analog comparator compares the signal at an input pin with either an internal programmable voltage reference or a second input pin. The comparator output can be used to drive either an output pin or to generate an interrupt.

## **Universal Asynchronous Receiver/Transmitter**

The UART is full-duplex and capable of handling asynchronous data transfers. The UART supports 8- and 9-bit data modes and selectable parity. The UART also supports multi-drop address processing in hardware. The UART baud rate generator can be configured and used as a basic 16-bit timer.

## Timers

Two enhanced 16-bit reloadable timers can be used for timing/counting events or for motor control operations. These timers provide a 16-bit programmable reload counter and operate in ONE-SHOT, CONTINUOUS, GATED, CAPTURE, CAPTURE RESTART, COMPARE, CAPTURE AND COMPARE, PWM SINGLE OUTPUT, and PWM DUAL OUTPUT modes.

## Interrupt Controller

Z8 Encore! XP<sup>®</sup> F0823 Series products support up to 20 interrupts. These interrupts consist of eight internal peripheral interrupts and 12 general-purpose I/O pin interrupt sources. The interrupts have three levels of programmable interrupt priority.

Note:

\*Analog input alternate functions (ANA) are not available on the Z8F0x13 devices.

# **Signal Descriptions**

Table 3 lists the Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series signals. To determine the signals available for the specific package styles, see Pin Configurations on page 7.

#### Table 3. Signal Descriptions

| Signal Mnemonic                                       | I/O     | Description                                                                                                                                                                                                                                                                                             |

|-------------------------------------------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| General-Purpose I/C                                   | ) Ports | A–D                                                                                                                                                                                                                                                                                                     |

| PA[7:0]                                               | I/O     | Port A. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| PB[7:0]                                               | I/O     | Port B. These pins are used for general-purpose I/O. PB6 and PB7 are available only in those devices without an ADC.                                                                                                                                                                                    |

| PC[7:0]                                               | I/O     | Port C. These pins are used for general-purpose I/O.                                                                                                                                                                                                                                                    |

| Note: PB6 and PB7 are<br>replaced by AV <sub>DI</sub> |         | /ailable in 28-pin packages without ADC. In 28-pin packages with ADC, they are $V_{\rm SS}.$                                                                                                                                                                                                            |

| UART Controllers                                      |         |                                                                                                                                                                                                                                                                                                         |

| TXD0                                                  | 0       | Transmit Data. This signal is the transmit output from the UART and IrDA.                                                                                                                                                                                                                               |

| RXD0                                                  | I       | Receive Data. This signal is the receive input for the UART and IrDA.                                                                                                                                                                                                                                   |

| CTS0                                                  | I       | Clear To Send. This signal is the flow control input for the UART.                                                                                                                                                                                                                                      |

| DE                                                    | 0       | Driver Enable. This signal allows automatic control of external RS-485 drivers. This signal is approximately the inverse of the TXE (Transmit Empty) bit in the UART Status 0 register. The DE signal can be used to ensure the external RS-485 driver is enabled when data is transmitted by the UART. |

| Timers                                                |         |                                                                                                                                                                                                                                                                                                         |

| T0OUT/T1OUT                                           | 0       | Timer Output 0–1. These signals are output from the timers.                                                                                                                                                                                                                                             |

| T0OUT/T1OUT                                           | 0       | Timer Complement Output 0–1. These signals are output from the timers in PWM Dual Output mode.                                                                                                                                                                                                          |

| T0IN/T1IN                                             | I       | Timer Input 0–1. These signals are used as the <u>capture</u> , gating and counter inputs. The T0IN signal is multiplexed T0OUT signals.                                                                                                                                                                |

| Comparator                                            |         |                                                                                                                                                                                                                                                                                                         |

| CINP/CINN                                             | Ι       | Comparator Inputs. These signals are the positive and negative inputs to the comparator.                                                                                                                                                                                                                |

| COUT                                                  | 0       | Comparator Output. This is the output of the comparator.                                                                                                                                                                                                                                                |

| Symbol<br>Mnemonic | Direction | Reset<br>Direction                                                      | Active Low<br>or Active<br>High | Tristate<br>Output | Internal Pull-up<br>or Pull-down                        | Schmitt-<br>Trigger<br>Input | Open Drain<br>Output                                    | 5 V<br>Tolerance                   |

|--------------------|-----------|-------------------------------------------------------------------------|---------------------------------|--------------------|---------------------------------------------------------|------------------------------|---------------------------------------------------------|------------------------------------|

| PA0/DBG            | I/O       | I (but can<br>change<br>during<br>reset if key<br>sequence<br>detected) | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| PA1                | I/O       | Ι                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| RESET/<br>PA2      | I/O       | I/O<br>(defaults<br>to RESET)                                           | N/A                             | Yes                | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes                          | Programmable<br>for PA2 <u>; always</u><br>on for RESET | Yes, unless<br>pull-ups<br>enabled |

| PA[5:3]            | I/O       | I                                                                       | N/A                             | Yes                | Programmable<br>Pull-up                                 | Yes                          | Yes,<br>Programmable                                    | Yes, unless<br>pull-ups<br>enabled |

| VDD                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

| VSS                | N/A       | N/A                                                                     | N/A                             | N/A                | N/A                                                     | N/A                          | N/A                                                     | N/A                                |

## Table 5. Pin Characteristics (8-Pin Devices)

Writing a 1 to the IRQE bit in the Interrupt Control register

Interrupts are globally disabled by any of the following actions:

- Execution of a Disable Interrupt (DI) instruction

- eZ8 CPU acknowledgement of an interrupt service request from the interrupt controller

- Writing a 0 to the IRQE bit in the Interrupt Control register

- Reset

- Execution of a Trap instruction

- Illegal Instruction Trap

- Primary Oscillator Fail Trap

- Watchdog Timer Oscillator Fail Trap

#### **Interrupt Vectors and Priority**

The interrupt controller supports three levels of interrupt priority. Level 3 is the highest priority, Level 2 is the second highest priority, and Level 1 is the lowest priority. If all interrupts are enabled with identical interrupt priority (for example, all as Level 2 interrupts), the interrupt priority is assigned from highest to lowest as specified in Table 33 on page 54. Level 3 interrupts are always assigned higher priority than Level 2 interrupts which, in turn, always are assigned higher priority than Level 1 interrupts. Within each interrupt priority level (Level 1, Level 2, or Level 3), priority is assigned as specified in Table 33. Reset, Watchdog Timer interrupt (if enabled), Primary Oscillator Fail Trap, Watchdog Timer Oscillator Fail Trap, and Illegal Instruction Trap always have highest (Level 3) priority.

#### Interrupt Assertion

Interrupt sources assert their interrupt requests for only a single system clock period (single pulse). When the interrupt request is acknowledged by the eZ8 CPU, the corresponding bit in the Interrupt Request register is cleared until the next interrupt occurs. Writing a 0 to the corresponding bit in the Interrupt Request register likewise clears the interrupt request.

**Caution:** The following coding style that clears bits in the Interrupt Request registers is not recommended. All incoming interrupts received between execution of the first LDX command and the final LDX command are lost.

Poor coding style that can result in lost interrupt requests: LDX r0, IRQ0 AND r0, MASK LDX IRQ0, r0

# Timers

Z8 Encore! XP<sup>®</sup> F0823 Series products contain up to two 16-bit reloadable timers that are used for timing, event counting, or generation of PWM signals. The timers' features include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the baud rate generator of the UART (if unused) also provides basic timing functionality. For information on using the baud rate generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 93.

## Architecture

Figure 9 displays the architecture of the timers. Timer Block Timer Data Bus Control Block Control Timer 16-Bit Interrupt, Compare Interrupt **Reload Register** PWM, and Timer Timer Output Output System Control Timer Clock 16-Bit Counter I Output with Prescaler Timer Complement Input Compare I Gate 16-Bit Input PWM/Compare Capture Input

Figure 9. Timer Block Diagram

If an initial starting value other than 0001H is loaded into the Timer High and Low Byte registers, use the ONE-SHOT mode equation to determine the first PWM time-out period. If TPOL is set to 0, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{\text{Reload Value} - \text{PWM Value}}{\text{Reload Value}} \times 100$

If TPOL is set to 1, the ratio of the PWM output High time to the total period is represented by the following equation:

PWM Output High Time Ratio (%) =  $\frac{PWM \text{ Value}}{\text{Reload Value}} \times 100$

#### PWM Dual Output Mode

In PWM DUAL OUTPUT mode, the timer outputs a PWM output signal pair (basic PWM signal and its complement) through two GPIO port pins. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

The timer also generates a second PWM output signal Timer Output Complement. The Timer Output Complement is the complement of the Timer Output PWM signal. A programmable deadband delay can be configured to time delay (0 to 128 system clock cycles) PWM output transitions on these two pins from a low to a high (inactive to active). This ensures a time gap between the deassertion of one PWM output to the assertion of its complement.

Follow the steps below for configuring a timer for PWM Dual Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM Dual Output mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register

- Set the prescale value

of the Timer Input signal. When the Capture event occurs, an interrupt is generated and the timer continues counting. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

The timer continues counting up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt and continues counting. The INPCAP bit in TxCTL1 register clears indicating the timer interrupt is not because of an input capture event.

Follow the steps below for configuring a timer for CAPTURE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for CAPTURE mode

- Set the prescale value

- Set the Capture edge (rising or falling) for the Timer Input

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. Clearing these registers allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =  $\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### **CAPTURE RESTART Mode**

In CAPTURE RESTART mode, the current timer count value is recorded when the acceptable external Timer Input transition occurs. The Capture count value is written to the Timer PWM High and Low Byte Registers. The timer input is the system clock. The TPOL bit in the Timer Control register determines if the Capture occurs on a rising edge or a falling edge of the Timer Input signal. When the Capture event occurs, an interrupt is

timer value is not reset to 0001H). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) upon Compare.

If the Timer reaches FFFFH, the timer rolls over to 0000H and continue counting. Follow the steps below to configure a timer for COMPARE mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for Compare mode.

- Set the prescale value.

- Set the initial logic level (High or Low) for the Timer Output alternate function, if appropriate.

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Compare value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer and initiate counting.

In COMPARE mode, the system clock always provides the timer input. The Compare time can be calculated by the following equation:

$COMPARE Mode Time (s) = \frac{(Compare Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$

#### GATED Mode

In GATED mode, the timer counts only when the Timer Input signal is in its active state (asserted), as determined by the TPOL bit in the Timer Control register. When the Timer Input signal is asserted, counting begins. A timer interrupt is generated when the Timer Input signal is deasserted or a timer Reload occurs. To determine if a Timer Input signal deassertion generated the interrupt, read the associated GPIO input value and compare to the value stored in the TPOL bit.

The timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. When reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes (assuming the Timer Input signal remains asserted). Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state (from Low to High or from High to Low) at timer reset.

### **External Driver Enable**

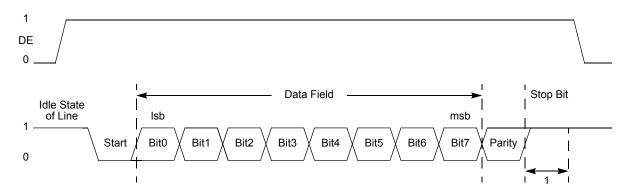

The UART provides a Driver Enable (DE) signal for off-chip bus transceivers. This feature reduces the software overhead associated with using a GPIO pin to control the transceiver when communicating on a multi-transceiver bus, such as RS-485.

Driver Enable is an active High signal that envelopes the entire transmitted data frame including parity and Stop bits as displayed in Figure 14. The Driver Enable signal asserts when a byte is written to the UART Transmit Data register. The Driver Enable signal asserts at least one UART bit period and no greater than two UART bit periods before the Start bit is transmitted. This allows a setup time to enable the transceiver. The Driver Enable signal deasserts one system clock period after the final Stop bit is transmitted. This one system clock delay allows both time for data to clear the transceiver before disabling it, as well as the ability to determine if another character follows the current character. In the event of back to back characters (new data must be written to the Transmit Data Register before the previous character is completely transmitted) the DE signal is not deasserted between characters. The DEPOL bit in the UART Control Register 1 sets the polarity of the Driver Enable signal.

The Driver Enable to Start bit setup time is calculated as follows: (2)

$$\left(\frac{1}{\text{Baud Rate (Hz)}}\right) \le \text{DE to Start Bit Setup Time (s)} \le \left(\frac{2}{\text{Baud Rate (Hz)}}\right)$$

#### **UART Interrupts**

The UART features separate interrupts for the transmitter and the receiver. In addition, when the UART primary functionality is disabled, the Baud Rate Generator can also function as a basic timer with interrupt capability.

Note:

- *This bit only enables the crystal oscillator. Its selection as system clock must be done manually.*

- 0 = Crystal oscillator is enabled during reset, resulting in longer reset timing

- *I* = *Crystal oscillator is disabled during reset, resulting in shorter reset timing*

- *¥* Warning: Programming the XTLDIS bit to zero on 8-pin versions of this device prevents any further communication via the debug pin. This is due to the fact that the XIN and DBG functions are shared on pin 2 of this package. Do not program this bit to zero on 8-pin devices unless no further debugging or Flash programming is required.

## **Trim Bit Address Space**

All available Trim bit addresses and their functions are listed in Table 89 through Table 91.

## Trim Bit Address 0000H—Reserved

| Table 89. | Trim | Options | Bits a | at Address | 0000H |

|-----------|------|---------|--------|------------|-------|

|           |      |         |        |            |       |

| BITS      | 7                                               | 6   | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|

| FIELD     | Reserved                                        |     |     |     |     |     |     |     |

| RESET     | U                                               | U   | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR      | Information Page Memory 0020H                   |     |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |     |     |     |     |     |     |     |

Reserved—Altering this register may result in incorrect device operation.

### Trim Bit Address 0001H—Reserved

#### Table 90. Trim Option Bits at 0001H

| BITS      | 7                                               | 6        | 5   | 4   | 3   | 2   | 1   | 0   |

|-----------|-------------------------------------------------|----------|-----|-----|-----|-----|-----|-----|

| FIELD     |                                                 | Reserved |     |     |     |     |     |     |

| RESET     | U                                               | U        | U   | U   | U   | U   | U   | U   |

| R/W       | R/W                                             | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR      | Information Page Memory 0021H                   |          |     |     |     |     |     |     |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |          |     |     |     |     |     |     |

## OCD Unlock Sequence (8-Pin Devices Only)

Because of pin-sharing on the 8-pin device, an unlock sequence must be performed to access the DBG pin. If this sequence is not completed during a system reset, then the PA0/DBG pin functions only as a GPIO pin.

The following sequence unlocks the DBG pin:

- 1. Hold PA2/RESET Low.

- 2. Wait 5 ms for the internal reset sequence to complete.

- 3. Send the following bytes serially to the debug pin:

```

DBG \leftarrow 80H (autobaud)

DBG \leftarrow EBH

DBG \leftarrow 5AH

DBG \leftarrow 70H

DBG \leftarrow CDH (32-bit unlock key)

```

4. Release PA2/RESET. The PA0/DBG pin is now identical in function to that of the DBG pin on the 20- or 28-pin device. To enter DEBUG mode, re-autobaud and write 80H to the OCD control register (see On-Chip Debugger Commands on page 157).

#### **Breakpoints**

Execution breakpoints are generated using the BRK instruction (opcode 00H). When the eZ8 CPU decodes a BRK instruction, it signals the OCD. If breakpoints are enabled, the OCD enters DEBUG mode and idles the eZ8 CPU. If breakpoints are not enabled, the OCD ignores the BRK signal and the BRK instruction operates as an NOP instruction.

#### **Breakpoints in Flash Memory**

The BRK instruction is opcode 00H, which corresponds to the fully programmed state of a byte in Flash memory. To implement a breakpoint, write 00H to the required break address, overwriting the current instruction. To remove a breakpoint, the corresponding page of Flash memory must be erased and reprogrammed with the original data.

#### **Runtime Counter**

The OCD contains a 16-bit Runtime Counter. It counts system clock cycles between breakpoints. The counter starts counting when the OCD leaves DEBUG mode and stops counting when it enters DEBUG mode again or when it reaches the maximum count of FFFFH.

# **Oscillator Control**

Z8 Encore! XP<sup>®</sup> F0823 Series devices uses three possible clocking schemes, each user-selectable:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, Z8 Encore! XP F0823 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

## Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

### **System Clock Selection**

The oscillator control block selects from the available clocks. Table 101 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                 | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>           | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                   |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 101. Oscillator Configuration and Selection

| Table 1 | 08. Bit | Manipu | lation Ir | nstructions   |

|---------|---------|--------|-----------|---------------|

|         | 00. Dit | manipu |           | 1311 40110113 |

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| TCMX     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 109. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                         |

|----------|----------|---------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment Addresses |

#### Table 110. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | _        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | HALT Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

| Assembly<br>Mnemonic | Symbolic Operation                                           | Addre      | ss Mode     | - Opcode(s)<br>(Hex) | Flags |            |   |             |   | - Fetch | Instr. |   |

|----------------------|--------------------------------------------------------------|------------|-------------|----------------------|-------|------------|---|-------------|---|---------|--------|---|

|                      |                                                              | dst        | src         |                      | С     | z          | S | V           | D | Н       | Cycles |   |

| XOR dst, src         | $dst \gets dst \ XOR \ src$                                  | r          | r           | B2                   | _     | *          | * | 0           | - | _       | 2      | 3 |

|                      |                                                              | r          | lr          | B3                   | _     |            |   |             |   |         | 2      | 4 |

|                      |                                                              | R          | R           | B4                   | _     |            |   |             |   |         | 3      | 3 |

|                      |                                                              | R          | IR          | B5                   | -     |            |   |             |   |         | 3      | 4 |

|                      |                                                              | R          | IM          | B6                   | -     |            |   |             |   |         | 3      | 3 |

|                      |                                                              | IR         | IM          | B7                   | _     |            |   |             |   |         | 3      | 4 |

| XORX dst, src        | $dst \gets dst \ XOR \ src$                                  | ER         | ER          | B8                   | _     | *          | * | 0           | _ | _       | 4      | 3 |

|                      |                                                              | ER         | IM          | B9                   | _     |            |   |             |   |         | 4      | 3 |

| Flags Notation:      | * = Value is a function o<br>– = Unaffected<br>X = Undefined | f the resu | It of the o | peration.            | -     | = R<br>= S |   | t to<br>5 1 | 0 |         |        |   |

#### Table 115. eZ8 CPU Instruction Summary (Continued)

# **On-Chip Peripheral AC and DC Electrical Characteristics**

## Table 122. Power-On Reset and Voltage Brownout Electrical Characteristics and Timing

|                   | Parameter                                                                                                      | T <sub>A</sub> = - | 40 °C to +           | 105 °C       |          | Conditions                                                                                            |  |

|-------------------|----------------------------------------------------------------------------------------------------------------|--------------------|----------------------|--------------|----------|-------------------------------------------------------------------------------------------------------|--|

| Symbol            |                                                                                                                | Minimum            | Typical <sup>1</sup> | Maximum      | Units    |                                                                                                       |  |

| V <sub>POR</sub>  | Power-On Reset<br>Voltage Threshold                                                                            | 2.20               | 2.45                 | 2.70         | V        | V <sub>DD</sub> = V <sub>POR</sub>                                                                    |  |

| V <sub>VBO</sub>  | Voltage Brownout Reset<br>Voltage Threshold                                                                    | 2.15               | 2.40                 | 2.65         | V        | $V_{DD} = V_{VBO}$                                                                                    |  |

|                   | $V_{POR}$ to $V_{VBO}$ hysteresis                                                                              |                    | 50                   | 75           | mV       |                                                                                                       |  |

|                   | Starting V <sub>DD</sub> voltage to<br>ensure valid Power-On<br>Reset.                                         | _                  | V <sub>SS</sub>      | -            | V        |                                                                                                       |  |

| T <sub>ANA</sub>  | Power-On Reset Analog<br>Delay                                                                                 | -                  | 70                   | -            | μs       | V <sub>DD</sub> > V <sub>POR</sub> ; T <sub>POR</sub> Digital<br>Reset delay follows T <sub>ANA</sub> |  |

| T <sub>POR</sub>  | Power-On Reset Digital<br>Delay                                                                                |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles + IPO<br>startup time (T <sub>IPOST</sub> )                |  |

| T <sub>SMR</sub>  | Stop Mode Recovery                                                                                             |                    | 16                   |              | μs       | 66 Internal Precision<br>Oscillator cycles                                                            |  |

| T <sub>VBO</sub>  | Voltage Brownout Pulse<br>Rejection Period                                                                     | _                  | 10                   | _            | μs       | Period of time in which V <sub>DD</sub><br>< V <sub>VBO</sub> without generating<br>a Reset.          |  |

| T <sub>RAMP</sub> | Time for V <sub>DD</sub> to<br>transition from V <sub>SS</sub> to<br>V <sub>POR</sub> to ensure valid<br>Reset | 0.10               | _                    | 100          | ms       |                                                                                                       |  |

| T <sub>SMP</sub>  | Stop Mode Recovery pin pulse rejection period                                                                  |                    | 20                   |              | ns       | For any SMR pin or for the Reset pin when it is asserted in STOP mode.                                |  |

|                   | he typical column is from char are not tested in production.                                                   | acterization       | at 3.3 V and         | 30 °C. These | values a | re provided for design guidance                                                                       |  |

199

|                     |                                                    | T <sub>A</sub> =       | = 3.0 V to<br>0 °C to +<br>otherwise | 70 °C      |                           |                                                                                              |  |

|---------------------|----------------------------------------------------|------------------------|--------------------------------------|------------|---------------------------|----------------------------------------------------------------------------------------------|--|

| Symbol              | Parameter                                          | Minimum Typical Maximu |                                      | Maximum    | Units                     | Conditions                                                                                   |  |

|                     | Resolution                                         | 10                     |                                      | _          | bits                      |                                                                                              |  |

|                     | Differential Nonlinearity<br>(DNL)                 | -1.0                   | -                                    | 1.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |

|                     | Integral Nonlinearity (INL)                        | -3.0                   | _                                    | 3.0        | LSB <sup>3</sup>          | External V <sub>REF</sub> = 2.0 V;<br>R <sub>S</sub> $\leftarrow$ 3.0 k $\Omega$             |  |

|                     | Offset Error with Calibration                      |                        | <u>+</u> 1                           |            | LSB <sup>3</sup>          |                                                                                              |  |

|                     | Absolute Accuracy with Calibration                 |                        | <u>+</u> 3                           |            | LSB <sup>3</sup>          |                                                                                              |  |

| V <sub>REF</sub>    | Internal Reference Voltage                         | 1.0<br>2.0             | 1.1<br>2.2                           | 1.2<br>2.4 | V                         | REFSEL=01<br>REFSEL=10                                                                       |  |

| V <sub>REF</sub>    | Internal Reference<br>Variation with Temperature   |                        | <u>+</u> 1.0                         |            | %                         | Temperature variation<br>with V <sub>DD</sub> = 3.0                                          |  |

| V <sub>REF</sub>    | Internal Reference Voltage Variation with $V_{DD}$ |                        | <u>+</u> 0.5                         |            | %                         | Supply voltage variation<br>with T <sub>A</sub> = 30 °C                                      |  |

| R <sub>REFOUT</sub> | Reference Buffer Output<br>Impedance               |                        | 850                                  |            | Ω                         | When the internal<br>reference is buffered and<br>driven out to the VREF<br>pin (REFOUT = 1) |  |

|                     | Single-Shot Conversion<br>Time                     | _                      | 5129                                 | -          | System<br>clock<br>cycles | All measurements but temperature sensor                                                      |  |

|                     |                                                    |                        | 10258                                |            |                           | Temperature sensor<br>measurement                                                            |  |

|                     | Continuous Conversion<br>Time                      | -                      | 256                                  | -          |                           | All measurements but temperature sensor                                                      |  |

|                     |                                                    |                        | 512                                  |            |                           | Temperature sensor<br>measurement                                                            |  |

|                     | Signal Input Bandwidth                             | -                      | 10                                   |            | kHz                       | As defined by -3 dB point                                                                    |  |

| R <sub>S</sub>      | Analog Source Impedance <sup>4</sup>               | -                      | -                                    | 10         | kΩ                        | In unbuffered mode                                                                           |  |

## Table 125. Analog-to-Digital Converter Electrical Characteristics and Timing

#### 205

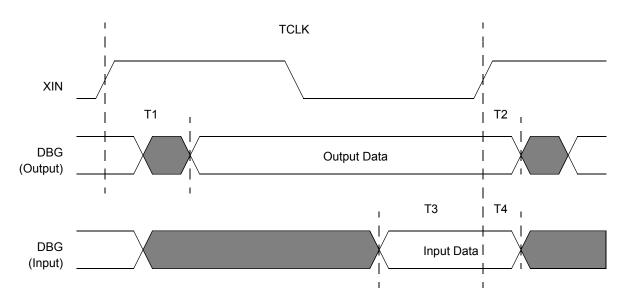

## **On-Chip Debugger Timing**

Figure 31 and Table 129 provide timing information for the DBG pin. The DBG pin timing specifications assume a 4 ns maximum rise and fall time.

|                        |                                  | Dela    | y (ns)  |  |

|------------------------|----------------------------------|---------|---------|--|

| Parameter Abbreviation |                                  | Minimum | Maximum |  |

| DBG                    |                                  |         |         |  |

| T <sub>1</sub>         | XIN Rise to DBG Valid Delay      | _       | 15      |  |

| T <sub>2</sub>         | XIN Rise to DBG Output Hold Time | 2       | _       |  |

| T <sub>3</sub>         | DBG to XIN Rise Input Setup Time | 5       | _       |  |

| T <sub>4</sub>         | DBG to XIN Rise Input Hold Time  | 5       | _       |  |

#### Table 129. On-Chip Debugger Timing

Index

**COMPARE 84** compare - extended addressing 175 COMPARE mode 84 compare with carry 175 compare with carry - extended addressing 175 complement 177 complement carry flag 176 condition code 173 continuous conversion (ADC) 120 CONTINUOUS mode 84 control register definition, UART 104 Control Registers 13, 17 **COUNTER modes 84** CP 175 **CPC 175 CPCX 175** CPU and peripheral overview 4 CPU control instructions 176 **CPX 175** Customer Support 237

# D

DA 173, 175 data memory 15 DC characteristics 194 debugger, on-chip 151 **DEC 175** decimal adjust 175 decrement 175 decrement and jump non-zero 178 decrement word 175 **DECW 175** destination operand 174 device, port availability 35 DI 176 direct address 173 disable interrupts 176 **DJNZ 178** dst 174

## Ε

EI 176

electrical characteristics 193 ADC 201 flash memory and timing 200 GPIO input data sample timing 202 Watchdog Timer 200, 202 enable interrupt 176 ER 173 extended addressing register 173 external pin reset 25 eZ8 CPU features 4 eZ8 CPU instruction classes 174 eZ8 CPU instruction notation 172 eZ8 CPU instruction set 171 eZ8 CPU instruction set 171

## F

FCTL register 137, 143, 144 features, Z8 Encore! 1 first opcode map 190 FLAGS 174 flags register 174 flash controller 4 option bit address space 144 option bit configuration - reset 141 program memory address 0000H 144 program memory address 0001H 145 flash memory 129 arrangement 130 byte programming 135 code protection 133 configurations 129 control register definitions 137, 143 controller bypass 136 electrical characteristics and timing 200 flash control register 137, 143, 144 flash option bits 134 flash status register 137 flow chart 132 frequency high and low byte registers 139 mass erase 135 operation 131 operation timing 133

228

Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

timing 205 OCD commands execute instruction (12H) 161 read data memory (0DH) 160 read OCD control register (05H) 158 read OCD revision (00H) 158 read OCD status register (02H) 158 read program counter (07H) 159 read program memory (0BH) 160 read program memory CRC (0EH) 161 read register (09H) 159 read runtime counter (03H) 158 step instruction (10H) 161 stuff instruction (11H) 161 write data memory (0CH) 160 write OCD control register (04H) 158 write program counter (06H) 159 write program memory (0AH) 159 write register (08H) 159 on-chip debugger (OCD) 151 on-chip debugger signals 10 ONE-SHOT mode 84 opcode map abbreviations 189 cell description 188 first 190 second after 1FH 191 Operational Description 21, 31, 35, 53, 67, 87, 93, 113, 117, 127, 129, 141, 151, 165, 169 OR 177 ordering information 217 **ORX 178**

status register 163

## Ρ

p 173 packaging 20-pin PDIP 211, 212 20-pin SSOP 212, 215 28-pin PDIP 213 28-pin SOIC 214 8-pin PDIP 209 8-pin SOIC 210

PDIP 214, 215 part selection guide 2 PC 174 PDIP 214, 215 peripheral AC and DC electrical characteristics 199 pin characteristics 10 Pin Descriptions 7 polarity 173 POP 177 pop using extended addressing 177 **POPX 177** port availability, device 35 port input timing (GPIO) 203 port output timing, GPIO 204 power supply signals 10 power-down, automatic (ADC) 118 Power-on and Voltage Brownout electrical characteristics and timing 199 Power-On Reset (POR) 23 program control instructions 178 program counter 174 program memory 13 **PUSH 177** push using extended addressing 177 PUSHX 177 PWM mode 84, 85 PxADDR register 44

## R

PxCTL register 45

R 173 r 173 RA register address 173 RCF 176 receive IrDA data 115 receiving UART data-interrupt-driven method 98 receiving UART data-polled method 97 register 173 ADC control (ADCCTL) 122, 124 232