## Zilog - Z8F0813SH005EC Datasheet

Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Discontinued at Digi-Key                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 16                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 20-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sh005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| On-Chip Debugger Initiated Reset                    | 26 |

|-----------------------------------------------------|----|

| Stop Mode Recovery                                  |    |

| Stop Mode Recovery Using Watchdog Timer Time-Out    |    |

| Stop Mode Recovery Using a GPIO Port Pin Transition |    |

| Stop Mode Recovery Using the External RESET Pin     |    |

| Reset Register Definitions                          |    |

| Low-Power Modes                                     |    |

| STOP Mode                                           |    |

| HALT Mode                                           |    |

| Peripheral-Level Power Control                      | 32 |

| Power Control Register Definitions                  | 32 |

| General-Purpose Input/Output                        | 35 |

| GPIO Port Availability By Device                    | 35 |

| Architecture                                        | 36 |

| GPIO Alternate Functions                            | 36 |

| Direct LED Drive                                    | 37 |

| Shared Reset Pin                                    | 37 |

| Shared Debug Pin                                    | 37 |

| Crystal Oscillator Override                         | 38 |

| 5 V Tolerance                                       |    |

| External Clock Setup                                |    |

| GPIO Interrupts                                     |    |

| GPIO Control Register Definitions                   |    |

| Port A–C Address Registers                          |    |

| Port A–C Control Registers                          |    |

| Port A–C Data Direction Sub-Registers               | 45 |

| Port A–C Alternate Function Sub-Registers           |    |

| Port A–C Input Data Registers                       |    |

| Port A–C Output Data Register                       |    |

|                                                     |    |

| LED Drive Level High Register                       |    |

|                                                     |    |

| Interrupt Controller                                |    |

| Interrupt Vector Listing                            |    |

| Architecture                                        |    |

| Operation                                           |    |

| IVIASIEI IIIIEIIUPI LIIAVIE                         | 00 |

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

tions as a GPIO pin. If it is not present, the debug feature is disabled until/unless another reset event occurs. For more details, see On-Chip Debugger on page 151.

# **Crystal Oscillator Override**

For systems using a crystal oscillator, PA0 and PA1 are used to connect the crystal. When the crystal oscillator is enabled (see Oscillator Control Register Definitions on page 167), the GPIO settings are overridden and PA0 and PA1 are disabled.

# **5 V Tolerance**

All six I/O pins on the 8-pin devices are 5 V-tolerant, unless the programmable pull-ups are enabled. If the pull-ups are enabled and inputs higher than  $V_{DD}$  are applied to these parts, excessive current flows through those pull-up devices and can damage the chip.

**Note:** In the 20- and 28-pin versions of this device, any pin which shares functionality with an ADC, crystal or comparator port is not 5 V-tolerant, including PA[1:0], PB[5:0], and PC[2:0]. All other signal pins are 5 V-tolerant, and can safely handle inputs higher than  $V_{DD}$  even with the pull-ups enabled.

# **External Clock Setup**

For systems using an external TTL drive, PB3 is the clock source for 20- and 28-pin devices. In this case, configure PB3 for alternate function CLKIN. Write the Oscillator Control Register (see Oscillator Control Register Definitions on page 167) such that the external oscillator is selected as the system clock. For 8-pin devices use PA1 instead of PB3.

| Port   | Pin | Mnemonic                                                   | Alternate Function<br>Set Register AFS1                |            |

|--------|-----|------------------------------------------------------------|--------------------------------------------------------|------------|

| Port C | PC0 | Reserved                                                   |                                                        | AFS1[0]: 0 |

|        |     | ANA4/CINP/LED<br>Drive                                     | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1 |

|        | PC1 | Reserved                                                   |                                                        | AFS1[1]: 0 |

|        |     | ANA5/CINN/ LED ADC or Comparator Input, or LED drive Drive |                                                        | AFS1[1]: 1 |

|        | PC2 | Reserved                                                   |                                                        | AFS1[2]: 0 |

|        |     | ANA6/LED/<br>VREF*                                         | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1 |

|        | PC3 | COUT                                                       | Comparator Output                                      | AFS1[3]: 0 |

|        |     | LED                                                        | LED drive                                              | AFS1[3]: 1 |

|        | PC4 | Reserved                                                   |                                                        | AFS1[4]: 0 |

|        |     | LED                                                        | LED Drive                                              | AFS1[4]: 1 |

|        | PC5 | Reserved                                                   |                                                        | AFS1[5]: 0 |

|        |     | LED                                                        | LED Drive                                              | AFS1[5]: 1 |

|        | PC6 | Reserved                                                   |                                                        | AFS1[6]: 0 |

|        |     | LED                                                        | LED Drive                                              | AFS1[6]: 1 |

|        | PC7 | Reserved                                                   |                                                        | AFS1[7]: 0 |

|        |     | LED                                                        | LED Drive                                              | AFS1[7]: 1 |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

**Note:** Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in Port A–C Alternate Function Sub-Registers must also be enabled. \*VREF is available on PC2 in 20-pin parts only.

| Priority | Program<br>Memory<br>Vector Address | Interrupt or Trap Source       |

|----------|-------------------------------------|--------------------------------|

| Lowest   | 0036H                               | Port C Pin 0, both input edges |

|          | 0038H                               | Reserved                       |

#### Table 33. Trap and Interrupt Vectors in Order of Priority (Continued)

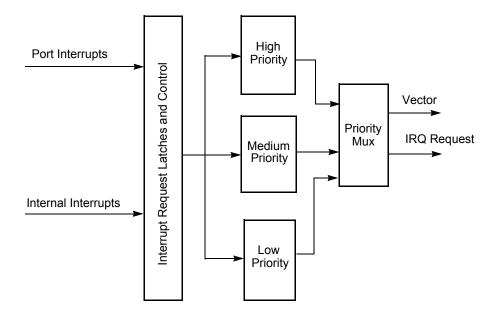

# Architecture

Figure 8 displays the interrupt controller block diagram.

Figure 8. Interrupt Controller Block Diagram

# Operation

## **Master Interrupt Enable**

The master interrupt enable bit (IRQE) in the Interrupt Control register globally enables and disables interrupts.

Interrupts are globally enabled by any of the following actions:

- Execution of an Enable Interrupt (EI) instruction

- Execution of an Return from Interrupt (IRET) instruction

| BITS  | 7    | 6    | 5    | 4    | 3    | 2    | 1    | 0    |

|-------|------|------|------|------|------|------|------|------|

| FIELD | IES7 | IES6 | IES5 | IES4 | IES3 | IES2 | IES1 | IES0 |

| RESET | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |

| ADDR  |      |      |      | FC   | DH   |      |      |      |

#### Table 46. Interrupt Edge Select Register (IRQES)

IES*x*—Interrupt Edge Select *x*

0 = An interrupt request is generated on the falling edge of the PAx input or PDx

1 = An interrupt request is generated on the rising edge of the PAx input PDx where x indicates the specific GPIO port pin number (0 through 7)

## **Shared Interrupt Select Register**

The Shared Interrupt Select (IRQSS) register (Table 47) determines the source of the PADxS interrupts. The Shared Interrupt Select register selects between Port A and alternate sources for the individual interrupts.

Because these shared interrupts are edge-triggered, it is possible to generate an interrupt just by switching from one shared source to another. For this reason, an interrupt must be disabled before switching between sources.

Table 47. Shared Interrupt Select Register (IRQSS)

| BITS  | 7        | 6     | 5        | 4   | 3   | 2   | 1   | 0   |

|-------|----------|-------|----------|-----|-----|-----|-----|-----|

| FIELD | Reserved | PA6CS | Reserved |     |     |     |     |     |

| RESET | 0        | 0     | 0        | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W      | R/W   | R/W      | R/W | R/W | R/W | R/W | R/W |

| ADDR  |          |       |          | FC  | EH  |     |     |     |

PA6CS—PA6/Comparator Selection

0 = PA6 is used for the interrupt for PA6CS interrupt request

1 = The Comparator is used for the interrupt for PA6CS interrupt request

Reserved-Must be 0

## **Interrupt Control Register**

The Interrupt Control (IRQCTL) register (Table 48) contains the master enable bit for all interrupts.

| BITS  | 7    | 6   | 5   | 4     | 3    | 2   | 1   | 0   |  |

|-------|------|-----|-----|-------|------|-----|-----|-----|--|

| FIELD | PWML |     |     |       |      |     |     |     |  |

| RESET | 0    | 0   | 0   | 0     | 0    | 0   | 0   | 0   |  |

| R/W   | R/W  | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |  |

| ADDR  |      |     |     | F05H, | F0DH |     |     |     |  |

#### Table 54. Timer 0–1 PWM Low Byte Register (TxPWML)

PWMH and PWML—Pulse-Width Modulator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, form a 16-bit value that is compared to the current 16-bit timer count. When a match occurs, the PWM output changes state. The PWM output value is set by the TPOL bit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers also store the 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

## **Timer 0–1 Control Registers**

#### Time 0–1 Control Register 0

The Timer Control Register 0 (TxCTL0) and Timer Control Register 1 (TxCTL1) determine the timer operating mode. It also includes a programmable PWM deadband delay, two bits to configure timer interrupt definition, and a status bit to identify if the most recent timer interrupt is caused by an input Capture event.

Table 55. Timer 0–1 Control Register 0 (TxCTL0)

| BITS  | 7                                 | 6   | 5   | 4      | 3    | 2   | 1   | 0   |

|-------|-----------------------------------|-----|-----|--------|------|-----|-----|-----|

| FIELD | LD TMODEHI TICONFIG Reserved PWMD |     |     | INPCAP |      |     |     |     |

| RESET | 0                                 | 0   | 0   | 0      | 0    | 0   | 0   | 0   |

| R/W   | R/W                               | R/W | R/W | R/W    | R/W  | R/W | R/W | R/W |

| ADDR  |                                   |     |     | F06H,  | F0EH |     |     |     |

#### TMODEHI—Timer Mode High Bit

This bit along with the TMODE field in TxCTL1 register determines the operating mode of the timer. This is the most-significant bit of the Timer mode selection value. See the TxCTL1 register description for more details.

TICONFIG—Timer Interrupt Configuration

This field configures timer interrupt definition.

## Watchdog Timer Refresh

When first enabled, the WDT is loaded with the value in the Watchdog Timer Reload registers. The Watchdog Timer counts down to 000000H unless a WDT instruction is executed by the eZ8 CPU. Execution of the WDT instruction causes the down counter to be reloaded with the WDT Reload value stored in the Watchdog Timer Reload registers. Counting resumes following the reload operation.

When Z8 Encore! XP<sup>®</sup> F0823 Series devices are operating in DEBUG Mode (using the OCD), the Watchdog Timer is continuously refreshed to prevent any Watchdog Timer time-outs.

## Watchdog Timer Time-Out Response

The Watchdog Timer times out when the counter reaches 000000H. A time-out of the Watchdog Timer generates either an interrupt or a system reset. The WDT\_RES Flash Option Bit determines the time-out response of the Watchdog Timer. For information on programming of the WDT\_RES Flash Option Bit, see Flash Option Bits on page 141.

#### WDT Interrupt in Normal Operation

If configured to generate an interrupt when a time-out occurs, the Watchdog Timer issues an interrupt request to the interrupt controller and sets the WDT status bit in the Watchdog Timer Control register. If interrupts are enabled, the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address. After time-out and interrupt generation, the Watchdog Timer counter rolls over to its maximum value of FFFFFH and continues counting. The Watchdog Timer counter is not automatically returned to its Reload Value.

The Reset Status Register (see Reset Status Register on page 28) must be read before clearing the WDT interrupt. This read clears the WDT time-out Flag and prevents further WDT interrupts for immediately occurring.

#### WDT Interrupt in STOP Mode

If configured to generate an interrupt when a time-out occurs and Z8 Encore! XP F0823 Series are in STOP mode, the Watchdog Timer automatically initiates a Stop Mode Recovery and generates an interrupt request. Both the WDT status bit and the STOP bit in the Watchdog Timer Control register are set to 1 following a WDT time-out in STOP mode. For more information on Stop Mode Recovery, see Reset and Stop Mode Recovery on page 21.

If interrupts are enabled, following completion of the Stop Mode Recovery the eZ8 CPU responds to the interrupt request by fetching the Watchdog Timer interrupt vector and executing code from the vector address.

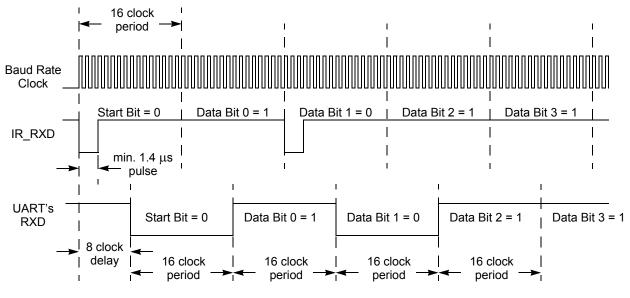

## **Receiving IrDA Data**

Data received from the infrared transceiver using the IR\_RXD signal through the RXD pin is decoded by the Infrared Endec and passed to the UART. The UART's baud rate clock is used by the Infrared Endec to generate the demodulated signal (RXD) that drives the UART. Each UART/Infrared data bit is 16-clocks wide. Figure 18 displays data reception. When the Infrared Endec is enabled, the UART's RXD signal is internal to the Z8 Encore! XP<sup>®</sup> F0823 Series products while the IR\_RXD signal is received through the RXD pin.

Figure 18. IrDA Data Reception

#### **Infrared Data Reception**

**Caution:** The system clock frequency must be at least 1.0 MHz to ensure proper reception of the 1.4 μs minimum width pulses allowed by the IrDA standard.

#### **Endec Receiver Synchronization**

The IrDA receiver uses a local baud rate clock counter (0 to 15 clock periods) to generate an input stream for the UART and to create a sampling window for detection of incoming pulses. The generated UART input (UART RXD) is delayed by 8 baud rate clock periods with respect to the incoming IrDA data stream. When a falling edge in the input data stream is detected, the Endec counter is reset. When the count reaches a value of 8, the UART RXD value is updated to reflect the value of the decoded data. When the count reaches 12 baud clock periods, the sampling window for the next incoming pulse opens. The window remains open until the count again reaches 8 (that is, 24 baud clock periods since the previous pulse was detected), giving the Endec a sampling window of minus four

## 118

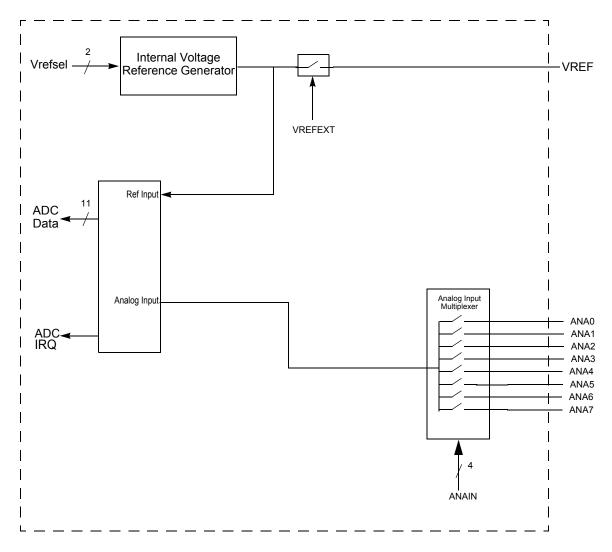

Figure 19. Analog-to-Digital Converter Block Diagram

# Operation

## **Data Format**

The output of the ADC is an 11-bit, signed, two's complement digital value. The output generally ranges from 0 to +1023, but offset errors can cause small negative values.

The ADC registers return 13 bits of data, but the two LSBs are intended for compensation use only. When the compensation routine is performed on the 13 bit raw ADC value, two

## **Software Compensation Procedure**

The value read from the ADC high and low byte registers are uncompensated. The user mode software must apply gain and offset correction to this uncompensated value for maximum accuracy. The following formula yields the compensated value:

$ADC_{comp} = (ADC_{uncomp} - OFFCAL) + ((ADC_{uncomp} - OFFCAL) * GAINCAL)/2^{16}$

where GAINCAL is the gain calibration byte, OFFCAL is the offset calibration byte and  $ADC_{uncomp}$  is the uncompensated value read from the ADC. The OFFCAL value is in two's complement format, as are the compensated and uncompensated ADC values.

- **Note:** The offset compensation is performed first, followed by the gain compensation. One bit of resolution is lost because of rounding on both the offset and gain computations. As a result the ADC registers read back 13 bits: 1 sign bit, two calibration bits lost to rounding and 10 data bits. Also note that in the second term, the multiplication must be performed before the division by 2<sup>16</sup>. Otherwise, the second term evaluates to zero incorrectly.

- **Caution:** Although the ADC can be used without the gain and offset compensation, it does exhibit non-unity gain. Designing the ADC with sub-unity gain reduces noise across the ADC range but requires the ADC results to be scaled by a factor of 8/7.

# **ADC Control Register Definitions**

The following sections define the ADC control registers.

## **ADC Control Register 0**

The ADC Control register selects the analog input channel and initiates the analog-to-digital conversion.

| BITS  | 7   | 6       | 5      | 4    | 3           | 2 | 1 | 0 |

|-------|-----|---------|--------|------|-------------|---|---|---|

| FIELD | CEN | REFSELL | REFEXT | CONT | ANAIN[3:0]  |   |   |   |

| RESET | 0   | 0       | 0      | 0    | 0           | 0 | 0 | 0 |

| R/W   | R/W | R/W     | R/W    | R/W  | R/W R/W R/W |   |   |   |

| ADDR  |     |         |        | F7   | ОН          |   |   |   |

Table 72. ADC Control Register 0 (ADCCTL0)

CEN—Conversion Enable

0 = Conversion is complete. Writing a 0 produces no effect. The ADC automatically clears this bit to 0 when a conversion is complete.

1 = Begin conversion. Writing a 1 to this bit starts a conversion. If a conversion is already in progress, the conversion restarts. This bit remains 1 until the conversion is complete.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01 = Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP<sup>®</sup> F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

132

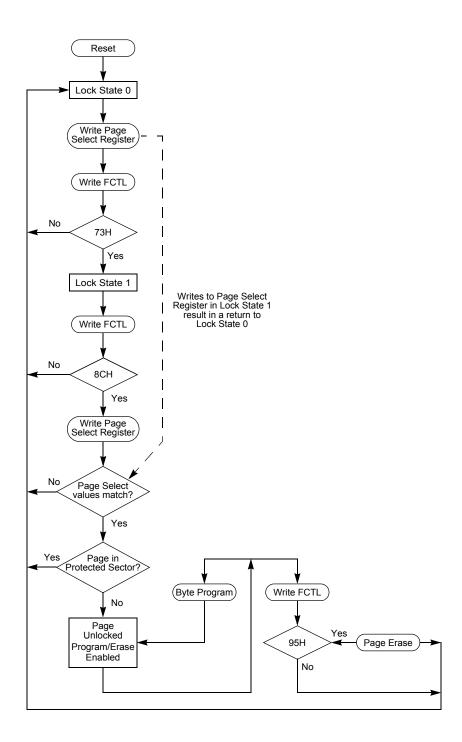

Figure 21. Flash Controller Operation Flowchart

Watchdog Timer can only be disabled by a Reset or Stop Mode Recovery. This setting is the default for unprogrammed (erased) Flash.

Reserved—R/W bits must be 1 during writes; 1 when read.

VBO AO-Voltage Brownout Protection Always ON

0 = Voltage Brownout Protection can be disabled in STOP mode to reduce total power consumption. For the block to be disabled, the power control register bit must also be written (see Power Control Register 0 on page 32).

1 = Voltage Brownout Protection is always enabled including during STOP mode. This setting is the default for unprogrammed (erased) Flash.

FRP—Flash Read Protect

0 = User program code is inaccessible. Limited control features are available through the On-Chip Debugger.

1 = User program code is accessible. All On-Chip Debugger commands are enabled. This setting is the default for unprogrammed (erased) Flash.

Reserved-Must be 1

FWP—Flash Write Protect

This Option Bit provides Flash Program Memory protection:

0 = Programming and erasure disabled for all of Flash Program Memory. Programming, Page Erase, and Mass Erase through User Code is disabled. Mass Erase is available using the On-Chip Debugger.

1 = Programming, Page Erase, and Mass Erase are enabled for all of Flash program memory.

## Flash Program Memory Address 0001H

#### Table 88. Flash Options Bits at Program Memory Address 0001H

| BITS       | 7                    | 6           | 5            | 4        | 3        | 2   | 1 | 0 |  |  |

|------------|----------------------|-------------|--------------|----------|----------|-----|---|---|--|--|

| FIELD      | Reserved             |             |              | XTLDIS   | Reserved |     |   |   |  |  |

| RESET      | U                    | U           | U            | U        | U        | U   | U | U |  |  |

| R/W        | R/W                  | R/W         | R/W          | R/W      | R/W      | R/W |   |   |  |  |

| ADDR       | Program Memory 0001H |             |              |          |          |     |   |   |  |  |

| Note:    = | Inchanged b          | V Reset R/M | = Read/Write | <b>`</b> |          |     |   |   |  |  |

**Note:** U = Unchanged by Reset. R/W = Read/Write.

Reserved—R/W must be 1 during writes; 1 when read

XTLDIS—State of Crystal Oscillator at Reset

# **On-Chip Debugger Commands**

The host communicates to the OCD by sending OCD commands using the DBG interface. During normal operation, only a subset of the OCD commands are available. In DEBUG mode, all OCD commands become available unless the user code and control registers are protected by programming the Flash Read Protect Option bit (FRP). The Flash Read Protect Option bit prevents the code in memory from being read out of Z8 Encore! XP<sup>®</sup> F0823 Series products. When this option is enabled, several of the OCD commands are disabled. Table 99 on page 162 is a summary of the OCD commands. Each OCD command is described in further detail in the bulleted list following this table. Table 99 on page 162 also indicates those commands that operate when the device is not in DEBUG mode (normal operation) and those commands that are disabled by programming the Flash Read Protect Option bit.

| Debug Command              | Command<br>Byte | Enabled when<br>NOT in DEBUG<br>mode? | Disabled by Flash Read Protect<br>Option Bit                                                                                                                              |

|----------------------------|-----------------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Read OCD Revision          | 00H             | Yes                                   | -                                                                                                                                                                         |

| Reserved                   | 01H             | _                                     | _                                                                                                                                                                         |

| Read OCD Status Register   | 02H             | Yes                                   | -                                                                                                                                                                         |

| Read Runtime Counter       | 03H             | _                                     | -                                                                                                                                                                         |

| Write OCD Control Register | 04H             | Yes                                   | Cannot clear DBGMODE bit.                                                                                                                                                 |

| Read OCD Control Register  | 05H             | Yes                                   | -                                                                                                                                                                         |

| Write Program Counter      | 06H             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Counter       | 07H             | _                                     | Disabled.                                                                                                                                                                 |

| Write Register             | 08H             | _                                     | Only writes of the Flash Memory Control<br>registers are allowed. Additionally, only<br>the Mass Erase command is allowed to<br>be written to the Flash Control register. |

| Read Register              | 09H             | -                                     | Disabled.                                                                                                                                                                 |

| Write Program Memory       | 0AH             | _                                     | Disabled.                                                                                                                                                                 |

| Read Program Memory        | 0BH             | _                                     | Disabled.                                                                                                                                                                 |

| Write Data Memory          | 0CH             | _                                     | Yes.                                                                                                                                                                      |

| Read Data Memory           | 0DH             | -                                     | -                                                                                                                                                                         |

| Read Program Memory CRC    | 0EH             | -                                     | -                                                                                                                                                                         |

| Reserved                   | 0FH             | -                                     | -                                                                                                                                                                         |

| Step Instruction           | 10H             | _                                     | Disabled.                                                                                                                                                                 |

| Assembly<br>Mnemonic |                                                                  | Addre   | ss Mode     | - Opcode(s) | Fla | gs |              |   | - Fetch | Instr. |   |        |

|----------------------|------------------------------------------------------------------|---------|-------------|-------------|-----|----|--------------|---|---------|--------|---|--------|

|                      | Symbolic Operation                                               | dst     | src         | (Hex)       | С   | Ζ  | S            | v | D       | Н      |   | Cycles |

| RR dst               |                                                                  | R       |             | E0          | *   | *  | *            | * | _       | -      | 2 | 2      |

|                      | ► D7 D6 D5 D4 D3 D2 D1 D0 ► C                                    | IR      |             | E1          | _   |    |              |   |         |        | 2 | 3      |

| RRC dst              |                                                                  | R       |             | C0          | *   | *  | *            | * | _       | -      | 2 | 2      |

|                      | ► <u>D7D6D5D4D3D2D1D0</u> ► C<br>dst                             | IR      |             | C1          | _   |    |              |   |         |        | 2 | 3      |

| SBC dst, src         | $dst \gets dst - src - C$                                        | r       | r           | 32          | *   | *  | *            | * | 1       | *      | 2 | 3      |

|                      |                                                                  | r       | lr          | 33          | _   |    |              |   |         |        | 2 | 4      |

|                      |                                                                  | R       | R           | 34          | _   |    |              |   |         |        | 3 | 3      |

|                      |                                                                  | R       | IR          | 35          | _   |    |              |   |         |        | 3 | 4      |

|                      |                                                                  | R       | IM          | 36          | _   |    |              |   |         |        | 3 | 3      |

|                      |                                                                  | IR      | IM          | 37          | _   |    |              |   |         |        | 3 | 4      |

| SBCX dst, src        | $dst \gets dst - src - C$                                        | ER      | ER          | 38          | *   | *  | *            | * | 1       | *      | 4 | 3      |

|                      |                                                                  | ER      | IM          | 39          | _   |    |              |   |         |        | 4 | 3      |

| SCF                  | C ← 1                                                            |         |             | DF          | 1   | -  | _            | _ | _       | -      | 1 | 2      |

| SRA dst              | <b>*</b> *                                                       | R       |             | D0          | *   | *  | *            | 0 | _       | -      | 2 | 2      |

|                      | D7D6D5D4D3D2D1D0 ► C<br>dst                                      | IR      |             | D1          |     |    |              |   |         |        | 2 | 3      |

| SRL dst              | 0 - D7 D6 D5 D4 D3 D2 D1 D0 - C                                  | R       |             | 1F C0       | *   | *  | 0            | * | _       | -      | 3 | 2      |

|                      | dst                                                              | IR      |             | 1F C1       |     |    |              |   |         |        | 3 | 3      |

| SRP src              | $RP \leftarrow src$                                              |         | IM          | 01          | -   | _  | _            | _ | _       | -      | 2 | 2      |

| STOP                 | STOP Mode                                                        |         |             | 6F          | _   | _  | _            | _ | _       | _      | 1 | 2      |

| SUB dst, src         | $dst \gets dst - src$                                            | r       | r           | 22          | *   | *  | *            | * | 1       | *      | 2 | 3      |

|                      |                                                                  | r       | lr          | 23          | -   |    |              |   |         |        | 2 | 4      |

|                      |                                                                  | R       | R           | 24          | -   |    |              |   |         |        | 3 | 3      |

|                      |                                                                  | R       | IR          | 25          | _   |    |              |   |         |        | 3 | 4      |

|                      |                                                                  | R       | IM          | 26          | -   |    |              |   |         |        | 3 | 3      |

|                      |                                                                  | IR      | IM          | 27          | -   |    |              |   |         |        | 3 | 4      |

| Flags Notation:      | * = Value is a function of th<br>– = Unaffected<br>X = Undefined | ne resu | It of the o | peration.   |     |    | ese<br>et to |   | 0       |        |   |        |

## Table 115. eZ8 CPU Instruction Summary (Continued)

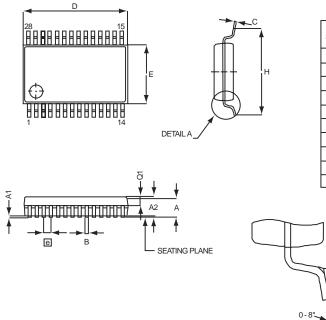

# Figure 42 displays the 28-pin Small Shrink Outline Package (SSOP) available for Z8 Encore! XP F0823 Series devices.

|        |         | MILLIMETER | 2     | INCH       |       |       |  |  |  |

|--------|---------|------------|-------|------------|-------|-------|--|--|--|

| SYMBOL | MIN NOM |            | MAX   | MIN        | NOM   | MAX   |  |  |  |

| А      | 1.73    | 1.86       | 1.99  | 0.068      | 0.073 | 0.078 |  |  |  |

| A1     | 0.05    | 0.13       | 0.21  | 0.002      | 0.005 | 0.008 |  |  |  |

| A2     | 1.68    | 1.73       | 1.78  | 0.066      | 0.068 | 0.070 |  |  |  |

| В      | 0.25    |            | 0.38  | 0.010      |       | 0.015 |  |  |  |

| С      | 0.09    | -          | 0.20  | 0.004      | 0.006 | 0.008 |  |  |  |

| D      | 10.07   | 10.20      | 10.33 | 0.397      | 0.402 | 0.407 |  |  |  |

| E      | 5.20    | 5.30       | 5.38  | 0.205      | 0.209 | 0.212 |  |  |  |

| е      |         | 0.65 TYP   |       | 0.0256 TYP |       |       |  |  |  |

| н      | 7.65    | 7.80       | 7.90  | 0.301      | 0.307 | 0.311 |  |  |  |

| L      | 0.63    | 0.75       | 0.95  | 0.025      | 0.030 | 0.037 |  |  |  |

CONTROLLING DIMENSIONS: MM LEADS ARE COPLANAR WITHIN .004 INCHES.

Figure 42. 28-Pin Small Shrink Outline Package (SSOP)

| Jaquing<br>Trad<br>Z8 Encore! XP <sup>®</sup> F0823 S                       | Flash                                                                       | M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M<br>M | I/O Lines | ∓<br>Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description |

|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-----------|-----------------|------------------------|---------------------|----------------|-------------|

| Z8F08A28100KITG Z8 Encore! XP F082A Series Development Kit (20- and 28-Pin) |                                                                             |                                                                                             |           |                 |                        |                     |                |             |

| Z8F04A28100KITG                                                             | Z8F04A28100KITG Z8 Encore! XP F042A Series Development Kit (20- and 28-Pin) |                                                                                             |           |                 |                        |                     |                |             |

| Z8F04A08100KITG Z8 Encore! XP F042A Series Development Kit (8-Pin)          |                                                                             |                                                                                             |           |                 |                        |                     |                |             |

| ZUSBSC00100ZACG USB Smart Cable Accessory Kit                               |                                                                             |                                                                                             |           |                 |                        |                     |                |             |

| ZUSBOPTSC01ZACG                                                             | ZUSBOPTSC01ZACG Opto-Isolated USB Smart Cable Accessory Kit                 |                                                                                             |           |                 |                        |                     |                |             |

| ZENETSC0100ZACG Ethernet Smart Cable Accessory Kit                          |                                                                             |                                                                                             |           |                 |                        |                     |                |             |

# Т

**TCM 176 TCMX 176** test complement under mask 176 test complement under mask - extended addressing 176 test under mask 176 test under mask - extended addressing 176 timer signals 9 timers 67 architecture 67 block diagram 67 CAPTURE mode 74, 75, 84, 85 CAPTURE/COMPARE mode 78, 85 COMPARE mode 76, 84 CONTINUOUS mode 69, 84 COUNTER mode 70, 71 COUNTER modes 84 GATED mode 77, 84 ONE-SHOT mode 68, 84 operating mode 68 PWM mode 72, 73, 84, 85 reading the timer count values 79 reload high and low byte registers 80 timer control register definitions 80 timer output signal operation 79 timers 0-3 control registers 82, 83 high and low byte registers 80, 81 TM 176 TMX 176 tools, hardware and software 226 transmit IrDA data 114 transmitting UART data-polled method 95 transmitting UART dat-interrupt-driven method 96 **TRAP 178**

## U

UART 4 architecture 93 baud rate generator 103

control register definitions 104 controller signals 9 data format 94 interrupts 101 MULTIPROCESSOR mode 99 receiving data using interrupt-driven method 98 receiving data using the polled method 97 transmitting data using the interrupt-driven method 96 transmitting data using the polled method 95 x baud rate high and low registers 110 x control 0 and control 1 registers 107 x status 0 and status 1 registers 105, 106 UxBRH register 110 UxBRL register 110 UxCTL0 register 107, 110 UxCTL1 register 108 UxRXD register 105 UxSTAT0 register 105 UxSTAT1 register 106 UxTXD register 104

# V

vector 173 Voltage Brownout reset (VBR) 24

## W

Watchdog Timer approximate time-out delay 87 CNTL 24 control register 89, 127, 167 electrical characteristics and timing 200, 202 interrupt in normal operation 88 interrupt in STOP mode 88 refresh 88, 177 reload unlock sequence 89 reload upper, high and low registers 90 reset 25 reset in normal operation 89