Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                  |

|----------------------------|-----------------------------------------------------------|

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 24                                                        |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | -                                                         |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | 0°C ~ 70°C (TA)                                           |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 28-SOIC (0.295", 7.50mm Width)                            |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0813sj005sc |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Ordering Information            | 217 |

|---------------------------------|-----|

| Part Number Suffix Designations | 226 |

| Index                           | 227 |

| Customer Support                | 237 |

# **Reset Controller**

Z8 Encore!  $XP^{\mathbb{R}}$  F0823 Series products can be reset using the  $\overline{RESET}$  pin, POR, WDT time-out, STOP mode exit, or Voltage Brownout warning signal. The  $\overline{RESET}$  pin is bidirectional, that is, it functions as reset source as well as a reset indicator.

# **On-Chip Debugger**

Z8 Encore! XP F0823 Series products feature an integrated On-Chip Debugger. The OCD provides a rich-set of debugging capabilities, such as reading and writing registers, programming Flash memory, setting breakpoints and executing code. A single-pin interface provides communication to the OCD. Table 5 provides detailed information about the characteristics for each pin available on Z8 Encore!  $XP^{\text{(R)}}$  F0823 Series 8-pin devices.

**Note:** All six I/O pins on the 8-pin packages are 5 V-tolerant (unless the pull-up devices are enabled). The column in Table 4 below describes 5 V-tolerance for the 20- and 28-pin packages only.

|                    |           |                               | Active<br>Low or          |                    |                                  | Schmitt-         |                        |                  |

|--------------------|-----------|-------------------------------|---------------------------|--------------------|----------------------------------|------------------|------------------------|------------------|

| Symbol<br>Mnemonic | Direction | Reset<br>Direction            | Active<br>High            | Tristate<br>Output | Internal Pull-up<br>or Pull-down | Trigger<br>Input | Open Drain<br>Output   | 5 V<br>Tolerance |

| AVDD               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | N/A              |

| AVSS               | N/A       | N/A                           | N/A                       | N/A                | N/A                              | N/A              | N/A                    | NA               |

| DBG                | I/O       | I                             | N/A                       | Yes                | No                               | Yes              | Yes                    | Yes              |

| PA[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PA[7:2]<br>only  |

| PB[7:0]            | I/O       | Ι                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PB[7:6]<br>only  |

| PC[7:0]            | I/O       | I                             | N/A                       | Yes                | Programmable<br>Pull-up          | Yes              | Yes,<br>Programmable   | PC[7:3]<br>only  |

| RESET              | I/O       | I/O<br>(defaults<br>to RESET) | Low (in<br>Reset<br>mode) | Yes (PD0<br>only)  | Alw <u>ays on</u> for<br>RESET   | Yes              | Always on for<br>RESET | Yes              |

| VDD                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

| VSS                | N/A       | N/A                           | N/A                       | N/A                |                                  |                  | N/A                    | N/A              |

#### Table 4. Pin Characteristics (20- and 28-pin Devices)

**Note:** *PB6 and PB7 are available only in the devices without ADC.*

# Stop Mode Recovery Using the External RESET Pin

When the Z8 Encore! XP F0823 Series device is in STOP mode and the external  $\overline{\text{RESET}}$  pin is driven Low, a system reset occurs. Because of a glitch filter operating on the  $\overline{\text{RESET}}$  pin, the Low pulse must be greater than the minimum width specified, or it is ignored. For more details, see Electrical Characteristics on page 193.

# **Reset Register Definitions**

#### **Reset Status Register**

The Reset Status (RSTSTAT) register is a read-only register that indicates the source of the most recent Reset event, indicates a Stop Mode Recovery event, and indicates a Watchdog Timer time-out. Reading this register resets the upper four bits to 0.

This register shares its address with the Watchdog Timer control register, which is writeonly (Table 12).

#### Table 12. Reset Status Register (RSTSTAT)

| BITS  | 7                      | 6    | 5   | 4   | 3        | 2 | 1 | 0 |  |  |

|-------|------------------------|------|-----|-----|----------|---|---|---|--|--|

| FIELD | POR                    | STOP | WDT | EXT | Reserved |   |   |   |  |  |

| RESET | See descriptions below |      |     | 0   | 0        | 0 | 0 | 0 |  |  |

| R/W   | R R R                  |      |     | R   | R        | R | R | R |  |  |

| ADDR  |                        | FF0H |     |     |          |   |   |   |  |  |

| Reset or Stop Mode Recovery Event             | POR | STOP | WDT | EXT |

|-----------------------------------------------|-----|------|-----|-----|

| Power-On Reset                                | 1   | 0    | 0   | 0   |

| Reset using RESET pin assertion               | 0   | 0    | 0   | 1   |

| Reset using WDT time-out                      | 0   | 0    | 1   | 0   |

| Reset using the OCD (OCTCTL[1] set to 1)      | 1   | 0    | 0   | 0   |

| Reset from STOP Mode using DBG Pin driven Low | 1   | 0    | 0   | 0   |

| Stop Mode Recovery using GPIO pin transition  | 0   | 1    | 0   | 0   |

| Stop Mode Recovery using WDT time-out         | 0   | 1    | 1   | 0   |

#### POR—Power-On Reset Indicator

If this bit is set to 1, a Power-On Reset event is occurred. This bit is reset to 0 if a WDT time-out or Stop Mode Recovery occurs. This bit is also reset to 0 when the register is read.

| Port   | Pin | Mnemonic                | Alternate Function Description                         | Alternate Function<br>Set Register AFS1 |

|--------|-----|-------------------------|--------------------------------------------------------|-----------------------------------------|

| Port C | PC0 | Reserved                |                                                        | AFS1[0]: 0                              |

|        |     | ANA4/CINP/LED<br>Drive  | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1                              |

|        | PC1 | Reserved                |                                                        | AFS1[1]: 0                              |

|        |     | ANA5/CINN/ LED<br>Drive | ADC or Comparator Input, or LED drive                  | AFS1[1]: 1                              |

|        | PC2 | Reserved                |                                                        | AFS1[2]: 0                              |

| P      |     | ANA6/LED/<br>VREF*      | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1                              |

|        | PC3 | COUT                    | Comparator Output                                      | AFS1[3]: 0                              |

|        |     | LED                     | LED drive                                              | AFS1[3]: 1                              |

|        | PC4 | Reserved                |                                                        | AFS1[4]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[4]: 1                              |

|        | PC5 | Reserved                |                                                        | AFS1[5]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[5]: 1                              |

|        | PC6 | Reserved                |                                                        | AFS1[6]: 0                              |

|        |     | LED LED Drive           |                                                        | AFS1[6]: 1                              |

|        | PC7 | Reserved                |                                                        | AFS1[7]: 0                              |

|        |     | LED                     | LED Drive                                              | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

**Note:** Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in Port A–C Alternate Function Sub-Registers must also be enabled. \*VREF is available on PC2 in 20-pin parts only.

# **Interrupt Request 1 Register**

The Interrupt Request 1 (IRQ1) register (Table 35) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ1 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU reads the Interrupt Request 1 register to determine if any interrupt requests are pending.

Table 35. Interrupt Request 1 Register (IRQ1)

| BITS  | 7     | 6     | 5    | 4    | 3    | 2    | 1    | 0    |  |  |

|-------|-------|-------|------|------|------|------|------|------|--|--|

| FIELD | PA7VI | PA6CI | PA5I | PA4I | PA3I | PA2I | PA1I | PA0I |  |  |

| RESET | 0     | 0     | 0    | 0    | 0    | 0    | 0    | 0    |  |  |

| R/W   | R/W   | R/W   | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  |  |  |

| ADDR  |       | FC3H  |      |      |      |      |      |      |  |  |

PA7VI—Port A7 Interrupt Request

0 = No interrupt request is pending for GPIO Port A

1 = An interrupt request from GPIO Port A

PA6CI—Port A6 or Comparator Interrupt Request

0 = No interrupt request is pending for GPIO Port A or Comparator

1 = An interrupt request from GPIO Port A or Comparator

PAxI—Port A Pin x Interrupt Request

0 = No interrupt request is pending for GPIO Port A pin x

1 = An interrupt request from GPIO Port A pin x is awaiting service

where x indicates the specific GPIO Port pin number (0-5)

# **Interrupt Request 2 Register**

The Interrupt Request 2 (IRQ2) register (Table 36) stores interrupt requests for both vectored and polled interrupts. When a request is presented to the interrupt controller, the corresponding bit in the IRQ2 register becomes 1. If interrupts are globally enabled (vectored interrupts), the interrupt controller passes an interrupt request to the eZ8 CPU. If interrupts are globally disabled (polled interrupts), the eZ8 CPU can read the Interrupt Request 2 register to determine if any interrupt requests are pending.

# Timers

Z8 Encore! XP<sup>®</sup> F0823 Series products contain up to two 16-bit reloadable timers that are used for timing, event counting, or generation of PWM signals. The timers' features include:

- 16-bit reload counter.

- Programmable prescaler with prescale values from 1 to 128.

- PWM output generation.

- Capture and compare capability.

- External input pin for timer input, clock gating, or capture signal. External input pin signal frequency is limited to a maximum of one-fourth the system clock frequency.

- Timer output pin.

- Timer interrupt.

In addition to the timers described in this chapter, the baud rate generator of the UART (if unused) also provides basic timing functionality. For information on using the baud rate generator as an additional timer, see Universal Asynchronous Receiver/Transmitter on page 93.

# Architecture

Figure 9 displays the architecture of the timers. Timer Block Timer Data Bus Control Block Control Timer 16-Bit Interrupt, Compare Interrupt **Reload Register** PWM, and Timer Timer Output Output System Control Timer Clock 16-Bit Counter I Output with Prescaler Timer Complement Input Compare I Gate 16-Bit Input PWM/Compare Capture Input

Figure 9. Timer Block Diagram

#### **ONE-SHOT Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **CONTINUOUS Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### **COUNTER Mode**

If the timer is enabled the Timer Output signal is complemented after timer reload.

- 0 =Count occurs on the rising edge of the Timer Input signal

- 1 = Count occurs on the falling edge of the Timer Input signal

#### **PWM SINGLE OUTPUT Mode**

0 = Timer Output is forced Low (0) when the timer is disabled. When enabled, the Timer Output is forced High (1) upon PWM count match and forced Low (0) upon Reload.

1 = Timer Output is forced High (1) when the timer is disabled. When enabled, the Timer Output is forced Low (0) upon PWM count match and forced High (1) upon Reload.

#### **CAPTURE Mode**

0 = Count is captured on the rising edge of the Timer Input signal

1 = Count is captured on the falling edge of the Timer Input signal

#### **COMPARE Mode**

When the timer is disabled, the Timer Output signal is set to the value of this bit. When the timer is enabled, the Timer Output signal is complemented upon timer Reload.

#### GATED Mode

0 = Timer counts when the Timer Input signal is High (1) and interrupts are generated on the falling edge of the Timer Input.

1 = Timer counts when the Timer Input signal is Low (0) and interrupts are generated on the rising edge of the Timer Input.

- 3. Clears the UART Receiver interrupt in the applicable Interrupt Request register.

- 4. Executes the IRET instruction to return from the interrupt-service routine and await more data.

# Clear To Send (CTS) Operation

The CTS pin, if enabled by the CTSE bit of the UART Control 0 register, performs flow control on the outgoing transmit datastream. The Clear To Send ( $\overline{\text{CTS}}$ ) input pin is sampled one system clock before beginning any new character transmission. To delay transmission of the next data character, an external receiver must deassert  $\overline{\text{CTS}}$  at least one system clock cycle before a new data transmission begins. For multiple character transmissions, this action is typically performed during Stop Bit transmission. If  $\overline{\text{CTS}}$  deasserts in the middle of a character transmission, the current character is sent completely.

# **MULTIPROCESSOR (9-Bit) Mode**

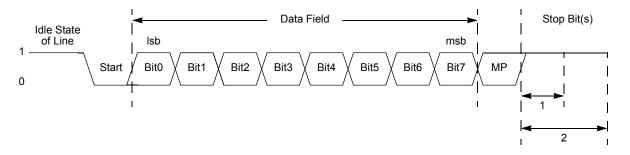

The UART has a MULTIPROCESSOR (9-bit) mode that uses an extra (9<sup>th</sup>) bit for selective communication when a number of processors share a common UART bus. In MULTIPROCESSOR mode (also referred to as 9-bit mode), the multiprocessor bit (MP) is transmitted immediately following the 8-bits of data and immediately preceding the Stop bit(s) as displayed in Figure 13. The character format is given below:

Figure 13. UART Asynchronous MULTIPROCESSOR Mode Data Format

In MULTIPROCESSOR (9-bit) mode, the Parity bit location (9<sup>th</sup> bit) becomes the Multiprocessor control bit. The UART Control 1 and Status 1 registers provide MULTIPROCESSOR (9-bit) mode control and status information. If an automatic address matching scheme is enabled, the UART Address Compare register holds the network address of the device.

#### **MULTIPROCESSOR (9-bit) Mode Receive Interrupts**

When MULTIPROCESSOR mode is enabled, the UART only processes frames addressed to it. The determination of whether a frame of data is addressed to the UART can be made

# **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data register (Table 63). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

### Table 63. UART Receive Data Register (U0RXD)

| BITS  | 7 | 6    | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-------|---|------|---|---|---|---|---|---|--|--|

| FIELD |   | RXD  |   |   |   |   |   |   |  |  |

| RESET | Х | Х    | Х | Х | Х | Х | Х | Х |  |  |

| R/W   | R | R    | R | R | R | R | R | R |  |  |

| ADDR  |   | F40H |   |   |   |   |   |   |  |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 64 and Table 65) identify the current UART operating configuration and status.

Table 64. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6    | 5  | 4  | 3    | 2    | 1   | 0   |  |  |

|-------|-----|------|----|----|------|------|-----|-----|--|--|

| FIELD | RDA | PE   | OE | FE | BRKD | TDRE | TXE | CTS |  |  |

| RESET | 0   | 0    | 0  | 0  | 0    | 1    | 1   | Х   |  |  |

| R/W   | R   | R    | R  | R  | R    | R    | R   | R   |  |  |

| ADDR  |     | F41H |    |    |      |      |     |     |  |  |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty

1 = There is a byte in the UART Receive Data register

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred

1 = A parity error has occurred

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is

PSEL—Parity Select

0 = Even parity is transmitted and expected on all received data

1 = Odd parity is transmitted and expected on all received data

SBRK—Send Break

This bit pauses or breaks data transmission. Sending a break interrupts any transmission in progress, so ensure that the transmitter has finished sending data before setting this bit.

0 = No break is sent

1 = Forces a break condition by setting the output of the transmitter to zero

STOP—Stop Bit Select

0 = The transmitter sends one stop bit

1 = The transmitter sends two stop bits

LBEN—Loop Back Enable

0 = Normal operation

1 = All transmitted data is looped back to the receiver

Table 67. UART Control 1 Register (U0CTL1)

| BITS  | 7       | 6    | 5       | 4    | 3     | 2      | 1      | 0    |  |  |

|-------|---------|------|---------|------|-------|--------|--------|------|--|--|

| FIELD | MPMD[1] | MPEN | MPMD[0] | MPBT | DEPOL | BRGCTL | RDAIRQ | IREN |  |  |

| RESET | 0       | 0    | 0       | 0    | 0     | 0      | 0      | 0    |  |  |

| R/W   | R/W     | R/W  | R/W     | R/W  | R/W   | R/W    | R/W    | R/W  |  |  |

| ADDR  |         | F43H |         |      |       |        |        |      |  |  |

#### MPMD[1:0]—MULTIPROCESSOR Mode

If MULTIPROCESSOR (9-bit) mode is enabled,

00 = The UART generates an interrupt request on all received bytes (data and address)

01 = The UART generates an interrupt request only on received address bytes

10 = The UART generates an interrupt request when a received address byte matches the value stored in the Address Compare Register and on all successive data bytes until an address mismatch occurs

11 = The UART generates an interrupt request on all received data bytes for which the most recent address byte matched the value in the Address Compare Register

MPEN—MULTIPROCESSOR (9-bit) Enable

This bit is used to enable MULTIPROCESSOR (9-bit) mode.

0 = Disable MULTIPROCESSOR (9-bit) mode

1 = Enable MULTIPROCESSOR (9-bit) mode

MPBT—Multiprocessor Bit Transmit

This bit is applicable only when MULTIPROCESSOR (9-bit) mode is enabled. The 9th bit is used by the receiving device to determine if the data byte contains address or data information.

# **Analog-to-Digital Converter**

The Analog-to-Digital Converter (ADC) converts an analog input signal to its digital representation. The features of this sigma-delta ADC include:

- 10-bit resolution

- Eight single-ended analog input sources are multiplexed with general-purpose I/O ports

- Interrupt upon conversion complete

- Bandgap generated internal voltage reference generator with two selectable levels

- Factory offset and gain calibration

# Architecture

Figure 19 displays the major functional blocks of the ADC. An analog multiplexer network selects the ADC input from the available analog pins, ANA0 through ANA7.

REFSELL—Voltage Reference Level Select Low Bit; in conjunction with the High bit (REFSELH) in ADC Control/Status Register 1, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL};

Note:

*This reference is independent of the Comparator reference.*

00= Internal Reference Disabled, reference comes from external pin.

01 = Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

REFEXT—External Reference Select

0 = External reference buffer is disabled; V<sub>ref</sub> pin is available for GPIO functions

1 = The internal ADC reference is buffered and connected to the  $V_{ref}$  pin

#### CONT

0 = Single-shot conversion. ADC data is output once at completion of the 5129 system clock cycles.

1 = Continuous conversion. ADC data updated every 256 system clock cycles.

ANAIN[3:0]—Analog Input Select

These bits select the analog input for conversion. Not all port pins in this list are available in all packages for Z8 Encore! XP<sup>®</sup> F0823 Series. For information on the port pins available with each package style, see Pin Description on page 7. Do not enable unavailable analog inputs. Usage of these bits changes depending on the buffer mode selected in ADC Control/Status Register 1.

For the reserved values, all input switches are disabled to avoid leakage or other undesirable operation. ADC samples taken with reserved bit settings are undefined.

Single-Ended:

0000 = ANA00001 = ANA10010 = ANA20011 = ANA3 0100 = ANA40101 = ANA50110 = ANA60111 = ANA71000 = Reserved1001 = Reserved1010 = Reserved1011 = Reserved1100 = Reserved1101 = Reserved1110 = Reserved1111 = Reserved

## **ADC Control/Status Register 1**

The second ADC Control register contains the voltage reference level selection bit.

#### Table 73. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7       | 6        | 5   | 4   | 3   | 2   | 1   | 0   |  |

|-------|---------|----------|-----|-----|-----|-----|-----|-----|--|

| FIELD | REFSELH | Reserved |     |     |     |     |     |     |  |

| RESET | 1       | 0        | 0   | 0   | 0   | 0   | 0   | 0   |  |

| R/W   | R/W     | R/W      | R/W | R/W | R/W | R/W | R/W | R/W |  |

| ADDR  |         | F71H     |     |     |     |     |     |     |  |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

# ADC Data High Byte Register

The ADC Data High Byte register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data High Byte Register (ADCD\_H)

| BITS  | 7 | 6     | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|-------|---|----|----|---|---|---|--|--|

| FIELD |   | ADCDH |   |    |    |   |   |   |  |  |

| RESET | Х | Х     | Х | Х  | Х  | Х | Х | Х |  |  |

| R/W   | R | R     | R | R  | R  | R | R | R |  |  |

| ADDR  |   |       |   | F7 | 2H |   |   |   |  |  |

#### ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

# **Caution:** Unintentional accesses to the oscillator control register can actually stop the chip by switching to a non-functioning oscillator. To prevent this condition, the oscillator control block employs a register unlocking/locking scheme.

#### **OSC Control Register Unlocking/Locking**

To write the oscillator control register, unlock it by making two writes to the OSCCTL register with the values E7H followed by 18H. A third write to the OSCCTL register changes the value of the actual register and returns the register to a locked state. Any other sequence of oscillator control register writes has no effect. The values written to unlock the register must be ordered correctly, but are not necessarily consecutive. It is possible to write to or read from other registers within the unlocking/locking operation.

When selecting a new clock source, the primary oscillator failure detection circuitry and the Watchdog Timer oscillator failure circuitry must be disabled. If POFEN and WOFEN are not disabled prior to a clock switch-over, it is possible to generate an interrupt for a failure of either oscillator. The Failure detection circuitry can be enabled anytime after a successful write of OSCSEL in the oscillator control register.

The internal precision oscillator is enabled by default. If the user code changes to a different oscillator, it is appropriate to disable the IPO for power savings. Disabling the IPO does not occur automatically.

#### **Clock Failure Detection and Recovery**

#### **Primary Oscillator Failure**

Z8 Encore! XP<sup>®</sup> F0823 Series devices can generate non-maskable interrupt-like events when the primary oscillator fails. To maintain system function in this situation, the clock failure recovery circuitry automatically forces the Watchdog Timer oscillator to drive the system clock. The Watchdog Timer oscillator must be enabled to allow the recovery. Although this oscillator runs at a much slower speed than the original system clock, the CPU continues to operate, allowing execution of a clock failure vector and software routines that either remedy the oscillator failure or issue a failure alert. This automatic switchover is not available if the Watchdog Timer is the primary oscillator. It is also unavailable if the Watchdog Timer oscillator is disabled, though it is not necessary to enable the Watchdog Timer reset function outlined in the Watchdog Timer on page 87.

The primary oscillator failure detection circuitry asserts if the system clock frequency drops below 1 kHz  $\pm$ 50%. If an external signal is selected as the system oscillator, it is possible that a very slow but non-failing clock can generate a failure condition. Under these conditions, do not enable the clock failure circuitry (POFEN must be deasserted in the OSCCTL register).

#### Watchdog Timer Failure

In the event of a Watchdog Timer oscillator failure, a similar non-maskable interrupt-like event is issued. This event does not trigger an attendant clock switch-over, but alerts the CPU of the failure. After a Watchdog Timer failure, it is no longer possible to detect a primary oscillator failure. The failure detection circuitry does not function if the Watchdog Timer is used as the primary oscillator or if the Watchdog Timer oscillator has been disabled. For either of these cases, it is necessary to disable the detection circuitry by deasserting the WDFEN bit of the OSCCTL register.

The Watchdog Timer oscillator failure detection circuit counts system clocks while searching for a Watchdog Timer clock. The logic counts 8004 system clock cycles before determining that a failure has occurred. The system clock rate determines the speed at which the Watchdog Timer failure can be detected. A very slow system clock results in very slow detection times.

**Caution:** It is possible to disable the clock failure detection circuitry as well as all functioning clock sources. In this case, the Z8 Encore! XP F0823 Series device ceases functioning and can only be recovered by Power-On Reset.

# **Oscillator Control Register Definitions**

The following section provides the bit definitions for the Oscillator Control register.

#### **Oscillator Control Register**

The Oscillator Control register (OSCCTL) enables/disables the various oscillator circuits, enables/disables the failure detection/recovery circuitry and selects the primary oscillator, which becomes the system clock.

The Oscillator Control register must be unlocked before writing. Writing the two step sequence E7H followed by 18H to the Oscillator Control Register unlocks it. The register is locked at successful completion of a register write to the OSCCTL.

| BITS  | 7     | 6        | 5     | 4     | 3     | 2   | 1      | 0   |  |  |

|-------|-------|----------|-------|-------|-------|-----|--------|-----|--|--|

| FIELD | INTEN | Reserved | WDTEN | POFEN | WDFEN |     | SCKSEL |     |  |  |

| RESET | 1     | 0        | 1     | 0     | 0     | 0   | 0      | 0   |  |  |

| R/W   | R/W   | R/W      | R/W   | R/W   | R/W   | R/W | R/W    | R/W |  |  |

| ADDR  |       | F86H     |       |       |       |     |        |     |  |  |

Table 102. Oscillator Control Register (OSCCTL)

• Rotate and Shift

Tables 107 through Table 114 contain the instructions belonging to each group and the number of operands required for each instruction. Some instructions appear in more than one table as these instruction can be considered as a subset of more than one category. Within these tables, the source operand is identified as 'src', the destination operand is 'dst' and a condition code is 'cc'.

| Mnemonic | Operands | Instruction                                   |  |  |  |

|----------|----------|-----------------------------------------------|--|--|--|

|          | •        |                                               |  |  |  |

| ADC      | dst, src | Add with Carry                                |  |  |  |

| ADCX     | dst, src | Add with Carry using Extended Addressing      |  |  |  |

| ADD      | dst, src | Add                                           |  |  |  |

| ADDX     | dst, src | Add using Extended Addressing                 |  |  |  |

| CP       | dst, src | Compare                                       |  |  |  |

| CPC      | dst, src | Compare with Carry                            |  |  |  |

| CPCX     | dst, src | Compare with Carry using Extended Addressing  |  |  |  |

| СРХ      | dst, src | Compare using Extended Addressing             |  |  |  |

| DA       | dst      | Decimal Adjust                                |  |  |  |

| DEC      | dst      | Decrement                                     |  |  |  |

| DECW     | dst      | Decrement Word                                |  |  |  |

| INC      | dst      | Increment                                     |  |  |  |

| INCW     | dst      | Increment Word                                |  |  |  |

| MULT     | dst      | Multiply                                      |  |  |  |

| SBC      | dst, src | Subtract with Carry                           |  |  |  |

| SBCX     | dst, src | Subtract with Carry using Extended Addressing |  |  |  |

| SUB      | dst, src | Subtract                                      |  |  |  |

| SUBX     | dst, src | Subtract using Extended Addressing            |  |  |  |

|          |          |                                               |  |  |  |

#### **Table 107. Arithmetic Instructions**

| Table 1 | 08. Bit | Manir | oulation | Instructions |  |

|---------|---------|-------|----------|--------------|--|

|         | 00. Dit | mann  | Julution | monuciono    |  |

| Mnemonic | Operands    | Instruction                                          |

|----------|-------------|------------------------------------------------------|

| BCLR     | bit, dst    | Bit Clear                                            |

| BIT      | p, bit, dst | Bit Set or Clear                                     |

| BSET     | bit, dst    | Bit Set                                              |

| BSWAP    | dst         | Bit Swap                                             |

| CCF      | _           | Complement Carry Flag                                |

| RCF      | _           | Reset Carry Flag                                     |

| SCF      | _           | Set Carry Flag                                       |

| ТСМ      | dst, src    | Test Complement Under Mask                           |

| ТСМХ     | dst, src    | Test Complement Under Mask using Extended Addressing |

| ТМ       | dst, src    | Test Under Mask                                      |

| ТМХ      | dst, src    | Test Under Mask using Extended Addressing            |

Table 109. Block Transfer Instructions

| Mnemonic | Operands | Instruction                                                         |

|----------|----------|---------------------------------------------------------------------|

| LDCI     | dst, src | Load Constant to/from Program Memory and Auto-Increment Addresses   |

| LDEI     | dst, src | Load External Data to/from Data Memory and Auto-Increment Addresses |

#### Table 110. CPU Control Instructions

| Mnemonic | Operands | Instruction           |

|----------|----------|-----------------------|

| ATM      | _        | Atomic Execution      |

| CCF      | _        | Complement Carry Flag |

| DI       | —        | Disable Interrupts    |

| EI       | _        | Enable Interrupts     |

| HALT     | _        | HALT Mode             |

| NOP      | _        | No Operation          |

| RCF      | _        | Reset Carry Flag      |

| Part Number                              | F           |           | ines      | Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |

|------------------------------------------|-------------|-----------|-----------|------------|------------------------|---------------------|----------------|---------------------|

| Part                                     | Flash       | RAM       | I/O Lines | Inter      | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |

| Z8 Encore! XP with 8                     | KB Flash    |           |           |            |                        |                     |                |                     |

| Standard Temperatur                      | re: 0 °C to | 70 °C     |           |            |                        |                     |                |                     |

| Z8F0813PB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005SC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005SC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005SC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Extended Temperatu                       | re: -40 °C  | to 105 °( | 0         |            |                        |                     |                |                     |

| Z8F0813PB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | PDIP 8-pin package  |

| Z8F0813QB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | QFN 8-pin package   |

| Z8F0813SB005EC                           | 8 KB        | 1 KB      | 6         | 12         | 2                      | 0                   | 1              | SOIC 8-pin package  |

| Z8F0813SH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SOIC 20-pin package |

| Z8F0813HH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | SSOP 20-pin package |

| Z8F0813PH005EC                           | 8 KB        | 1 KB      | 16        | 18         | 2                      | 0                   | 1              | PDIP 20-pin package |

| Z8F0813SJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SOIC 28-pin package |

| Z8F0813HJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | SSOP 28-pin package |

| Z8F0813PJ005EC                           | 8 KB        | 1 KB      | 24        | 18         | 2                      | 0                   | 1              | PDIP 28-pin package |

| Replace C with G for Lead-Free Packaging |             |           |           |            |                        |                     |                |                     |

| Jaquing<br>Trad<br>Z8 Encore! XP <sup>®</sup> F0823 S | Flash | W W W W W W W W W W W W W W W W W W W | t I/O Lines | ∓<br>Interrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description                |

|-------------------------------------------------------|-------|---------------------------------------|-------------|-----------------|------------------------|---------------------|----------------|----------------------------|

| Z8F08A28100KITG                                       | -     |                                       |             |                 |                        |                     |                |                            |

| Z8F04A28100KITG                                       |       | Z8 Enco                               | re! XP      | F042            | A Serie                | es De               | velo           | pment Kit (20- and 28-Pin) |

| Z8F04A08100KITG                                       |       | Z8 Enco                               | re! XP      | F042            | A Serie                | es De               | velo           | pment Kit (8-Pin)          |

| ZUSBSC00100ZACG                                       |       | USB Sm                                | art Ca      | ble A           | ccesso                 | ry Ki               | t              |                            |

| ZUSBOPTSC01ZACG                                       |       | Opto-Iso                              | olated      | USB             | Smart (                | Cable               | Acc            | essory Kit                 |

| ZENETSC0100ZACG Ethernet Smart Cable Accessory Kit    |       |                                       |             |                 |                        | t                   |                |                            |