Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Core ProcessoreZ8Core Size8-BitSpeed5MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-Nu Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300°, 7.62mm) | Details                    |                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------------------------------|

| Core Size8-BitSpeed5MHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size.Nutage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4×10bOperating Temperature.40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8.DIP (0.300", 7.62mm)Supplier Device Package.        | Product Status             | Obsolete                                                  |

| SpeedSMHzConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-       | Core Processor             | eZ8                                                       |

| r.ConnectivityIrDA, UART/USARTPeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size8KB (8K x 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOgerating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-              | Core Size                  | 8-Bit                                                     |

| PeripheralsBrown-out Detect/Reset, LED, POR, PWM, WDTNumber of I/O6Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                            | Speed                      | 5MHz                                                      |

| Number of I/O6Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4×10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8.DIP (0.300", 7.62mm)Supplier Device Package-                                                                          | Connectivity               | IrDA, UART/USART                                          |

| Program Memory Size8KB (8K × 8)Program Memory TypeFLASHEEPROM Size-RAM Size1K × 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeS-DIP (0.300", 7.62mm)Package / Case-                                                                                                                           | Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Program Memory TypeFLASHEEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                       | Number of I/O              | 6                                                         |

| EEPROM Size-RAM Size1K x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                               | Program Memory Size        | 8KB (8K x 8)                                              |

| RAM SizeIK x 8Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                                           | Program Memory Type        | FLASH                                                     |

| Voltage - Supply (Vcc/Vdd)2.7V ~ 3.6VData ConvertersA/D 4x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                                                         | EEPROM Size                | <u> </u>                                                  |

| Data ConvertersA/D 4x10bOscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                                                                                              | RAM Size                   | 1K x 8                                                    |

| Oscillator TypeInternalOperating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                                                                                                                      | Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Operating Temperature-40°C ~ 105°C (TA)Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                                                                                                                                             | Data Converters            | A/D 4x10b                                                 |

| Mounting TypeThrough HolePackage / Case8-DIP (0.300", 7.62mm)Supplier Device Package-                                                                                                                                                                                                                                                                                                    | Oscillator Type            | Internal                                                  |

| Package / Case     8-DIP (0.300", 7.62mm)       Supplier Device Package     -                                                                                                                                                                                                                                                                                                            | Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Supplier Device Package                                                                                                                                                                                                                                                                                                                                                                  | Mounting Type              | Through Hole                                              |

|                                                                                                                                                                                                                                                                                                                                                                                          | Package / Case             | 8-DIP (0.300", 7.62mm)                                    |

| Purchase URL https://www.e-xfl.com/product-detail/zilog/z8f0823pb005ec                                                                                                                                                                                                                                                                                                                   | Supplier Device Package    | -                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                          | Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823pb005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Address (Hex)   | Register Description      | Mnemonic | Reset (Hex) | Page No |

|-----------------|---------------------------|----------|-------------|---------|

| F0C             | Timer 1 PWM High Byte     | T1PWMH   | 00          | 81      |

| F0D             | Timer 1 PWM Low Byte      | T1PWML   | 00          | 82      |

| F0E             | Timer 1 Control 0         | T1CTL0   | 00          | 82      |

| F0F             | Timer 1 Control 1         | T1CTL1   | 00          | 80      |

| F10–F3F         | Reserved                  | —        | XX          |         |

| UART            |                           |          |             |         |

| F40             | UART0 Transmit Data       | U0TXD    | XX          | 104     |

|                 | UART0 Receive Data        | U0RXD    | XX          | 105     |

| F41             | UART0 Status 0            | U0STAT0  | 0000011Xb   | 105     |

| F42             | UART0 Control 0           | U0CTL0   | 00          | 107     |

| F43             | UART0 Control 1           | U0CTL1   | 00          | 107     |

| F44             | UART0 Status 1            | U0STAT1  | 00          | 106     |

| F45             | UART0 Address Compare     | U0ADDR   | 00          | 109     |

| F46             | UART0 Baud Rate High Byte | U0BRH    | FF          | 110     |

| F47             | UART0 Baud Rate Low Byte  | U0BRL    | FF          | 110     |

| F48–F6F         | Reserved                  | _        | XX          |         |

| Analog-to-Digit | al Converter (ADC)        |          |             |         |

| F70             | ADC Control 0             | ADCCTL0  | 00          | 122     |

| F71             | ADC Control 1             | ADCCTL1  | 80          | 122     |

| F72             | ADC Data High Byte        | ADCD_H   | XX          | 124     |

| F73             | ADC Data Low Bits         | ADCD_L   | XX          | 124     |

| F74–F7F         | Reserved                  | _        | XX          |         |

| Low Power Cor   | ntrol                     |          |             |         |

| F80             | Power Control 0           | PWRCTL0  | 80          | 33      |

| F81             | Reserved                  |          | XX          |         |

| LED Controller  |                           |          |             |         |

| F82             | LED Drive Enable          | LEDEN    | 00          | 51      |

| F83             | LED Drive Level High Byte | LEDLVLH  | 00          | 51      |

| F84             | LED Drive Level Low Byte  | LEDLVLL  | 00          | 52      |

| F85             | Reserved                  | _        | XX          |         |

| Oscillator Cont | rol                       |          |             |         |

| F86             | Oscillator Control        | OSCCTL   | A0          | 167     |

| F87–F8F         | Reserved                  | _        | XX          |         |

| Comparator 0    |                           |          |             |         |

| F90             | Comparator 0 Control      | CMP0     | 14          | 128     |

|                 |                           |          |             |         |

| Address (Hex)   | Register Description    | Mnemonic | Reset (Hex) | Page No |

|-----------------|-------------------------|----------|-------------|---------|

| F91–FBF         | Reserved                | —        | XX          |         |

| Interrupt Contr | oller                   |          |             |         |

| FC0             | Interrupt Request 0     | IRQ0     | 00          | 58      |

| FC1             | IRQ0 Enable High Bit    | IRQ0ENH  | 00          | 60      |

| FC2             | IRQ0 Enable Low Bit     | IRQ0ENL  | 00          | 61      |

| FC3             | Interrupt Request 1     | IRQ1     | 00          | 59      |

| FC4             | IRQ1 Enable High Bit    | IRQ1ENH  | 00          | 62      |

| FC5             | IRQ1 Enable Low Bit     | IRQ1ENL  | 00          | 62      |

| FC6             | Interrupt Request 2     | IRQ2     | 00          | 60      |

| FC7             | IRQ2 Enable High Bit    | IRQ2ENH  | 00          | 63      |

| FC8             | IRQ2 Enable Low Bit     | IRQ2ENL  | 00          | 63      |

| FC9–FCC         | Reserved                |          | XX          |         |

| FCD             | Interrupt Edge Select   | IRQES    | 00          | 64      |

| FCE             | Shared Interrupt Select | IRQSS    | 00          | 64      |

| FCF             | Interrupt Control       | IRQCTL   | 00          | 65      |

| GPIO Port A     |                         |          |             |         |

| FD0             | Port A Address          | PAADDR   | 00          | 43      |

| FD1             | Port A Control          | PACTL    | 00          | 45      |

| FD2             | Port A Input Data       | PAIN     | XX          | 45      |

| FD3             | Port A Output Data      | PAOUT    | 00          | 45      |

| GPIO Port B     |                         |          |             |         |

| FD4             | Port B Address          | PBADDR   | 00          | 43      |

| FD5             | Port B Control          | PBCTL    | 00          | 45      |

| FD6             | Port B Input Data       | PBIN     | XX          | 45      |

| FD7             | Port B Output Data      | PBOUT    | 00          | 45      |

| GPIO Port C     | ·                       |          |             |         |

| FD8             | Port C Address          | PCADDR   | 00          | 43      |

| FD9             | Port C Control          | PCCTL    | 00          | 45      |

| FDA             | Port C Input Data       | PCIN     | XX          | 45      |

| FDB             | Port C Output Data      | PCOUT    | 00          | 45      |

| FDC-FEF         | Reserved                | _        | XX          |         |

| Watchdog Time   |                         |          |             |         |

| FF0             | Reset Status            | RSTSTAT  | XX          | 90      |

| -               | Watchdog Timer Control  | WDTCTL   | XX          | 90      |

|                 | 0                       | WDTU     |             |         |

## Table 8. Register File Address Map (Continued)

# Z8 Encore! XP<sup>®</sup> F0823 Series Product Specification

| Port   | Pin | Mnemonic                                                   | Alternate Function Description                         | Alternate Function<br>Set Register AFS1 |

|--------|-----|------------------------------------------------------------|--------------------------------------------------------|-----------------------------------------|

| Port C | PC0 | Reserved                                                   |                                                        | AFS1[0]: 0                              |

|        |     | ANA4/CINP/LED<br>Drive                                     | ADC or Comparator Input, or LED drive                  | AFS1[0]: 1                              |

|        | PC1 | Reserved                                                   |                                                        | AFS1[1]: 0                              |

|        |     | ANA5/CINN/ LED ADC or Comparator Input, or LED drive Drive |                                                        | AFS1[1]: 1                              |

|        | PC2 | Reserved                                                   |                                                        | AFS1[2]: 0                              |

| PC     |     | ANA6/LED/<br>VREF*                                         | ADC Analog Input or LED Drive or ADC Voltage Reference | AFS1[2]: 1                              |

|        | PC3 | COUT                                                       | Comparator Output                                      | AFS1[3]: 0                              |

|        |     | LED                                                        | LED drive                                              | AFS1[3]: 1                              |

|        | PC4 | Reserved                                                   |                                                        | AFS1[4]: 0                              |

|        |     | LED                                                        | LED Drive                                              | AFS1[4]: 1                              |

|        | PC5 | Reserved                                                   |                                                        | AFS1[5]: 0                              |

|        |     | LED                                                        | LED Drive                                              | AFS1[5]: 1                              |

|        | PC6 | Reserved                                                   |                                                        | AFS1[6]: 0                              |

|        |     | LED                                                        | LED Drive                                              | AFS1[6]: 1                              |

|        | PC7 | Reserved                                                   |                                                        | AFS1[7]: 0                              |

|        |     | LED                                                        | LED Drive                                              | AFS1[7]: 1                              |

#### Table 15. Port Alternate Function Mapping (Non 8-Pin Parts) (Continued)

**Note:** Because there are at most two choices of alternate function for any pin of Port C, the Alternate Function Set register AFS2 is implemented but not used to select the function. Also, Alternate Function selection as described in Port A–C Alternate Function Sub-Registers must also be enabled. \*VREF is available on PC2 in 20-pin parts only.

# **Interrupt Controller**

The interrupt controller on the Z8 Encore! XP<sup>®</sup> F0823 Series products prioritizes the interrupt requests from the on-chip peripherals and the GPIO port pins. The features of interrupt controller include:

- 20 unique interrupt vectors

- 12 GPIO port pin interrupt sources (two are shared)

- 8 on-chip peripheral interrupt sources (two are shared)

- Flexible GPIO interrupts

- Eight selectable rising and falling edge GPIO interrupts

- Four dual-edge interrupts

- Three levels of individually programmable interrupt priority

- Watchdog Timer can be configured to generate an interrupt

Interrupt requests (IRQs) allow peripheral devices to suspend CPU operation in an orderly manner and force the CPU to start an interrupt service routine (ISR). Usually this interrupt service routine is involved with the exchange of data, status information, or control information between the CPU and the interrupting peripheral. When the service routine is completed, the CPU returns to the operation from which it was interrupted.

The eZ8 CPU supports both vectored and polled interrupt handling. For polled interrupts, the interrupt controller has no effect on operation. For more information on interrupt servicing by the eZ8 CPU, refer to *eZ8 CPU Core User Manual (UM0128)* available for download at <u>www.zilog.com</u>.

# **Interrupt Vector Listing**

Table 33 lists all of the interrupts available in order of priority. The interrupt vector is stored with the most-significant byte (MSB) at the even Program Memory address and the least-significant byte (LSB) at the following odd Program Memory address.

**Note:** Some port interrupts are not available on the 8- and 20-pin packages. The ADC interrupt is unavailable on devices not containing an ADC.

# Operation

The timers are 16-bit up-counters. Minimum time-out delay is set by loading the value 0001H into the Timer Reload High and Low Byte registers and setting the prescale value to 1. Maximum time-out delay is set by loading the value 0000H into the Timer Reload High and Low Byte registers and setting the prescale value to 128. If the Timer reaches FFFFH, the timer rolls over to 0000H and continues counting.

# **Timer Operating Modes**

The timers can be configured to operate in the following modes:

## **ONE-SHOT Mode**

In ONE-SHOT mode, the timer counts up to the 16-bit Reload value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Reload value, the timer generates an interrupt and the count value in the Timer High and Low Byte registers is reset to 0001H. The timer is automatically disabled and stops counting.

Also, if the Timer Output alternate function is enabled, the Timer Output pin changes state for one system clock cycle (from Low to High or from High to Low) upon timer Reload. If it is appropriate to have the Timer Output make a state change at a One-Shot time-out (rather than a single cycle pulse), first set the TPOL bit in the Timer Control register to the start value before enabling ONE-SHOT mode. After starting the timer, set TPOL to the opposite bit value.

Follow the steps below for configuring a timer for ONE-SHOT mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for ONE-SHOT mode

- Set the prescale value

- Set the initial output level (High or Low) if using the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

#### **PWM SINGLE OUTPUT Mode**

In PWM SINGLE OUTPUT mode, the timer outputs a PWM output signal through a GPIO port pin. The timer input is the system clock. The timer first counts up to the 16-bit PWM match value stored in the Timer PWM High and Low Byte registers. When the timer count value matches the PWM value, the Timer Output toggles. The timer continues counting until it reaches the Reload value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes.

If the TPOL bit in the Timer Control register is set to 1, the Timer Output signal begins as a High (1) and transitions to a Low (0) when the timer value matches the PWM value. The Timer Output signal returns to a High (1) after the timer reaches the Reload value and is reset to 0001H.

If the TPOL bit in the Timer Control register is set to 0, the Timer Output signal begins as a Low (0) and transitions to a High (1) when the timer value matches the PWM value. The Timer Output signal returns to a Low (0) after the timer reaches the Reload value and is reset to 0001H.

Follow the steps below for configuring a timer for PWM Single Output mode and initiating the PWM operation:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for PWM mode

- Set the prescale value

- Set the initial logic level (High or Low) and PWM High/Low transition for the Timer Output alternate function

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H). This only affects the first pass in PWM mode. After the first timer reset in PWM mode, counting always begins at the reset value of 0001H.

- 3. Write to the PWM High and Low Byte registers to set the PWM value.

- 4. Write to the Timer Reload High and Low Byte registers to set the Reload value (PWM period). The Reload value must be greater than the PWM value.

- 5. If appropriate, enable the timer interrupt and set the timer interrupt priority by writing to the relevant interrupt registers.

- 6. Configure the associated GPIO port pin for the Timer Output alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

The PWM period is represented by the following equation:

$PWM Period (s) = \frac{Reload Value \times Prescale}{System Clock Frequency (Hz)}$

generated and the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is because of an input capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Reload value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not caused by an input capture event.

Follow the steps below for configuring a timer for CAPTURE RESTART mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer.

- Configure the timer for CAPTURE RESTART mode. Setting the mode also involves writing to TMODEHI bit in TxCTL1 register.

- Set the prescale value.

- Set the Capture edge (rising or falling) for the Timer Input.

- 2. Write to the Timer High and Low Byte registers to set the starting count value (typically 0001H).

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Clear the Timer PWM High and Low Byte registers to 0000H. This allows the software to determine if interrupts were generated by either a Capture or a Reload event. If the PWM High and Low Byte registers still contain 0000H after the interrupt, the interrupt was generated by a Reload.

- 5. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input Capture and Reload events. If appropriate, configure the timer interrupt to be generated only at the input Capture event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 6. Configure the associated GPIO port pin for the Timer Input alternate function.

- 7. Write to the Timer Control register to enable the timer and initiate counting.

In CAPTURE mode, the elapsed time from timer start to Capture event can be calculated using the following equation:

Capture Elapsed Time (s) =

$$\frac{(Capture Value - Start Value) \times Prescale}{System Clock Frequency (Hz)}$$

#### COMPARE Mode

In COMPARE mode, the timer counts up to the 16-bit maximum Compare value stored in the Timer Reload High and Low Byte registers. The timer input is the system clock. Upon reaching the Compare value, the timer generates an interrupt and counting continues (the

Follow the steps below to configure a timer for GATED mode and to initiate the count:

- 1. Write to the Timer Control register to:

- Disable the timer

- Configure the timer for Gated mode

- Set the prescale value

- 2. Write to the Timer High and Low Byte registers to set the starting count value. Writing these registers only affects the first pass in GATED mode. After the first timer reset in GATED mode, counting always begins at the reset value of 0001H.

- 3. Write to the Timer Reload High and Low Byte registers to set the Reload value.

- 4. Enable the timer interrupt, if appropriate, and set the timer interrupt priority by writing to the relevant interrupt registers. By default, the timer interrupt is generated for both input deassertion and Reload events. If appropriate, configure the timer interrupt to be generated only at the input deassertion event or the Reload event by setting TICONFIG field of the TxCTL1 register.

- 5. Configure the associated GPIO port pin for the Timer Input alternate function.

- 6. Write to the Timer Control register to enable the timer.

- 7. Assert the Timer Input signal to initiate the counting.

#### **CAPTURE/COMPARE Mode**

In CAPTURE/COMPARE mode, the timer begins counting on the first external Timer Input transition. The acceptable transition (rising edge or falling edge) is set by the TPOL bit in the Timer Control Register. The timer input is the system clock.

Every subsequent acceptable transition (after the first) of the Timer Input signal captures the current count value. The Capture value is written to the Timer PWM High and Low Byte Registers. When the Capture event occurs, an interrupt is generated, the count value in the Timer High and Low Byte registers is reset to 0001H, and counting resumes. The INPCAP bit in TxCTL1 register is set to indicate the timer interrupt is caused by an input Capture event.

If no Capture event occurs, the timer counts up to the 16-bit Compare value stored in the Timer Reload High and Low Byte registers. Upon reaching the Compare value, the timer generates an interrupt, the count value in the Timer High and Low Byte registers is reset to 0001H and counting resumes. The INPCAP bit in TxCTL1 register is cleared to indicate the timer interrupt is not because of an input Capture event.

Follow the steps below for configuring a timer for CAPTURE/COMPARE mode and initiating the count:

- 1. Write to the Timer Control register to:

- Disable the timer

# **UART Receive Data Register**

Data bytes received through the RXD*x* pin are stored in the UART Receive Data register (Table 63). The read-only UART Receive Data register shares a Register File address with the Write-only UART Transmit Data register.

# Table 63. UART Receive Data Register (U0RXD)

| BITS  | 7 | 6             | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|---------------|---|----|----|---|---|---|--|

| FIELD |   | RXD           |   |    |    |   |   |   |  |

| RESET | Х | Х             | Х | Х  | Х  | Х | Х | Х |  |

| R/W   | R | R R R R R R R |   |    |    |   |   |   |  |

| ADDR  |   |               |   | F4 | 0H |   |   |   |  |

RXD—Receive Data

UART receiver data byte from the RXDx pin

# **UART Status 0 Register**

The UART Status 0 and Status 1 registers (Table 64 and Table 65) identify the current UART operating configuration and status.

Table 64. UART Status 0 Register (U0STAT0)

| BITS  | 7   | 6    | 5  | 4  | 3    | 2    | 1   | 0   |

|-------|-----|------|----|----|------|------|-----|-----|

| FIELD | RDA | PE   | OE | FE | BRKD | TDRE | TXE | CTS |

| RESET | 0   | 0    | 0  | 0  | 0    | 1    | 1   | Х   |

| R/W   | R   | R    | R  | R  | R    | R    | R   | R   |

| ADDR  |     | F41H |    |    |      |      |     |     |

RDA—Receive Data Available

This bit indicates that the UART Receive Data register has received data. Reading the UART Receive Data register clears this bit.

0 = The UART Receive Data register is empty

1 = There is a byte in the UART Receive Data register

PE—Parity Error

This bit indicates that a parity error has occurred. Reading the UART Receive Data register clears this bit.

0 = No parity error has occurred

1 = A parity error has occurred

OE—Overrun Error

This bit indicates that an overrun error has occurred. An overrun occurs when new data is

#### 124

# **ADC Control/Status Register 1**

The second ADC Control register contains the voltage reference level selection bit.

#### Table 73. ADC Control/Status Register 1 (ADCCTL1)

| BITS  | 7       | 6    | 5                       | 4 | 3 | 2 | 1 | 0 |

|-------|---------|------|-------------------------|---|---|---|---|---|

| FIELD | REFSELH |      | Reserved                |   |   |   |   |   |

| RESET | 1       | 0    | 0 0 0 0 0 0             |   |   |   |   |   |

| R/W   | R/W     | R/W  | R/W R/W R/W R/W R/W R/W |   |   |   |   |   |

| ADDR  |         | F71H |                         |   |   |   |   |   |

REFSELH—Voltage Reference Level Select High Bit; in conjunction with the Low bit (REFSELL) in ADC Control Register 0, this determines the level of the internal voltage reference; the following details the effects of {REFSELH, REFSELL}; this reference is independent of the Comparator reference

00= Internal Reference Disabled, reference comes from external pin

01= Internal Reference set to 1.0 V

10= Internal Reference set to 2.0 V (default)

# ADC Data High Byte Register

The ADC Data High Byte register contains the upper eight bits of the ADC output. The output is an 11-bit two's complement value. During a single-shot conversion, this value is invalid. Access to the ADC Data High Byte register is read-only. Reading the ADC Data High Byte register latches data in the ADC Low Bits register.

Table 74. ADC Data High Byte Register (ADCD\_H)

| BITS  | 7 | 6             | 5 | 4  | 3  | 2 | 1 | 0 |  |

|-------|---|---------------|---|----|----|---|---|---|--|

| FIELD |   | ADCDH         |   |    |    |   |   |   |  |

| RESET | Х | Х             | Х | Х  | Х  | Х | Х | Х |  |

| R/W   | R | R R R R R R R |   |    |    |   |   |   |  |

| ADDR  |   |               |   | F7 | 2H |   |   |   |  |

#### ADCDH—ADC Data High Byte

This byte contains the upper eight bits of the ADC output. These bits are not valid during a single-shot conversion. During a continuous conversion, the most recent conversion output is held in this register. These bits are undefined after a Reset.

### Table 83. Flash Frequency High Byte Register (FFREQH)

| BITS  | 7   | 6                           | 5 | 4 | 3 | 2 | 1 | 0 |  |

|-------|-----|-----------------------------|---|---|---|---|---|---|--|

| FIELD |     | FFREQH                      |   |   |   |   |   |   |  |

| RESET | 0   | 0                           | 0 | 0 | 0 | 0 | 0 | 0 |  |

| R/W   | R/W | R/W R/W R/W R/W R/W R/W R/W |   |   |   |   |   |   |  |

| ADDR  |     | FFAH                        |   |   |   |   |   |   |  |

FFREQH—Flash Frequency High Byte High byte of the 16-bit Flash Frequency value

## Table 84. Flash Frequency Low Byte Register (FFREQL)

| BITS  | 7 | 6      | 5 | 4  | 3  | 2 | 1 | 0 |  |  |

|-------|---|--------|---|----|----|---|---|---|--|--|

| FIELD |   | FFREQL |   |    |    |   |   |   |  |  |

| RESET |   | 0      |   |    |    |   |   |   |  |  |

| R/W   |   | R/W    |   |    |    |   |   |   |  |  |

| ADDR  |   |        |   | FF | BH |   |   |   |  |  |

FFREQL—Flash Frequency Low Byte Low byte of the 16-bit Flash Frequency value

147

Reserved— Altering this register may result in incorrect device operation.

# Trim Bit Address 0002H

#### Table 91. Trim Option Bits at 0002H (TIPO)

| BITS      | 7                                               | 6        | 5 | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|-------------------------------------------------|----------|---|---|---|---|---|---|--|--|

| FIELD     |                                                 | IPO_TRIM |   |   |   |   |   |   |  |  |

| RESET     |                                                 | U        |   |   |   |   |   |   |  |  |

| R/W       |                                                 | R/W      |   |   |   |   |   |   |  |  |

| ADDR      | Information Page Memory 0022H                   |          |   |   |   |   |   |   |  |  |

| Note: U = | Note: U = Unchanged by Reset. R/W = Read/Write. |          |   |   |   |   |   |   |  |  |

IPO\_TRIM—Internal Precision Oscillator Trim Byte Contains trimming bits for Internal Precision Oscillator.

# Trim Bit Address 0003H—Reserved

# Trim Bit Address 0004H—Reserved

# **Zilog Calibration Data**

# **ADC Calibration Data**

#### Table 92. ADC Calibration Bits

| BITS      | 7                                   | 6            | 5            | 4   | 3   | 2   | 1   | 0   |  |  |

|-----------|-------------------------------------|--------------|--------------|-----|-----|-----|-----|-----|--|--|

| FIELD     | ADC_CAL                             |              |              |     |     |     |     |     |  |  |

| RESET     |                                     |              |              |     |     |     |     | U   |  |  |

| R/W       | R/W                                 | R/W          | R/W          | R/W | R/W | R/W | R/W | R/W |  |  |

| ADDR      | Information Page Memory 0060H–007DH |              |              |     |     |     |     |     |  |  |

| Note: U = | Unchanged by                        | y Reset. R/W | = Read/Write | ).  |     |     |     |     |  |  |

ADC CAL—Analog-to-Digital Converter Calibration Values

Contains factory calibrated values for ADC gain and offset compensation. Each of the ten supported modes has one byte of offset calibration and two bytes of gain calibration. These values are read by the software to compensate ADC measurements as detailed in

Software Compensation Procedure on page 122. The location of each calibration byte is provided in Table 93 on page 148.

| Info Page | Memory  | Compensation   |                         | Reference      |

|-----------|---------|----------------|-------------------------|----------------|

| Address   | Address | Usage          | ADC Mode                | Туре           |

| 60        | FE60    | Offset         | Single-Ended Unbuffered | Internal 2.0 V |

| 08        | FE08    | Gain High Byte | Single-Ended Unbuffered | Internal 2.0 V |

| 09        | FE09    | Gain Low Byte  | Single-Ended Unbuffered | Internal 2.0 V |

| 63        | FE63    | Offset         | Single-Ended Unbuffered | Internal 1.0 V |

| 0A        | FE0A    | Gain High Byte | Single-Ended Unbuffered | Internal 1.0 V |

| 0B        | FE0B    | Gain Low Byte  | Single-Ended Unbuffered | Internal 1.0 V |

| 66        | FE66    | Offset         | Single-Ended Unbuffered | External 2.0 V |

| 0C        | FE0C    | Gain High Byte | Single-Ended Unbuffered | External 2.0 V |

| 0D        | FE0D    | Gain Low Byte  | Single-Ended Unbuffered | External 2.0 V |

### Table 93. ADC Calibration Data Location

# **Serialization Data**

## Table 94. Serial Number at 001C-001F (S\_NUM)

| BITS      | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 6            | 5            | 4 | 3 | 2 | 1 | 0 |  |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------------|---|---|---|---|---|--|--|

| FIELD     | S_NUM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |              |              |   |   |   |   |   |  |  |

| RESET     | U U U U U U U U                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |              |              |   |   |   |   |   |  |  |

| R/W       | R/W         R/W |              |              |   |   |   |   |   |  |  |

| ADDR      | Information Page Memory 001C-001F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |              |              |   |   |   |   |   |  |  |

| Note: U = | Unchanged b                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | y Reset. R/W | = Read/Write |   |   |   |   |   |  |  |

S NUM— Serial Number Byte

The serial number is a unique four-byte binary value.

point, the PA0/DBG pin can be used to autobaud and cause the device to enter DEBUG mode. For more details, see OCD Unlock Sequence (8-Pin Devices Only) on page 156.

#### Exiting DEBUG Mode

The device exits DEBUG mode following any of these operations:

- Clearing the DBGMODE bit in the OCD Control Register to 0

- Power-On Reset

- Voltage Brownout reset

- Watchdog Timer reset

- Asserting the  $\overline{\text{RESET}}$  pin Low to initiate a Reset

- Driving the DBG pin Low while the device is in STOP mode initiates a system reset

## OCD Data Format

The OCD interface uses the asynchronous data format defined for RS-232. Each character is transmitted as 1 Start bit, 8 data bits (least-significant bit first), and 1 Stop bit as displayed in Figure 25.

| STADT | 00 | D1 | 50 | 50 | D4 | DE | D6 | D7 | STOD |

|-------|----|----|----|----|----|----|----|----|------|

| START | DU |    | DZ | 03 | D4 | 05 | DO | Dī | 310F |

#### Figure 25. OCD Data Format

**Note:** When responding to a request for data, the OCD may commence transmitting immediately after receiving the stop bit of an incoming frame. Therefore, when sending the stop bit, the host must not actively drive the DBG pin High for more than 0.5 bit times. It is recommended that, if possible, the host drives the DBG pin using an open-drain output.

# **OCD Auto-Baud Detector/Generator**

To run over a range of baud rates (data bits per second) with various system clock frequencies, the OCD contains an auto-baud detector/generator. After a reset, the OCD is idle until it receives data. The OCD requires that the first character sent from the host is the character 80H. The character 80H has eight continuous bits Low (one Start bit plus 7 data bits), framed between High bits. The auto-baud detector measures this period and sets the OCD baud rate generator accordingly.

The auto-baud detector/generator is clocked by the system clock. The minimum baud rate is the system clock frequency divided by 512. For optimal operation with asynchronous

# **Oscillator Control**

Z8 Encore! XP<sup>®</sup> F0823 Series devices uses three possible clocking schemes, each user-selectable:

- On-chip precision trimmed RC oscillator

- External clock drive

- On-chip low power Watchdog Timer oscillator

In addition, Z8 Encore! XP F0823 Series devices contain clock failure detection and recovery circuitry, allowing continued operation despite a failure of the primary oscillator.

# Operation

This chapter discusses the logic used to select the system clock and handle primary oscillator failures. A description of the specific operation of each oscillator is outlined elsewhere in this document.

# **System Clock Selection**

The oscillator control block selects from the available clocks. Table 101 details each clock source and its usage.

| Clock Source                          | Characteristics                                                                                                                 | Required Setup                                                                                                                                                                                                  |

|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Internal Precision<br>RC Oscillator   | <ul> <li>32.8 kHz or 5.53 MHz</li> <li>± 4% accuracy when trimmed</li> <li>No external components required</li> </ul>           | Unlock and write Oscillator Control<br>Register (OSCCTL) to enable and<br>select oscillator at either 5.53 MHz or<br>32.8 kHz                                                                                   |

| External Clock<br>Drive               | <ul> <li>0 to 20 MHz</li> <li>Accuracy dependent on external clock source</li> </ul>                                            | <ul> <li>Write GPIO registers to configure PB3<br/>pin for external clock function</li> <li>Unlock and write OSCCTL to select<br/>external system clock</li> <li>Apply external clock signal to GPIO</li> </ul> |

| Internal Watchdog<br>Timer Oscillator | <ul> <li>10 kHz nominal</li> <li>± 40% accuracy; no external components required</li> <li>Very Low power consumption</li> </ul> | <ul> <li>Enable WDT if not enabled and wait<br/>until WDT Oscillator is operating.</li> <li>Unlock and write Oscillator Control<br/>Register (OSCCTL) to enable and<br/>select oscillator</li> </ul>            |

Table 101. Oscillator Configuration and Selection

# **Opcode Maps**

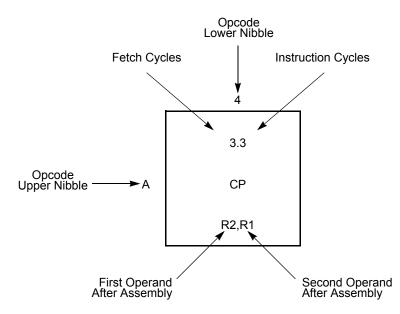

A description of the opcode map data and the abbreviations are provided in Figure 26. Figure 27 and Figure 28 provide information about each of the eZ8 CPU instructions. Table 116 lists Opcode Map abbreviations.

Figure 26. Opcode Map Cell Description

# **Electrical Characteristics**

The data in this chapter is pre-qualification and pre-characterization and is subject to change. Additional electrical characteristics may be found in the individual chapters.

# **Absolute Maximum Ratings**

Stresses greater than those listed in Table 117 may cause permanent damage to the device. These ratings are stress ratings only. Operation of the device at any condition outside those indicated in the operational sections of these specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. For improved reliability, tie unused inputs to one of the supply voltages ( $V_{DD}$  or  $V_{SS}$ ).

| Parameter                                           | Minimum | Maximum | Units | Notes |

|-----------------------------------------------------|---------|---------|-------|-------|

| Ambient temperature under bias                      | -40     | +105    | °C    |       |

| Storage temperature                                 | -65     | +150    | °C    |       |

| Voltage on any pin with respect to V <sub>SS</sub>  | -0.3    | +5.5    | V     | 1     |

|                                                     | -0.3    | +3.9    | V     | 2     |

| Voltage on $V_{DD}$ pin with respect to $V_{SS}$    | -0.3    | +3.6    | V     |       |

| Maximum current on input and/or inactive output pin | -5      | +5      | μA    |       |

| Maximum output current from active output pin       | -25     | +25     | mA    |       |

| 8-pin Packages Maximum Ratings at 0 °C to 70 °C     |         |         |       |       |

| Total power dissipation                             |         | 220     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 60      | mA    |       |

| 20-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 430     | mW    |       |

| Maximum current into $V_{DD}$ or out of $V_{SS}$    |         | 120     | mA    |       |

| 28-pin Packages Maximum Ratings at 0 °C to 70 °C    |         |         |       |       |

| Total power dissipation                             |         | 450     | mW    |       |

#### Table 117. Absolute Maximum Ratings

| 190 |

|-----|

|-----|

|                    |                                                         | $T_A = $                       | = 2.7 V to 3<br>-40 °C to +1<br>s otherwise |            |            |                                                   |

|--------------------|---------------------------------------------------------|--------------------------------|---------------------------------------------|------------|------------|---------------------------------------------------|

| Symbol             | Parameter                                               | ameter Minimum Typical Maximum |                                             | Units      | Conditions |                                                   |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (High Speed) |                                | 5.53                                        |            | MHz        | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Frequency (Low Speed)  |                                | 32.7                                        |            | kHz        | V <sub>DD</sub> = 3.3 V<br>T <sub>A</sub> = 30 °C |

| F <sub>IPO</sub>   | Internal Precision Oscillator<br>Error                  |                                | <u>+</u> 1                                  | <u>+</u> 4 | %          |                                                   |

| T <sub>IPOST</sub> | Internal Precision Oscillator<br>Startup Time           |                                | 3                                           |            | μs         |                                                   |

### Table 121. Internal Precision Oscillator Electrical Characteristics

| Part Number                         | F          |            | /O Lines | nterrupts | 16-Bit Timers<br>w/PWM | 10-Bit A/D Channels | UART with IrDA | Description         |  |

|-------------------------------------|------------|------------|----------|-----------|------------------------|---------------------|----------------|---------------------|--|

| Part                                | Flash      | RAM        | 10 L     | Inter     | 16-Bit T<br>w/PWM      | 10-B                | UAR            | Desc                |  |

| Z8 Encore! XP with 1                |            | , 10-Bit A | Analog   | j-to-D    | igital C               | onve                | erter          |                     |  |

| Standard Temperature: 0 °C to 70 °C |            |            |          |           |                        |                     |                |                     |  |

| Z8F0123PB005SC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |

| Z8F0123QB005SC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |

| Z8F0123SB005SC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |

| Z8F0123SH005SC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |

| Z8F0123HH005SC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |

| Z8F0123PH005SC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |

| Z8F0123SJ005SC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |

| Z8F0123HJ005SC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |

| Z8F0123PJ005SC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |

| Extended Temperatur                 | e: -40 °C  | to 105 °C  | ;        |           |                        |                     |                |                     |  |

| Z8F0123PB005EC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | PDIP 8-pin package  |  |

| Z8F0123QB005EC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | QFN 8-pin package   |  |

| Z8F0123SB005EC                      | 1 KB       | 256 B      | 6        | 12        | 2                      | 4                   | 1              | SOIC 8-pin package  |  |

| Z8F0123SH005EC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SOIC 20-pin package |  |

| Z8F0123HH005EC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | SSOP 20-pin package |  |

| Z8F0123PH005EC                      | 1 KB       | 256 B      | 16       | 18        | 2                      | 7                   | 1              | PDIP 20-pin package |  |

| Z8F0123SJ005EC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SOIC 28-pin package |  |

| Z8F0123HJ005EC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | SSOP 28-pin package |  |

| Z8F0123PJ005EC                      | 1 KB       | 256 B      | 22       | 18        | 2                      | 8                   | 1              | PDIP 28-pin package |  |

| Replace C with G for Lea            | d-Free Pac | kaging     |          |           |                        |                     |                |                     |  |

223