Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                           |

|----------------------------|-----------------------------------------------------------|

| Product Status             | Obsolete                                                  |

| Core Processor             | eZ8                                                       |

| Core Size                  | 8-Bit                                                     |

| Speed                      | 5MHz                                                      |

| Connectivity               | IrDA, UART/USART                                          |

| Peripherals                | Brown-out Detect/Reset, LED, POR, PWM, WDT                |

| Number of I/O              | 6                                                         |

| Program Memory Size        | 8KB (8K x 8)                                              |

| Program Memory Type        | FLASH                                                     |

| EEPROM Size                | -                                                         |

| RAM Size                   | 1K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                               |

| Data Converters            | A/D 4x10b                                                 |

| Oscillator Type            | Internal                                                  |

| Operating Temperature      | -40°C ~ 105°C (TA)                                        |

| Mounting Type              | Surface Mount                                             |

| Package / Case             | 8-SOIC (0.154", 3.90mm Width)                             |

| Supplier Device Package    | -                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/zilog/z8f0823sb005ec |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Revision History**

Each instance in Revision History reafieldans ge to this downut from its previous revision. For more details for the corresponding pages and appropriate links in the table below.

| Date             | Revision<br>Level | Description                                                                                                                                                                                          | Page No         |

|------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| March<br>2008    | 14                | Changed title to Z8 Encore! XP F0823 Series and contents to match the title.                                                                                                                         | <b>têhi</b> e   |

| December<br>2007 | 13                | Updated title from Z8 Encore! 8K and 4K Series t<br>Encore! XP Z8F0823 Series. Updatedgure 3 Table<br>15, Table 35 Table 59throughTable 61, Table 119,<br>and Part Number Suffix Designationsection. | 59, 91,         |

| August<br>2007   | 12                | UpdatedTable 1, Table 16 and Program Memory section.                                                                                                                                                 | 2, 42<br>and 13 |

| June 200         | 7 11              | Updated to combine Z8 Encore! 8K and Z8 Encor Series.                                                                                                                                                | еАИК            |

| December<br>2006 | 10                | UpdatedOrdering Informationhapter.                                                                                                                                                                   | 217             |

|                 | Reset (                                                 | Characteristics and Latency                                         |

|-----------------|---------------------------------------------------------|---------------------------------------------------------------------|

| Reset<br>Type   | Control Registers                                       | eZ8<br>CPU Reset Latency (Delay)                                    |

| System<br>Reset | Reset (as applicable)                                   | Reset 66 InternPrecision Oscillator Cycles                          |

|                 | eUnaffected, except<br>WDT_CTL and OSC_CTL<br>registers | Reset 66 Internal Precision Oscillator Cycles<br>+ IPO startup time |

#### Table 9. Reset and Stop Mode Recovery Characteristics and Latency

During a System Reset or Stop Mode Recovery, the IPOusetquisetart up. Then the Z8 Encore! XP F0823 Series device is **Relset** infor 66 cycles of the Internal Precision Oscillator. If the crystal oscillator is emailable of Iash option bits, this reset period is increased to 5000 IPO cycles. When accerse becorause of a low voltage condition or Power-On Reset, this delangets ured from the time thrate physic voltage for st exceeds the POR level. If the external pin resets recent at the end of the reset period, the device remains inset until the pin is deasserted.

At the beginning of Reset, all GPIO peirconafigured as inputs with pull-up resistor disabled.

During Reset, the eZ8 CPU and on-chip patripheridle; however, the on-chip crystal oscillator and Watchdog Torseillator continue to run.

Upon Reset, control registients involve Register File that have a defined Reset value are loaded with their reset values. Other constants (including the Stack Pointer, Register Pointer, and Flags) and generate RAD are undefined following Reset. The eZ8 CPU fetches the Reset vector at Program Memory 02022 and loads that value into the Program Counterm Peoegcution begins at the Reset vector address.

When the control registers are re-initialized them reset, the system clock after reset is always the IPO. The software must used the goscillator cobtook, such that the correct system clock source is enabled and selected.

#### Reset Sources

Table 10lists the possible sources of a System Reset.

| Operating Mode       | Reset Source                                      | Special Conditions                                                                                            |

|----------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| NORMAL or HALT modes | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                    |

|                      | Watchdog Timer time-out when configured for Reset | None.                                                                                                         |

|                      | RESET pin assertion                               | All reset pulses less than three system clocks i width are ignored.                                           |

|                      | OCD initiated Reset<br>(OCDCTL[0] set to 1)       | System Reset, except the OCD usinaffected by the reset.                                                       |

| STOP mode            | Power-On Reset/Voltage<br>Brownout                | Reset delay begins after supply voltage exceeds POR level.                                                    |

|                      | RESET pin assertion                               | All reset pulses less than the specified analog delay are ignored. Se Electrical Characteristics on page 193. |

|                      | DBG pin driven Low                                | None.                                                                                                         |

Table 10. Reset Sources and Resulting Reset Type

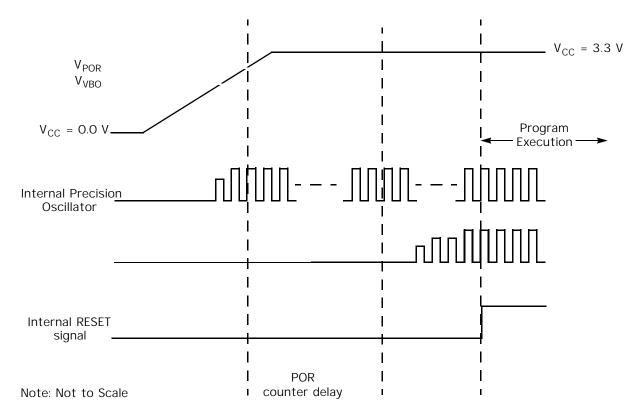

#### Power-On Reset

Each device in the Z8 Encore! XP FO82/3 Semitains an internal POR circuit. The POR circuit monitors the supply voltage dendhe device in the Reset state until the supply voltage reaches a safe operatin Ag the supply voltage exceeds the POR voltage threshold (), the device is held in the transfer the port out it the POR Counter has timed out. If the crystal oscillator is by able option bits, this time-out is longer.

After the Z8 Encore! XP F0823 Series detxictenexPOR state, the eZ8 CPU fetches the Reset vector. Following the POR CR status bit in Watchdog Timer Control (WDTCTL) register is set to 1.

Figure 5displays POR operation: Flore POR threshold voltager Vse Electrical Characteristions page 193.

Figure 5. Power-On Reset Operation

### Voltage Brownout Reset

The devices in the Z8 Encore! XP FO8i23 Second low VBO protection. The VBO circuit senses when the supply voltage dnopssafe level (below the VBO threshold voltage) and forces the device into the alles within the supply voltage remains below the POR voltage threshold (Vthe VBO block holds the device in the Reset.

After the supply voltage again exceeds/the Rocest voltage threshold, the device progresses through a full System Reset seas described in the POR section. Following POR, the POR status bit in the Status (RSTSTAT) register is set to 1. Figure 6 displays Voltage Brownout operation. For the VBO and POR threshold voltages ( $V_{BO}$  and  $V_{OR}$ ), set lectrical Characteristinspage 193.

The VBO circuit can be either enables blediduring STOP mode. Operation during STOP mode is set by the VBO\_AO Flashood bit. For information on configuring VBO\_AO, see Flash Option Bits page 141.

page 49SeeGPIO Alternate Functions page 36 to determine the alternate function associated with each port pin.

Table 21. Port A C Alternate Function Sub-Registers (PxAF)

| BITS  | 7      | 6                                             | 5           | 4            | 3               | 2                    | 1         | 0        |  |  |

|-------|--------|-----------------------------------------------|-------------|--------------|-----------------|----------------------|-----------|----------|--|--|

| FIELD | AF7    | AF6                                           | AF5         | AF4          | AF3             | AF2                  | AF1       | AFO      |  |  |

| RESET |        | OOH (Ports A C); O4H (Port A of 8-pin device) |             |              |                 |                      |           |          |  |  |

| R/W   |        | R/W                                           |             |              |                 |                      |           |          |  |  |

| ADDR  | lf 02H | in Port A (                                   | C Address F | Register, ac | ciessies throug | gh the Po <b>A</b> l | C Control | Register |  |  |

AF[7:0] Port Alternate Function enabled

O = The port pin is in normal mode **DDx the** in the Port A C Data Direction subregister determines the direction of the pin.

1 = The alternate function text through Alternate than Set sub-registers is enabled. Port pin operation is raded by the alternate function.

Port A C Output Control Sub-Registers

The Port A C Output Control sub-register 2(2) is accessed through the Port A C Control register by writting to the Port A C Addressstegi Setting the bits in the Port A C Output Control sub-registers onfigures the specified port pins for opendrain operation. These sub-registers officients dimectly and, as a result, alternate functions are also affected.

| BITS  | 7      | 6                                                               | 5           | 4            | 3               | 2           | 1         | 0        |  |

|-------|--------|-----------------------------------------------------------------|-------------|--------------|-----------------|-------------|-----------|----------|--|

| FIELD | POC7   | POC6                                                            | POC5        | POC4         | POC3            | POC2        | POC1      | POCO     |  |

| RESET | 0      | 0                                                               | 0           | 0            | 0               | 0           | 0         | 0        |  |

| R/W   | R/W    | R/W         R/W         R/W         R/W         R/W         R/W |             |              |                 |             |           |          |  |

| ADDR  | lf 03H | in Port A C                                                     | C Address R | Register, ac | ciessies throug | gh the PoAt | C Control | Register |  |

Table 22. Port A C Output Control Sub-Registers (PxOC)

#### POC[7:0] Port Output Control

These bits function independently **dtenthete** function bit and always disable the drains if set to 1.

**Caution:** Do not enable alternate functions for GPIO port pins for which there is no associated alternate function. Failure to follow this guideline can result in unpredictable operation.

Table 43. IRQ2 Enable and Priority Encoding (Continued)

| IRQ2ENH[ <b>x</b> ] | IRQ2ENL[ <b>x</b> ] | Priority | Description |

|---------------------|---------------------|----------|-------------|

| 1                   | 1                   | Level 3  | High        |

where *x* indicates the register bits from 0 7.

#### Table 44. IRQ2 Enable High Bit Register (IRQ2ENH)

| BITS  | 7        | 6   | 5   | 4   | 3     | 2     | 1     | 0     |

|-------|----------|-----|-----|-----|-------|-------|-------|-------|

| FIELD | Reserved |     |     |     | C3ENH | C2ENH | C1ENH | COENH |

| RESET | 0        | 0   | 0   | 0   | 0     | 0     | 0     | 0     |

| R/W   | R/W      | R/W | R/W | R/W | R/W   | R/W   | R/W   | R/W   |

| ADDR  |          |     |     | FC  | 7H    |       |       |       |

Reserved Must be O

C3ENH Port C3 Interrupt Request Enable High Bit C2ENH Port C2 Interrupt Request Enable High Bit C1ENH Port C1 Interrupt Request Enable High Bit C0ENH Port C0 Interrupt Request Enable High Bit

#### Table 45. IRQ2 Enable Low Bit Register (IRQ2ENL)

| BITS  | 7   | 6    | 5     | 4   | 3     | 2     | 1     | 0        |

|-------|-----|------|-------|-----|-------|-------|-------|----------|

| FIELD |     | Rese | erved |     | C3ENL | C2ENL | C1ENL | COENL    |

| RESET | 0   | 0    | 0     | 0   | 0     | 0     | 0     | 0        |

| R/W   | R/W | R/W  | R/W   | R/W | R/W   | R/W   | R/W   | R/W      |

| ADDR  |     |      |       | FC  | 8H    |       |       | <u>.</u> |

Reserved Must be O

C3ENL Port C3 InterrupRequest Enable Low Bit C2ENL Port C2 InterrupRequest Enable Low Bit C1ENL Port C1 InterrupRequest Enable Low Bit C0ENL Port C0 InterrupRequest Enable Low Bit

### Interrupt Edge Select Register

The Interrupt Edge Sele(IRQES) registeriable 45 determines whether interrupt is generated for the rising edge or falling edges elected GPIO Port A or Port D input pin.

#### COMPARATOR COUNTER Mode

In COMPARATOR COUNTER mode the timer counts inpusitions from the analog comparator output. TIPOL bit in the Timer Control Register selects whether the count occurs on the rising edge or the the temperator output signal. In COMPARATOR COUNTER mode, the prescaler is disabled.

# Caution: The frequency of the comparator output signal must not exceed one-fourth the system clock frequency.

After reaching the Reload value stored in the Reload High and Low Byte registers, the timer generates terring the count value in the High and Low Byte registers is reset **00**01H and counting resumes. Also, Tinthe Output alternate function is enabled, the Timer Output pin chang (from the to High or from High to Low) at timer Reload.

Follow the steps below for config**timeg** for COMPARATOR COUNTER mode and initiating the count:

1. Write to the Timer Control register to:

Disable the timer.

Configure the timer fol//IPORATOR COUNTER mode.

Select either the rising edge or falling the edge comparator output signal for the count. This also sets the initial loggi (High or Low) for the Timer Output alternate function. However, the Timert Ounction is not required to be enabled.

- 2. Write to the Timer High and Low Bystteensegtio set the sptandium tvalue. This action only affects the first pashs/RAR200 COUNTER mode. After the first timer Reload in COMPARATOR COUNTER hode, counting always begins at the reset value 00001H. Generally, in COMPARATORCOUNTER mode the Timer High and Low Byte registers the written with the 00001Ute.

- 3. Write to the Timer Reload High an Byttew registers to set the Reload value.

- 4. If appropriate, enable the timer interruse timer interrupt priority by writing to the relevant interrupt registers.

- 5. If using the Timer Output function, configure the associated GPIO port pin for the Timer Output alternate function.

- 6. Write to the Timer Control register to enable the timer.

In COMPARATOR COUNTER mode, the number of comparator output transitions since the timer start is given by the following equation:

Comparator Output Transitions Current Count Value Start Value

| BITS  | 7   | 6   | 5   | 4     | 3    | 2   | 1   | 0   |

|-------|-----|-----|-----|-------|------|-----|-----|-----|

| FIELD |     |     |     | PW    | 'ML  |     |     |     |

| RESET | 0   | 0   | 0   | 0     | 0    | 0   | 0   | 0   |

| R/W   | R/W | R/W | R/W | R/W   | R/W  | R/W | R/W | R/W |

| ADDR  |     |     |     | FO5H, | FODH |     |     |     |

Table 54. Timer 0 1 PWM Low Byte Register (TxPWML)

PWMH and PWML Pulse-Width Modator High and Low Bytes These two bytes, {PWMH[7:0], PWML[7:0]}, afdrombit value that is compared to the current 16-bit timer count. When a remarks, htbe PWM output changes state. The PWM output value is set by Problebit in the Timer Control Register (TxCTL1) register.

The TxPWMH and TxPWML registers abree she 16-bit captured timer value when operating in CAPTURE or CAPTURE/COMPARE modes.

#### Timer 0 1 Control Registers

#### Time 0 1 Control Register 0

The Timer Control Register O (TxCTLO) and Timer Control Register 1 (TxCTL1) determine the timer operating moster.intclades a programmable PWM deadband delay, two bits to configure the terrupt definition, and tas bit to identify if the most recent timer interrceputsies by an input Capture event.

| Table 55. | limer 0 1 | Control | Register | 0 ( | (IxCILO) |  |

|-----------|-----------|---------|----------|-----|----------|--|

|           |           |         |          |     |          |  |

. \_

| BITS  | 7       | 6    | 5    | 4        | 3    | 2    | 1   | 0      |

|-------|---------|------|------|----------|------|------|-----|--------|

| FIELD | TMODEHI | TICO | NFIG | Reserved |      | PWMD |     | INPCAP |

| RESET | 0       | 0    | 0    | 0        | 0    | 0    | 0   | 0      |

| R/W   | R/W     | R/W  | R/W  | R/W      | R/W  | R/W  | R/W | R/W    |

| ADDR  |         |      |      | FO6H,    | FOEH |      |     |        |

TMODEHI Timer Mode High Bit

This bit along with the TMODE field in LTx Cegister determines the operating mode of the timer. This is the most-significantheitimer mode selection value. See the TxCTL1 register description for more details.

TICONFIG Timer Interrupt Configuration This field configures timer interrupt definition.

#### Receiving Data using the Interrupt-Driven Method

The UART Receiver interruipdicates the availability of new data (as well as error conditions). Follow the steps below two reactives guart receiver for interrupt-driven operation:

- 1. Write to the UART Baud Rate High and ytow registers to set the acceptable baud rate.

- 2. Enable the UART pin functions by configure associated GPIO port pins for alternate function operation.

- 3. Execute DI instruction to disable interrupts.

- 4. Write to the Interrupt control regestates the UART Receiver interrupt and set the acceptable priority.

- 5. Clear the UART Receiver interrupte imapplicable Interrupted register.

- 6. Write to the UART Control 1 Registernable Multiprocessor (9-bit) mode functions, if appropriate.

Set the Multiprocessor Mode States (o Enable MULTIPROCESSOR mode

Set the Multiprocessor  $\mathsf{Mod}\texttt{MBMS}[1:0]$  , to select the acceptable address matching scheme

Configure the UART to interrupt on received data and errors or errors only (interrupt on errors only is unlikeeyukeeful for Z8 Encore! XP devices without a DMA block)

- 7. Write the device address to the Address Compare Register (automatic MULTIPROCESSOR modes only).

- 8. Write to the UART Control O register to:

Set the receive enable RET) (to enable the UART data reception

Enable parity, if appropriate and if **routs** for mode is **emost** bled, and select either even or odd parity

9. Execute an instruction to enable interrupts.

The UART is now configured interrupt-driven date ption. When the UART Receiver interrupt is detected, the consistent pt service inceu(ISR) performs the following:

- 1. Checks the UART Status O registerr**toindete** source of the interrupt error, break, or received data.

- Reads the data from the UART Receive Data register if the interrupt was because of data available. If operating in MULTIPERSOR (9-bit) mode, further actions may be required depending on the MAROCESSOR mode bits MPMD[1:0].

in hardware, software not scombination of the depending on the multiprocessor configuration bits. In general, the addressed feature reduces the load on the CPU, because it does not require access to the UART when it receives data directed to othe devices on the multi-node network lighten for three MULTROCESSOR modes are available in hardware:

Interrupt on all address bytes

Interrupt on matched addressabgiteorrectly framed data bytes

Interrupt only on correctly framed data bytes

These modes are selected MRIMID[1:0] in the UART Control 1 Register. For all multiprocessor modes MIBIE Nof the UART Control 1 Register must be set to 1.

The first scheme is enabled by **wrtting** MPMD[1:0]. In this mode, all incoming address bytes cause an interrupt, **wbyltedatever** cause an interrupt. The interrupt service routine must manually check the laydber that caused triggered the interrupt. If it matches the UART address, the software APMD[0]. Each new incoming byte interrupts the CPU. The software is responsible termining the end of the frame. It checks for the end of the frame by reading MARRX bit of the UART Status 1 Register for each incoming byte MIPRX 1, a new frame has begun. If the address of this new frame is different from the UART s address, MPMD[0] must be set to 1 causing the UART interrupts to go inactive untilexth address byte. If the frame is address matches the UART s, the data in the new frame is processed as well.

The second scheme requires for the wing: set MPMD[1:0]0Bb and write the UART s address into the UART Add Cesss pare register. This demonstroduces additional hardware control, in the time only on frames that match the UART s address. When an incoming address byte dotes match the UART s address s, ignored. All successive data bytes in this frame are also ignered. Matching address byte occurs, an interrupt is issued and further up to now occur on each successive byte. When the first data byte in the frame is reade, when the uART Status 1 Register is asserted. All successive data bytes NEV FRMO. When the next address byte occurs, the hardware compares it to the UART s address is the match, the interrupts continues and the NEW FRMO it is set for the first byteneos the match. The interrupts continues and the next address match.

The third scheme is endable setting MPMD[1:0] the and by writing the UART s address into the UART Address page Register. This mode is identical to the second scheme, except that there are no interded persobytes. The first data byte of each frame remains accompanied NEWFRM ssertion.

Table 78. Flash Code Protection Using the Flash Option Bits

| FWP | Flash Code Protection Description                                                                                                                                                               |

|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0   | Programming and erasing disabled <b>for</b> of Flash Program Memory. In user code programming, Page Erase, and Massrase are all disabled. Mass Erase is available through the On-Chip Debugger. |

| 1   | Programming, Page Erase, and Massarase are enabled for all of Flash<br>Program Memory.                                                                                                          |

Flash Code Protection Using the Flash Controller

At Reset, the Flash Controller locks to program or erasure of the Flash memory. To program or erase the Flash rfiestory, ite the Page Select Register with the target page. Unlock the Flash Cobyrollaking two consecutive writes to the Flash Control register with the TabluersceCH sequentially. The Page Select Register must be rewritten with the pagemereviously stored the two Page Select writes do not match, the controller reverts tostalbecklecthe two writes match, the selected page becomes active. For more detailguse 2.1

After unlocking a specific page, you change that Page Program or Erase. Writing the value 95H causes a Page Erase only if the active page resides in a sector that is not protected. Any other value written to the flash register locks the Flash Controller. Mass Erase is not allowed in the deservic only in the bebug Port.

After unlocking a specific page, you canitad stoowarny byte on that page. After a byte is written, the page remains adjoad lowing for subsequentities to other bytes on the same page. Further writes to the Flash Quisteold acuse the active page to revert to a locked state.

Sector Based Flash Protection

The final protection mechanism is implemented er-sector basis. The Flash memories of Z8 Encore! XP devices are divided introdumentation number of 8 sectors. A sector is 1/8 of the total size of the Flash memory, his leads is smaller than the page size, in which case the sector and page sizes are equal.

The Sector Protect Register controls the pstates to feach Flash sector. This register is shared with the Page Stelgister. It is accessed by v73Hrfgollowed b5yEH to the Flash controller. The next write tchtGoerFlass Register targets the Sector Protect Register.

The Sector Protect Register is initial test, putting each sector into an unprotected state. When a bit in the sector Register is written to 1, the corresponding sector can no longer **beoweitase** by the CPU. External Flash programming through the OCD or via the final shall be made are unaffected. After

Reserved O when read FSTAT Flash Controller Status OOOOOO = Flash Controller locked OOOOO1 = First unlock condimeceived (73H written) OOOO10 = Second unlockmoond received (8CH written) OOOO11 = Flash Controller unlocked OOO100 = Sector protect register selected OO1xxx = Program operation in progress O10xxx = Page erase operation in progress 100xxx = Mass eraserotion in progress

#### Flash Page Select Register

The Flash Page Select (FPS) register shares address space with the Flash Sector Prote Register. Unless the Flash comtisolum locked and writtens to this address target the Flash Page Select Register.

The register is used to select one **gdfttane**aidable Flash memory pages to be programmed or erased. Each Flash Page contractions of Flash memory. During a Page Erase operation, all Flash memory having sector with the most significant 7-bits given by FPS[6:0] are chosen for program/erase operation.

| BITS  | 7       | 6    | 5   | 4   | 3   | 2   | 1   | 0   |

|-------|---------|------|-----|-----|-----|-----|-----|-----|

| FIELD | INFO_EN | PAGE |     |     |     |     |     |     |

| RESET | 0       | 0    | 0   | 0   | 0   | 0   | 0   | 0   |

| R/W   | R/W     | R/W  | R/W | R/W | R/W | R/W | R/W | R/W |

| ADDR  | FF9H    |      |     |     |     |     |     |     |

Table 81. Flash Page Select Register (FPS)

INFO\_EN Information Area Enable

0 = Information Area us not selected

1 = Information Area is selected. The **atifor** marked is mapped into the Program Memory address space at add **FESCOLS** throug **FFFH**.

#### PAGE Page Select

This 7-bit field identifies the Flash mpager for Page Erase and page unlocking. Program Memory Address[15:9] = PAGE**[6rO]** he Z8F04x3 devices, the upper 4 bits must always be 0. For the Z8F02x3 devices, the upper 5 bits must always be 0. For the Z8F01x3 devices, the upper 6 bits must always be 0.

A reset and stop function becarchieved by writing to this register. A reset and go function can be achieved by writing this register. If the device is in DEBUG mode, a run function can be implemented by 400 Hitting this register.

Table 99. OCD Control Register (OCDCTL)

| BITS  | 7       | 6     | 5      | 4        | 3 | 2   | 1 | 0   |

|-------|---------|-------|--------|----------|---|-----|---|-----|

| FIELD | DBGMODE | BRKEN | DBGACK | Reserved |   | RST |   |     |

| RESET | 0       | 0     | 0      | 0        | 0 | 0   | 0 | 0   |

| R/W   | R/W     | R/W   | R/W    | R        | R | R   | R | R/W |

DBGMODE DEBUG Mode

The device enters DEBUG mode when it this 1b When in DEBUG mode, the eZ8 CPU stops fetching new instructions this bit causes the eZ8 CPU to restart. This bit is automatically set where Kainstruction is decoded arrade provints are enabled. If the Flash Read Protect Option Bit is enails and than only be cleared by resetting the device. It cannot be written to 0.

0 = Z8 Encore! XP F0823 Series device is operating in NORMAL mode

1 = Z8 Encore! XP F0823 Series device is in DEBUG mode

#### BRKEN Breakpoint Enable

This bit controls the behavior BRK timestruction (opcoold). By default, breakpoints are disabled and BRK instruction behaves similar NOP instruction. If this bit is 1, when BRK instruction is decoded BGM OD bit of the OCDCTL register is automatically set to 1.

- 0 = Breakpoints are disabled

- 1 = Breakpoints are enabled

#### DBGACK Debug Acknowledge

This bit enables the debug acknowledge life this react is set to 1, the OCD sends a Debug Acknowledge chara (Fight) (to the host when a Breakpoint occurs.

- 0 = Debug Acknowledge is disabled

- 1 = Debug Acknowledge is enabled

Reserved O when read

#### RST Reset

Setting this bit to 1 reset & ROD4xA family view. The device ess through a normal Power-On Reset sequence weitex deption that the OCDtises et. This bit is automatically cleared to 0 at the end of reset.

O = No effect

1 = Reset the Flash Read Protect Option Bit device

| Notation | Description                    | Operand | Range                                                                                                                      |

|----------|--------------------------------|---------|----------------------------------------------------------------------------------------------------------------------------|

| b        | Bit                            | b       | b represents a value from 0 to 7 (000B to 111B).                                                                           |

| СС       | Condition Code                 |         | See Condition Codes overview in the eZ8 CPU User Manual.                                                                   |

| DA       | Direct Address                 | Addrs   | Addrs represents a number in the range of 0000H to FFFFH.                                                                  |

| ER       | Extended Addressing Register   | Reg     | Reg repressits a number in the range of OOOH to FFFH.                                                                      |

| IM       | Immediate Data                 | #Data   | Data is a number between OOH to FFH.                                                                                       |

| lr       | Indirect Working Register      | @Rn     | n = 0 15.                                                                                                                  |

| IR       | Indirect Register              | @Reg    | Reg. representa number in the range of OOH to FFH.                                                                         |

| Irr      | Indirect Working Register Pair | @RRp    | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                          |

| IRR      | Indirect Register Pair         | @Reg    | Reg represents an even number in the range OOH to FEH                                                                      |

| р        | Polarity                       | р       | Polarity is a single bit binary value of either OB or 1B.                                                                  |

| r        | Working Register               | Rn      | n = 0 15.                                                                                                                  |

| R        | Register                       | Reg     | Reg. represents a number in the range of OOH to FFH.                                                                       |

| RA       | Relative Address               | Х       | X represents an index in the range of +127 to<br>128 which is an offset relative to the address of<br>the next instruction |

| rr       | Working Register Pair          | RRp     | p = 0, 2, 4, 6, 8, 10, 12, or 14.                                                                                          |

| RR       | Register Pair                  | Reg     | Reg. represents an even number in the range of OOH to FEH.                                                                 |

| Vector   | Vector Address                 | Vector  | Vector represents a number in the range of OOH to FFH.                                                                     |

| X        | Indexed                        | #Index  | The register or regestpair to be indexed is offset<br>by the signed Index value (#Index) in a +127 to<br>-128 range.       |

#### Table 105. Notational Shorthand

227

Index

#### Symbols

# 174 % 174 @ 174

Numerics

10-bit ADC 4binary n40-lead plastic dual-inline package 214, 215BIT 176bit 172

## A

absolute maximum ratings 193 AC characteristics 197 ADC 175 architecture 117 automatic power-down 118 block diagram 118 continuous conversion 120 control register 122, 124 control register definitions 122 data high byte register 124 data low bits register 125 electrical characteristics and timing 201 operation 118 single-shot conversion 119 ADCCTL register 122, 124 ADCDH register 124 ADCDL register 125 ADCX 175 ADD 175 add - extended addressing 175 add with carry 175 add with carry - extended addressing 175 additional symbols 174 address space 13 ADDX 175 analog signals 10 analog-to-digital converter (ADC) 117 AND 177

ANDX 177 arithmetic instructions 175 assembly language programming 171 assembly language syntax 172

## В

B 174 b 173 baud rate generator, UART 103 **BCLR 176** binary number suffix 174 bit 173 clear 176 manipulation instructions 176 set 176 set or clear 176 swap 176 test and jump 178 test and jump if non-zero 178 test and jump if zero 178 bit jump and test if non-zero 178 bit swap 178 block diagram 3 block transfer instructions 176 BRK 178 **BSET 176** BSWAP 176, 178 BTJ 178 BTJNZ 178 **BTJZ 178**

## С

CALL procedure 178 CAPTURE mode 84, 85 CAPTURE/COMPARE mode 85 cc 173 CCF 176 characteristics, electrical 193 clear 177 CLR 177 COM 177